## UNIVERSITY AT STONY BROOK

CEAS Technical Report 757

Cost Efficient Processor Arrangement in Single Level Tree Networks

S. Charcranoon, T.G. Robertazzi and S. Luryi

# Cost Efficient Processor Arrangement in Single Level Tree Networks

Saravut Charcranoon, Student Member, IEEE

Thomas G. Robertazzi, Senior Member, IEEE

Serge Luryi, Fellow, IEEE

Department of Electrical Engineering,

University at Stony Brook,

Stony Brook, NY 11794

Phone: (516) 632-8400

Fax: (516) 632-8494

March 8, 1998

#### Abstract

A study of the optimal placement of processors in a single level tree network processing a divisible load is presented. A set of conditions indicating when the current processor arrangement profile can be improved in terms of total processing cost is obtained. A heuristic algorithm based on a local search is developed from these conditions. The experimental results show an impressive quality of the solution both in effectiveness and in proximity of suboptimal solutions to an optimal solution. The efficiency of the algorithm in terms of the average number of processor arrangement profiles to be searched before a final solution is reached can be bounded by a low order polynomial in the number of children processors as  $O(N^{1.6})$  for up to 19 processors. Several special cases of the model are considered. This work demonstrates the feasibility of cost accounting for future computer utilities.

**Keywords** Single-level tree network, divisible load sharing, processor arrangement, heuristic algorithm, local search, cost, computer utility.

# 1 Introduction

There is growing interest in networked distributed computing systems. This is evident from many new system technology developments as well as experiments on such systems. Among these are the widespread use of the Internet and intranets, the new development of portable and interoperable network software such as JAVA, CORBA, and the successful solution of cryptographic problems via distributed computing system. These factors naturally lead to the introduction of "computer utilities" in the near future. This concept introduces "resource utilization cost" into the problem of control and management in distributed computing systems. By including the resource utilization cost into such problems, the new problem setting requires not only system performance but also the corresponding incurred cost to be considered. One of the fundamental and interesting questions is how to arrange processors in a network topology such that the "total processing cost" incurred from utilizing network resources is minimized while the quality of service is at an accepatable level.

In scheduling in network-wide environments both computational time and communication time need to be considered together. Parallelism in the computational load is another important aspect to be taken into account in order to realize the full capability of a distributed computing system. There is a significant class of loads which explicitly possess data parallelism. This is the class of divisible loads where load can be divided into arbitrary fractions and each fraction of load can be processed in parallel by different processors in the network. Example of divisible loads include the processing of large linear data files as in image processing, signal processing, massive computational or experimental data processing, some massive simulation programs, and cryptography.

So far there have been a number of works on divisible load sharing [1, 2, 3, 4, 5, 6]. All these works attempt to minimize the finish time based on the premise that every active processor stop computing at the same time. However there are only a few works [7, 8] which study the resource utilization problem in the context of divisible load theory. In [8], the authors present a study of optimizing computing cost in a bus network. Therein they provide a criteria to determine a sequence of load distribution that yields the minimum total computing cost. In [7], the authors generalize the previous work [8] to include both link transmission cost and processor cost in a single-level tree network. They find that it is not possible to derive a simple optimal

condition. Instead a set of conditions indicating when a sequence can be improved in total processing cost was obtained. In both works, however, it was a logical interchange of an adjacent link-processor pairs that was used as the primitive operation to find the best sequence of load distribution in terms of the total processing cost. In this paper, on the other hand, it is an architectural rearrangement, a reformation of processor-link pairs in a single level tree network, through a physical interchange of pairs of processors that is used as the basic operation to achieve a minimum total processing cost in a single-level tree network with both link cost and processor cost. In a processor arrangement problem the sequence of load distribution to each link is fixed throughout the course of processor arrangement procedure. The problem is which of N processors to connect to which of N links in a one to one manner.

In this work there are two objective functions to be optimized: the finish time and the total processing cost. It is well known that there are several approaches to solve multiple-objective functions optimization problems. The approach taken here is to find the minimal cost processor arrangement profile given that for any profile, finish time is minimized using the methodology of [3]. That is, for each arrangement profile considered, load is allocated so

that all processors stop computing at the same time instant and finish time is thus minimized for each specific profile. While other approaches are certainly possibly, we believe that the proposed approach is a natural one.

The goal of this paper is to present an analysis of processor arrangement in a single-level tree network where the processors are equipped with frontend processors. We optimize the network arrangement in terms of cost and finish time using adjacent processor pairwise swapping and a load distribution principle, both of which are described below. This analysis is developed to derive the necessary conditions for an improvement in total processing cost. A heuristic algorithm to search for a cost-efficient processor arrangement in an effective and efficient maner is then developed. It is based upon a local search with a multi-level neighborhood structure and multiple initial solutions as its central parts. The corresponding performance is also assessed and discussed.

The paper is organized as follows. The model and concept are presented in section 2. In section 3, processor arrangement and cost optimization are discussed. Cost efficient processor arrangements and the necessary cost improvement conditions in a general single-level tree network are developed in section 4. Section 5 presents the optimal conditions to obtain the minimum

total processing cost processor arrangements in a bus and related networks. Remarks on the analysis of the previous two sections are given in section 6. The heuristic cost efficient processor arrangement algorithm and its performance evaluation are developed and discussed in section 7 and 8. Finally the conclusion appears in section 9.

# 2 Models and Notations

# 2.1 Models Descriptions

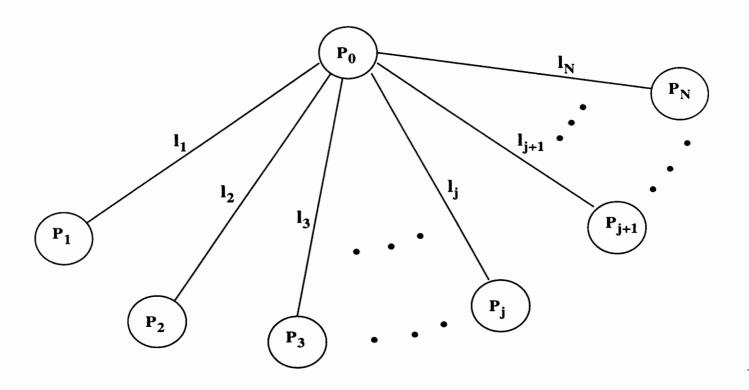

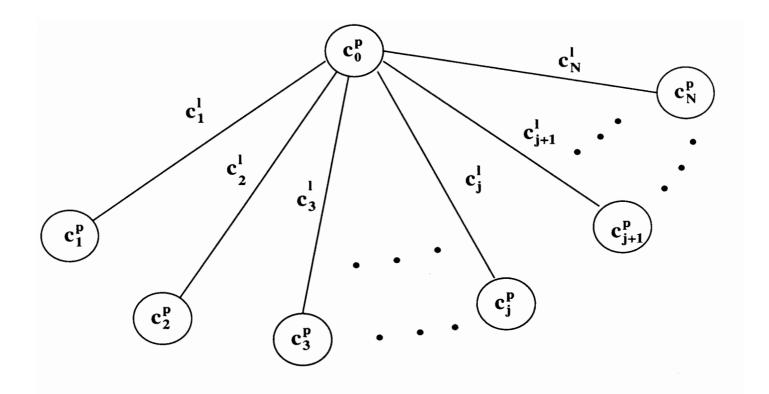

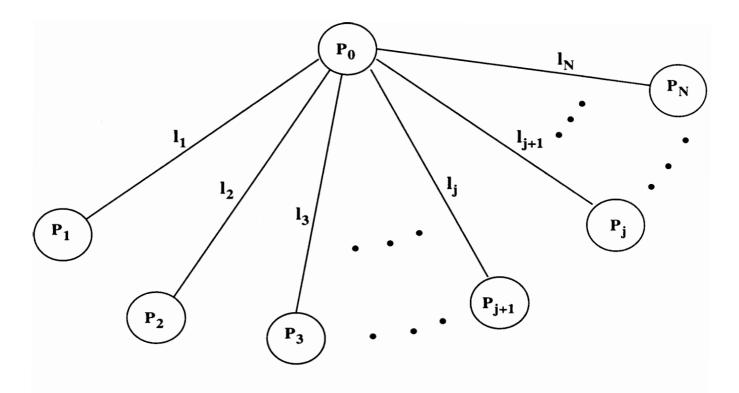

In this paper, a single-level tree network where the root processor is equipped with a front-end processor is considered. A single-level tree network with (N+1) processors and (N) links is shown in Figure 1. All the processors are connected to the root processor,  $p_0$ , via communication links. That is the children processors  $p_1,..., p_N$  are connected to the root processor  $p_0$  via links  $l_1, l_2,..., l_N$ . Associated with the links and processors are the associated cost coefficients  $c_1^l, c_2^l,..., c_N^l$  and  $c_0^p, c_1^p, c_2^p,..., c_N^p$ , respectively as depicted in Figure 2. The root processor, assumed to be the only processor at which the load arrives, partitions the total processing load into (N+1) fractions,

keeps its own fraction  $\alpha_0$ , and distributes the other fractions  $\alpha_1$ ,  $\alpha_2$ ,...,  $\alpha_N$  to the children processors  $p_1$ ,  $p_2$ ,...,  $p_N$  respectively and sequentially. Each processor begins computing immediately after receiving its assigned fraction of load and continues without any interruption until all of its assigned load fraction has been processed. We do not consider multi-installment strategies as in [3].

For clarity, a sequence of load distribution from the root processor to the children processors in a single-level tree network is represented by an ordered set as below,

$$\pi = \{p_0, (l_1, p_1), (l_2, p_2), ..., (l_j, p_j), ..., (l_N, p_N)\}$$

where  $(l_j, p_j)$  represents the  $j^{th}$  processor  $(p_j)$  connected to the root processor  $(p_0)$  via the  $j^{th}$  link  $(l_j)$ .

This ordered set represents a sequence in which the root processor distributes load to the children processors (from  $p_0$  to  $p_1, p_2, ..., p_N$ ). Without loss of generality, it is assumed that a sequence of load distribution is from left to right.

#### 2.2 Notations

Let

$\alpha_i$ : The load fraction assigned to the  $i^{th}$  link-processor pair.

$w_i$ : The inverse of the computing speed of the  $i^{th}$  processor.

$z_i$ : The inverse of the link speed of the  $i^{th}$  link in the single level tree network.

$T_{cp}$ : Time taken to process an entire load by a standard processor,  $w_{standard} = 1$ .

$T_{cm}$ : Time taken to communicate an entire load by a standard link,  $z_{standard} = 1$ .

$T_f$ : The finish time of an entire load, assuming that the load is delivered to the origination processor at time zero. Here the "finish time" is the time when the last processor ceases computation.

# 2.3 Optimal Finish Time Load Distribution

An equal division of load among processors does not in general give a minimum processing finish time even in a homogeneous network [3]. Instead, it is intuitive that to minimize the processing finish time the cost efficient load distribution should be such that all processors finish computing at the same time. In other words, cost efficient load distribution should not allow

any processor to finish its computation and then remain idle while other processors are still busy with their computations. Otherwise the processing finish time could be reduced by transferring some fractions of load from the busy processors to the idle processors. Formal proofs of this argument in the case of linear, bus, and tree networks appear in [3]. However, under certain sets of network parameters, in order to minimize the processing finish time, it is not necessary that all processors have to be utilized. In [3] conditions are found which determine which processors should be used to process the arriving load in the case of a single-level tree network. Still, the processors with non-zero assigned load have to finish computing at the same time. In this paper, it is assumed that all processors in the network are utilized.

Hence, throughout this paper, all processors are required to participate in load processing and they stop computing at the same time instant. Based on this assumption, the recursive equations for a single-level tree network are derived below. This is done by equating the finish times of all of the processors.

# 2.4 Fundamental Recusive Equations and Timing Diagram

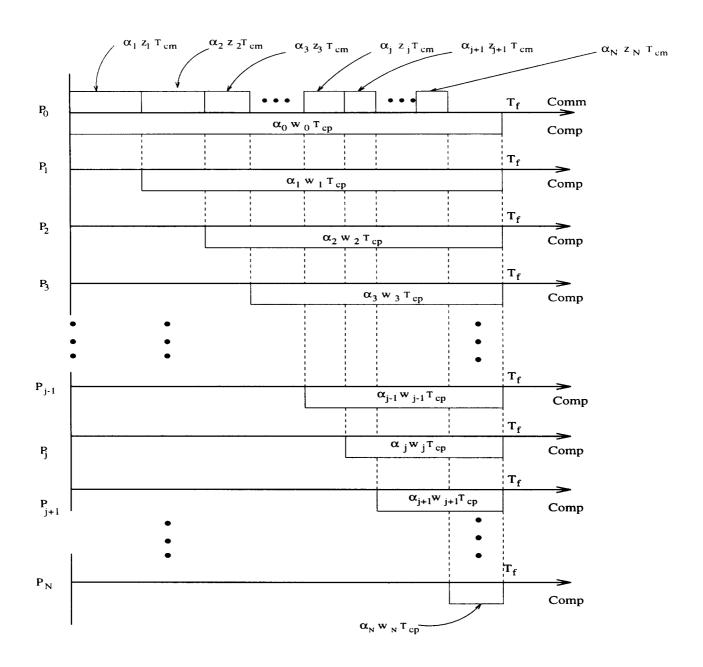

The timing diagram of a single level tree network is given by Figure 3.

From the timing diagram, one can derive fundamental recursive equation as

$$\alpha_i w_i T_{cp} = \alpha_{i+1} z_{i+1} T_{cm} + \alpha_{i+1} w_{i+1} T_{cp} , i = 0, ..., N-1$$

(1)

They can be written in another form as,

$$\alpha_{i+1} = k_i \alpha_i = (\prod_{j=0}^i k_j) \alpha_0 \quad i = 0, ..., N-1$$

(2)

where

$$k_{i} = \frac{\alpha_{i+1}}{\alpha_{i}}$$

$$= \frac{w_{i}T_{cp}}{z_{i+1}T_{cm} + w_{i+1}T_{cp}} \qquad i = 0, ..., N-1$$

(3)

(4)

Clearly, from Eq.(1) and (2), there are N equations and (N+1) unknowns.

An additional equation, the normalization equation, is needed to solve this system of equations. The normalization equation is given as,

$$\alpha_0 + \alpha_1 + \dots + \alpha_N = 1 \tag{5}$$

$$\sum_{i=0}^{N} \alpha_i = 1 \tag{6}$$

With the normalization equation, one can then resolve the recursive equations (1) to obtain the closed-form expression of  $\alpha_0$ , the fraction of load of the root processor. Once  $\alpha_0$  is known, the other processor load fractions can be obtained by substituting  $\alpha_0$  into Eq.(2) and solving them recursively as shown below.

$$\alpha_0 = \left[1 + \sum_{i=1}^{N} \left[ \prod_{j=0}^{i-1} k_j \right] \right]^{-1} \tag{7}$$

$$= [1 + k_0 + k_0 k_1 + \dots + k_0 k_1 \cdots k_{N-1}]^{-1}$$

(8)

$$= \left[1 + \frac{w_0 T_{cp}}{(z_1 T_{cm} + w_1 T_{cp})} + \dots + \frac{\prod_{i=0}^{N-1} (w_i T_{cp})}{\prod_{i=1}^{N} (z_i T_{cm} + w_i T_{cp})}\right]^{-1}$$

(9)

$$= \frac{1}{D} \prod_{i=1}^{N} (z_i T_{cm} + w_i T_{cp}) \tag{10}$$

$$\alpha_1 = k_0 \alpha_0$$

$$= \frac{w_0 T_{cp}}{(z_1 T_{cm} + w_1 T_{cp})} \frac{1}{D} \prod_{i=1}^{N} (z_i T_{cm} + w_i T_{cp})$$

$$= \frac{1}{D} (w_0 T_{cp}) \prod_{i=2}^{N} (z_i T_{cm} + w_i T_{cp})$$

(11)

$$\alpha_2 = k_1 \alpha_1$$

$$= \frac{w_1 T_{cp}}{(z_2 T_{cm} + w_2 T_{cp})} (w_0 T_{cp}) \frac{1}{D} \prod_{i=2}^{N} (z_i T_{cm} + w_i T_{cp})$$

$$= \frac{1}{D} (w_0 T_{cp}) (w_1 T_{cp}) \prod_{i=2}^{N} (z_i T_{cm} + w_i T_{cp})$$

:

$$\alpha_n = k_{n-1}\alpha_{n-1}$$

$$= \frac{1}{D} \prod_{i=0}^{n-1} (w_i T_{cp}) \prod_{i=n+1}^{N} (z_i T_{cm} + w_i T_{cp})$$

:

$$\alpha_N = k_{N-1}\alpha_{N-1}$$

$$= \frac{1}{D} \prod_{i=0}^{N-1} (w_i T_{cp})$$

where

$$D = \prod_{i=1}^{N} (z_i T_{cm} + w_i T_{cp}) + \sum_{n=1}^{N} \left( \prod_{i=0}^{n-1} (w_i T_{cp}) \prod_{i=n+1}^{N} (z_i T_{cm} + w_i T_{cp}) \right)$$

$$(12)$$

where:

$$w_0 T_{cp} = \prod_{i=0}^{0} (w_i T_{cp})$$

$$1 = \prod_{i=N+1}^{N} (z_i T_{cm} + w_i T_{cp})$$

# 3 Processor Arrangement and Cost Optimization

## 3.1 Processor Arrangement

Processor arrangement refers to the connection between links and processors in a single-level tree network. Processor arrangement in general involves a permutation of the order of processors to receive fractions of load from the root processor while maintaining the original arrangement of links in a network throughout the course of the processor arrangement. In terms of an ordered set representation of a single-level tree network:

$$\pi = \{p_0, (l_1, p_1), ..., (l_{j-1}, p_{j-1}), (l_j, p_j), (l_{j+1}, p_{j+1}), (l_{j+2}, p_{j+2}), ..., (l_N, p_N)\}$$

A processor arrangement determines which processor is connected to  $l_1$ ,  $l_2$ , ...,  $l_N$ . A processor arrangement does not change the order of dispatching fractions of load from the root processor to links, i.e., an element  $l_j$  associated with each ordered pair is fixed during the course of processor arrangement. That is, the sequence of load distribution from the root processor does not change from the link point of view. This ordered set will be referred to as a processor arrangement profile. Therefore, a processor arrangement is

a mechanism to change from one processor arrangement profile to another processor arrangement profile. In contrast to the sequencing mechanism of [7], a processor arrangement requires a physical change of a link-processor pairs through processor reordering. In this work, a processor arrangement is performed to minimize total processing cost. One important specialization of processor arrangement is an adjacent pairwise swapped processor arrangement which will be discussed later.

#### 3.2 Link-Processor Cost

The link-processor cost for processing a fraction of load at any processor is defined as the cost incurred from utilizing the processor and its corresponding link in order to successfully process the underlying fraction of load. Therefore, the link-processor cost consists of two major parts: the one incurred by communication over the link and the other incurred by the processor. Throughout this paper, we assume that the cost coefficients associated with links and processors are static. They do not change with either the level of load in progress or the time when the job arrives. This cost is defined only in terms of accounting for the duration during which the resource is busy serv-

ing the assigned divisible load. The link-processor cost is thus a monotonic increasing function of the service duration and moreover is a linear, regular and additive function. The processing costs associated with each network topology are as follows. Let:

$w_n$ : the inverse of the computing speed of the  $n^{th}$  processor, with the unit of second per load.

$z_n$ : the inverse of the link speed of the  $n^{th}$  link, with the unit of second per load.

$c_n^p$ : the computing cost per second of utilizing the  $n^{th}$  processor.

$c_n^l$ : the communication cost per second of utilizing the  $n^{th}$  link.

$c_n^p w_n$ : the computing cost per load of utilizing the  $n^{th}$  processor.

$c_n^l z_n$ : the communication cost per load of utilizing the  $n^{th}$  link.

$(c_n^p w_n + c_n^l z_n)$ : the processing cost per load of the  $n^{th}$  link-processor pair.

## 3.3 Total Cost

Total cost is a cost incurred for a network to process an entire load. It is a linear addition of all individual link-processor costs incurred by utilizing individual link-processor pairs. This individual cost depends on the assigned fraction of load, which in turn is determined by a processor arrangement profile (by "profile" is meant a specific arrangement of processors). Therefore, this total cost depends on the processor arrangement profile.

In this subsection, the general form of the total cost in a single-level tree network is developed. Also its simple form, which is a ratio of numerator and denominator, is given. This simple form will facilitate the subsequent analysis.

Define:

$$C_0 = c_0^p w_0 T_{cp} \tag{13}$$

$$C_n = c_n^l z_n T_{cm} + c_n^p w_n T_{cp}$$

,  $n = 1, ..., N$  (14)

Recall that the root processor is the load origination processor. Therefore no communication cost is incurred by the root processor.

Now:

$C_0$ : the cost of processing the entire of load on the root processor.

$C_n$ : the cost of processing the entire of load on the  $n^{th}$  processor.

$\alpha_0 C_0$ : the cost of processing the assigned fraction of load  $(\alpha_0)$  on the root processor.

$\alpha_n C_n$ : the cost of processing the assigned fraction of load  $(\alpha_n)$  on

the  $n^{th}$  processor.

The total cost,  $C_{total}$ , is defined as a summation of the individual processing costs incurred at each link-processor pair. That is:

$$C_{total} = \alpha_0 C_0 + \sum_{n=1}^{N} \alpha_n C_n \tag{15}$$

$$= \alpha_0(c_0^p w_0 T_{cp}) + \sum_{n=1}^N \alpha_n \left( c_n^l z_n T_{cm} + c_n^p w_n T_{cp} \right)$$

(16)

Note that in the following, in terms of notation the product signs do not distribute over other product signs.

Now, by substituting  $\alpha_0$  and all  $\alpha_n$  from the previous section into equation (16) one obtains:

$$C_{total} = \frac{1}{D} \left\{ \prod_{i=1}^{N} (z_i T_{cm} + w_i T_{cp}) (c_0^p w_0 T_{cp}) + \sum_{n=1}^{N} \left[ \prod_{i=0}^{n-1} (w_i T_{cp}) \right] \cdot \prod_{i=n+1}^{N} (z_i T_{cm} + w_i T_{cp}) (c_n^l z_n T_{cm} + c_n^p w_n T_{cp}) \right\}$$

$$(17)$$

One can also express the total cost while explicitly showing the processing cost incurred by the  $j^{th}$  and the  $(j+1)^{st}$  link-processor pairs as:

$$C_{total} = \frac{1}{D} \left\{ \prod_{i=1}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{0}^{p}w_{0}T_{cp}) + \sum_{n=1}^{j-1} \left[ \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{n}^{l}z_{n}T_{cm} + c_{n}^{p}w_{n}T_{cp}) \right] + \prod_{i=0}^{j-1} (w_{i}T_{cp}) \prod_{i=j+1}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{j}^{l}z_{j}T_{cm} + c_{j}^{p}w_{j}T_{cp}) + \prod_{i=0}^{j} (w_{i}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{j+1}^{l}z_{j+1}T_{cm} + c_{j+1}^{p}w_{j+1}T_{cp}) + \sum_{n=j+2}^{N} \left[ \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{n}^{l}z_{n}T_{cm} + c_{n}^{p}w_{n}T_{cp}) \right] \right\}$$

$$(18)$$

Since the total cost can be put in a simple form as:

$$C_{total} = \frac{N}{D} \tag{19}$$

Thus, the corresponding numerator, N, is:

$$N = \prod_{i=1}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{0}^{p}w_{0}T_{cp})$$

$$+ \sum_{n=1}^{j-1} \left[ \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{n}^{l}z_{n}T_{cm} + c_{n}^{p}w_{n}T_{cp}) \right]$$

$$+ \prod_{i=0}^{j-1} (w_{i}T_{cp}) \prod_{i=j+1}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{j}^{l}z_{j}T_{cm} + c_{j}^{p}w_{j}T_{cp})$$

$$+ \prod_{i=0}^{j} (w_{i}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{j+1}^{l}z_{j+1}T_{cm} + c_{j+1}^{p}w_{j+1}T_{cp})$$

$$+ \sum_{n=j+2}^{N} \left[ \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{n}^{l}z_{n}T_{cm} + c_{n}^{p}w_{n}T_{cp}) \right] (20)$$

(21)

Again, with the terms due to the  $j^{th}$  and the  $(j + 1)^{st}$  link-processor explicitly shown, one has

$$D = \prod_{i=1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j}T_{cm} + w_{j}T_{cp})(z_{j+1}T_{cm} + w_{j+1}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \sum_{n=1}^{j-1} \left( \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j}T_{cm} + w_{j}T_{cp})(z_{j+1}T_{cm} + w_{j+1}T_{cp}) \right)$$

$$\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \prod_{i=0}^{j-2} (w_{i}T_{cp})(w_{j-1}T_{cp})(z_{j+1}T_{cm} + w_{j+1}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \prod_{i=0}^{j-2} (w_{i}T_{cp})(w_{j-1}T_{cp})(w_{j}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \sum_{n=j+2}^{N} \left( \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{N} (z_{i}T_{cm} + w_{i}T_{cp}) \right)$$

$$(22)$$

This rational form of a numerator and a denominator of the total computing cost is useful in the subsequent analysis.

# 3.4 Cost Optimization

There are actually two optimization criteria involved in the problem considered in this paper. One is the above total cost and the second is finish

time. Generally, both should be minimized as much as possible. In this paper we choose to minimize total cost over all possible processor arrangements with finish time being minimized for the *given* processor arrangement chosen. While this is a natural and simple approach for this problem, other approaches to such dual optimization criteria problems are certainly possible.

# 3.5 Adjacent Pairwise Processor Swapping

#### 3.5.1 Concepts and Notations

Adjacent pairwise processor swapping refers to a physical interchange of two processors in an adjacent link-processor pair of the current processor arrangement profile, keeping all other link-processor pairs in their respective positions.

Consider a processor arrangement profile called the "current" processor arrangement profile as shown in Figure 1. A swapped processor arrangement profile is a profile obtained by implementing a single adjacent pairwise processor swap of one of the adjacent link-processor pairs of the current profile as shown in Figure 4, a swap of  $p_j$  and  $p_{j+1}$ .

Here the term "current" profile is used with a view towards the algorithm

developed later.

In the ordered set representation, a current profile and an associated swapped profile can be expressed respectively as,

$$\pi = \{p_0, (l_1, p_1), ..., (l_{j-1}, p_{j-1}), (l_j, p_j), (l_{j+1}, p_{j+1}), (l_{j+2}, p_{j+2}), ..., (l_N, p_N)\}$$

$$\pi' \ = \ \{p_0, (l_1, p_1), ..., (l_{j-1}, p_{j-1}), \underbrace{(l_j, p_{j+1}), \underbrace{(l_{j+1}, p_j)}, (l_{j+2}, p_{j+2}), ..., (l_N, p_N)}\}$$

#### 3.5.2 Recursive Equations

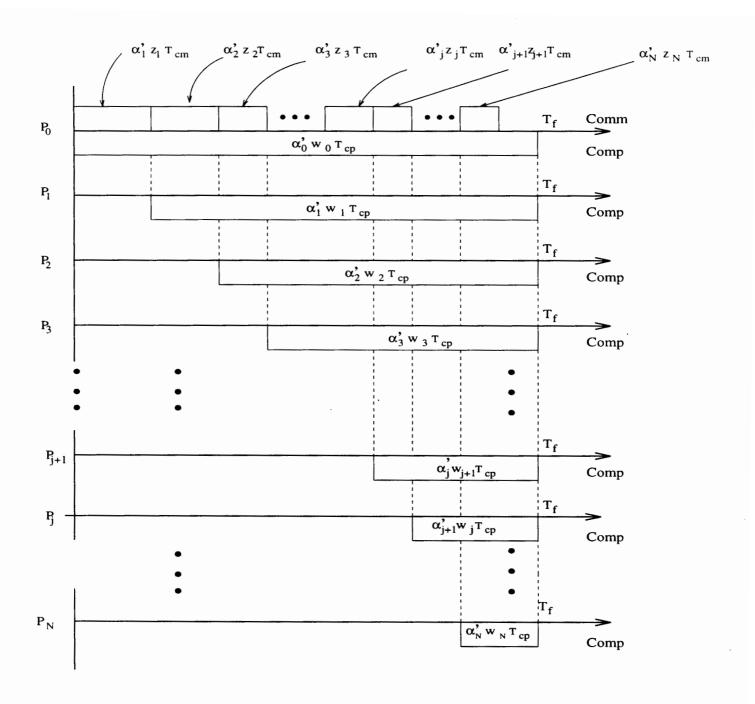

As in section 2.4, we can derive a closed-form solution of the load fraction of each link-processor pair under an adjacent pairwise processor swapped arrangement  $\pi'$  (cf. Figure 5) as follow.

The set of general recursive equations of an adjacent pairwise processor swapped arrangement analogous to equation (1) and equation (2) is given as,

$$\alpha_i' w_i' T_{cp} = \alpha_{i+1}' z_{i+1}' T_{cm} + \alpha_{i+1}' w_{i+1}' T_{cp} \quad i = 0, ..., N-1$$

(23)

$$\alpha'_{i+1} = k'_i \alpha'_i \tag{24}$$

Here, a mapping of  $w'_i$  to  $w_i$  of the original processor arrangement is given as follows

$$w_j' = w_{j+1}$$

$$w'_{j+1} = w_j$$

$$w_k' = w_k, \quad \forall k \neq j, j+1$$

One then has the following series of equations

$$\alpha_0'w_0T_{cp} = \alpha_1'z_1T_{cm} + \alpha_1'w_1T_{cp}$$

$$\alpha_1' = \left(\frac{w_0T_{cp}}{z_1T_{cm} + w_1T_{cp}}\right)\alpha_0'$$

:

$$\alpha'_{j-1}w_{j-1}T_{cp} = \alpha'_{j}z_{j}T_{cm} + \alpha'_{j}w_{j+1}T_{cp}$$

$$\alpha'_{j} = \left(\frac{w_{j-1}T_{cp}}{z_{j}T_{cm} + w_{j+1}T_{cp}}\right)\alpha'_{j-1}$$

$$\alpha'_{j}w_{j+1}T_{cp} = \alpha'_{j+1}z_{j+1}T_{cm} + \alpha'_{j+1}w_{j}T_{cp}$$

$$\alpha'_{j+1} = \left(\frac{w_{j+1}T_{cp}}{z_{j+1}T_{cm} + w_{j}T_{cp}}\right)\alpha'_{j}$$

$$\alpha'_{j+1}w_{j}T_{cp} = \alpha'_{j+2}z_{j+2}T_{cm} + \alpha'_{j+2}w_{j+2}T_{cp}$$

$$\alpha'_{j+2} = \left(\frac{w_{j}T_{cp}}{z_{j+2}T_{cm} + w_{j+2}T_{cp}}\right)\alpha'_{j+1}$$

:

$$\alpha'_{N-1}w_{N-1}T_{cp} = \alpha'_N z_N T_{cm} + \alpha'_N w_N T_{cp}$$

$$\alpha'_N = \left(\frac{w_{N-1}T_{cp}}{z_N T_{cm} + w_N T_{cp}}\right) \alpha'_{N-1}$$

Again incorporating the normalization equation, one solves the above system of (N+1) equations and (N+1) unknowns to obtain an expression for  $\alpha'_0$ . Once  $\alpha'_0$  known, by recursively substituting  $\alpha'_0$  into the other equations, then all other  $\alpha'_n$  will be obtained as below.

That is

$$\alpha_0' = \frac{1}{D_{\pi'}} \prod_{i=1}^{N} (z_i T_{cm} + w_i T_{cp})$$

(25)

In the explicit form the  $j^{th}$  and  $(j+1)^{st}$  terms can be provided as

$$\alpha'_{0} = \frac{1}{D_{\pi'}} \left( \prod_{i=1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j}T_{cm} + w_{j+1}T_{cp})(z_{j+1}T_{cm} + w_{j}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp}) \right)$$

$$\alpha'_{1} = \frac{1}{D_{\pi'}} \left( (w_{0}T_{cp}) \prod_{i=2}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j}T_{cm} + w_{j+1}T_{cp})(z_{j+1}T_{cm} + w_{j}T_{cp}) \right)$$

$$\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

:

$$\alpha'_{j-1} = \frac{1}{D_{\pi'}} \left( \prod_{i=0}^{j-2} (w_i T_{cp}) (z_j T_{cm} + w_{j+1} T_{cp}) (z_{j+1} T_{cm} + w_j T_{cp}) \prod_{i=j+2}^{N} (z_i T_{cm} + w_i T_{cp}) \right)$$

$$\alpha'_{j} = \frac{1}{D_{\pi'}} \left( \prod_{i=0}^{j-2} (w_i T_{cp}) (w_{j-1} T_{cp}) (z_{j+1} T_{cm} + w_j T_{cp}) \prod_{i=j+2}^{N} (z_i T_{cm} + w_i T_{cp}) \right)$$

$$\alpha'_{j+1} = \frac{1}{D_{\pi'}} \left( \prod_{i=0}^{j-2} (w_i T_{cp}) (w_{j-1} T_{cp}) (w_{j+1} T_{cp}) \prod_{i=j+2}^{N} (z_i T_{cm} + w_i T_{cp}) \right)$$

:

$$\alpha'_{N} = \frac{1}{D_{\pi'}} \left( \prod_{i=0}^{N-1} (w_{i} T_{cp}) \right)$$

where,

$$D_{\pi'} = \prod_{i=1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j}T_{cm} + w_{j+1}T_{cp})(z_{j+1}T_{cm} + w_{j}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \sum_{n=1}^{j-1} \left( \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j}T_{cm} + w_{j+1}T_{cp})(z_{j+1}T_{cm} + w_{j}T_{cp}) \right)$$

$$\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \prod_{i=0}^{j-2} (w_{i}T_{cp})(w_{j-1}T_{cp})(z_{j+1}T_{cm} + w_{j}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \prod_{i=0}^{N} (w_{i}T_{cp})(w_{j-1}T_{cp})(w_{j+1}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \sum_{n=i+2}^{N} \left( \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{N} (z_{i}T_{cm} + w_{i}T_{cp}) \right)$$

$$(26)$$

# 3.6 Some Total Computing Cost Related Equations

In this subsection, the relevant equations arising from a total computing cost performance comparison of an original arrangement and a swapped arrangement are given. For the sake of clarity, some pertinent terms are restated here.

$C_{total}$  the total computing cost of an original arrangement  $(\pi)$ .

$C'_{total}$  the total computing cost of an adjacent pairwise processor swapped arrangement  $(\pi')$ .

$N_{\pi}$  the numerator of  $C_{total}$  of an original arrangement  $(\pi)$ .

$N_{\pi'}$  the numerator of  $C_{total}$  of an adjacent pairwise processor swapped arrangement  $(\pi')$ .

$D_{\pi}$  the denominator of  $C_{total}$  of an original arrangement  $(\pi)$ .

$D_{\pi'}$  the denominator of  $C_{total}$  of an adjacent pairwise processor swapped arrangement  $(\pi')$ .

As mentioned in subsection 3.3, one can express the total computing cost in a simple form as,

$$C_{total} = \frac{N_{\pi}}{D_{\pi}}$$

$$C'_{total} = \frac{N_{\pi'}}{D_{\pi'}}$$

# 3.6.1 An Adjacent Pairwise Processor Arrangement

The total computing cost of an adjacent pairwise processor swapped arrangement can be stated as

$$C'_{total} = \alpha'_{0}C'_{0} + \sum_{n=1}^{N} \alpha'_{n}C'_{n}$$

$$= \alpha'_{0}(c^{p}_{0}w_{0}T_{cp}) + \sum_{n=1}^{j-1} \alpha'_{n} \left(c^{l}_{n}z_{n}T_{cm} + c^{p}_{n}w_{n}T_{cp}\right) + \alpha'_{j}(c^{l}_{j}z_{j}T_{cm} + c^{p}_{j+1}w_{j+1}T_{cp})$$

$$+ \alpha'_{j+1}(c^{l}_{j+1}z_{j+1}T_{cm} + c^{p}_{j}w_{j}T_{cp}) + \sum_{n=j+2}^{N} \alpha'_{n} \left(c^{l}_{n}z_{n}T_{cm} + c^{p}_{n}w_{n}T_{cp}\right)$$

(28)

By substituting  $\alpha'_n$  from the previous section into (28) one obtains,

$$C'_{total} = \frac{1}{D_{\pi'}} \left\{ \prod_{i=1}^{j-1} (z_i T_{cm} + w_i T_{cp}) (z_j T_{cm} + w_{j+1} T_{cp}) (z_{j+1} T_{cm} + w_j T_{cp}) \right.$$

$$\cdot \prod_{i=j+2}^{N} (z_i T_{cm} + w_i T_{cp}) (c_0^p w_0 T_{cp})$$

$$+ \sum_{n=1}^{j-1} \left( \prod_{i=0}^{n-1} (w_i T_{cp}) \prod_{i=n+1}^{j-1} (z_i T_{cm} + w_i T_{cp}) (z_j T_{cm} + w_{j+1} T_{cp}) (z_{j+1} T_{cm} + w_j T_{cp}) \right.$$

$$\cdot \prod_{i=j+2}^{N} (z_i T_{cm} + w_i T_{cp}) (c_n^l z_n T_{cm} + c_n^p w_n T_{cp})$$

$$+ \prod_{i=0}^{j-2} (w_i T_{cp}) (w_{j-1} T_{cp}) (z_{j+1} T_{cm} + w_j T_{cp})$$

$$\cdot \prod_{i=j+2}^{N} (z_i T_{cm} + w_i T_{cp}) (c_j^l z_j T_{cm} + c_{j+1}^p w_{j+1} T_{cp})$$

$$+ \prod_{i=0}^{j-2} (w_i T_{cp}) (w_{j-1} T_{cp}) (w_{j+1} T_{cp})$$

$$\cdot \prod_{i=j+2}^{N} (z_i T_{cm} + w_i T_{cp}) (c_{j+1}^l z_{j+1} T_{cm} + c_j^p w_j T_{cp})$$

$$+ \sum_{n=j+2}^{N} \left( \prod_{i=0}^{n-1} (w_i T_{cp}) \prod_{i=n+1}^{N} (z_i T_{cm} + w_i T_{cp}) (c_n^l z_n T_{cm} + c_n^p w_n T_{cp}) \right) \right\}$$

$$(29)$$

where

$$N_{\pi'} = \prod_{i=1}^{j-1} (z_i T_{cm} + w_i T_{cp}) (z_j T_{cm} + w_{j+1} T_{cp}) (z_{j+1} T_{cm} + w_j T_{cp})$$

$$\cdot \prod_{i=j+2}^{N} (z_i T_{cm} + w_i T_{cp}) (c_0^p w_0 T_{cp})$$

$$+ \sum_{n=1}^{j-1} \left( \prod_{i=0}^{n-1} (w_i T_{cp}) \prod_{i=n+1}^{j-1} (z_i T_{cm} + w_i T_{cp}) (z_j T_{cm} + w_{j+1} T_{cp}) (z_{j+1} T_{cm} + w_j T_{cp}) \right)$$

$$\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{n}^{l}z_{n}T_{cm} + c_{n}^{p}w_{n}T_{cp}) \\

+ \prod_{i=0}^{j-2} (w_{i}T_{cp})(w_{j-1}T_{cp})(z_{j+1}T_{cm} + w_{j}T_{cp}) \\

\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{j}^{l}z_{j}T_{cm} + c_{j+1}^{p}w_{j+1}T_{cp}) \\

+ \prod_{i=0}^{j-2} (w_{i}T_{cp})(w_{j-1}T_{cp})(w_{j+1}T_{cp}) \\

\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{j+1}^{l}z_{j+1}T_{cm} + c_{j}^{p}w_{j}T_{cp}) \\

+ \sum_{n=j+2}^{N} \left( \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{n}^{l}z_{n}T_{cm} + c_{n}^{p}w_{n}T_{cp}) \right) \tag{30}$$

$$D_{\pi'} = \prod_{i=1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j}T_{cm} + w_{j+1}T_{cp})(z_{j+1}T_{cm} + w_{j}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \sum_{n=1}^{j-1} \left( \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j}T_{cm} + w_{j+1}T_{cp})(z_{j+1}T_{cm} + w_{j}T_{cp}) \right)$$

$$+ \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp}) \left( \sum_{j+1}^{N} T_{cm} + w_{j}T_{cp} \right) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \prod_{i=0}^{j-2} (w_{i}T_{cp})(w_{j-1}T_{cp})(w_{j+1}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \sum_{n=j+2}^{N} \left( \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{N} (z_{i}T_{cm} + w_{i}T_{cp}) \right)$$

$$(31)$$

#### 3.6.2 An Original Processor Arrangement

The total computing cost of an original arrangement is exactly that derived in subsection 3.3. For clarity it is restated again,

$$N_{\pi} = \prod_{i=1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j}T_{cm} + w_{j}T_{cp})(z_{j+1}T_{cm} + w_{j+1}T_{cp})$$

$$\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{0}^{p}w_{0}T_{cp})$$

$$+ \sum_{n=1}^{j-1} \left( \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j}T_{cm} + w_{j}T_{cp})(z_{j+1}T_{cm} + w_{j+1}T_{cp}) \right)$$

$$\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{n}^{l}z_{n}T_{cm} + c_{n}^{p}w_{n}T_{cp})$$

$$+ \prod_{i=0}^{N} (w_{i}T_{cp})(w_{j-1}T_{cp})(z_{j+1}T_{cm} + w_{j+1}T_{cp})$$

$$\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{j}^{l}z_{j}T_{cm} + c_{j}^{p}w_{j}T_{cp})$$

$$+ \prod_{i=j+2}^{N} (w_{i}T_{cp})(w_{j-1}T_{cp})(w_{j}T_{cp})$$

$$\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{j+1}^{l}z_{j+1}T_{cm} + c_{j+1}^{p}w_{j+1}T_{cp})$$

$$+ \sum_{n=i+2}^{N} \left( \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{n}^{l}z_{n}T_{cm} + c_{n}^{p}w_{n}T_{cp}) \right)$$

$$(32)$$

Similarly we have the denominator for an original arrangement as follows

$$D_{\pi} = \prod_{i=1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j}T_{cm} + w_{j}T_{cp})(z_{j+1}T_{cm} + w_{j+1}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \sum_{n=1}^{j-1} \left( \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j}T_{cm} + w_{j}T_{cp})(z_{j+1}T_{cm} + w_{j+1}T_{cp}) \right)$$

$$\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \prod_{i=0}^{j-2} (w_{i}T_{cp})(w_{j-1}T_{cp})(z_{j+1}T_{cm} + w_{j+1}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \prod_{i=0}^{j-2} (w_{i}T_{cp})(w_{j-1}T_{cp})(w_{j}T_{cp}) \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \sum_{n=j+2}^{N} \left( \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{N} (z_{i}T_{cm} + w_{i}T_{cp}) \right)$$

$$(33)$$

#### 3.6.3 The Difference Equations

The difference between the numerators and the denominators, based on the information just developed, can be given as,

$$N_{\pi} - N_{\pi'} = \prod_{i=1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j+1} - z_{j})(w_{j} - w_{j+1})T_{cm}T_{cp}$$

$$\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{0}^{p}w_{0}T_{cp})$$

$$+ \sum_{n=1}^{j-1} \left(\prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j+1} - z_{j})(w_{j} - w_{j+1})T_{cm}T_{cp}\right)$$

$$\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})(c_{n}^{l}z_{n}T_{cm} + c_{n}^{p}w_{n}T_{cp})

+ \prod_{i=0}^{j-1} (w_{i}T_{cp}) \left[ (w_{j} - w_{j+1})(z_{j+1}c_{j+1}^{l} - z_{j}c_{j}^{l})T_{cm}T_{cp}

+ z_{j+1}T_{cm}T_{cp}(w_{j}c_{j}^{p} - w_{j+1}c_{j+1}^{p}) \right] \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

(34)

$$D_{\pi} - D_{\pi'} = \prod_{i=1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j+1} - z_{j})(w_{j} - w_{j+1})T_{cm}T_{cp} \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$+ \sum_{n=1}^{j-1} \left( \prod_{i=0}^{n-1} (w_{i}T_{cp}) \prod_{i=n+1}^{j-1} (z_{i}T_{cm} + w_{i}T_{cp})(z_{j+1} - z_{j})(w_{j} - w_{j+1})T_{cm}T_{cp} \right)$$

$$\cdot \prod_{i=j+2}^{N} (z_{i}T_{cm} + w_{i}T_{cp})$$

$$(35)$$

To simplify further, define

$$a = \prod_{i=1}^{j-1} (z_i T_{cm} + w_i T_{cp})$$

(36)

$$b = \prod_{i=j+2}^{N} (z_i T_{cm} + w_i T_{cp}) \tag{37}$$

$$d = \prod_{i=0}^{j-1} (w_i T_{cp}) \tag{38}$$

$$C_0 = c_0^p w_0 T_{cp} \tag{39}$$

$$C_n = c_n^l z_n T_{cm} + c_n^p w_n T_{cp} \tag{40}$$

$$k_n = \prod_{i=0}^{n-1} (w_i T_{cp}) \prod_{i=n+1}^{j-1} (z_i T_{cm} + w_i T_{cp})$$

(41)

Hence one has the simpler forms as below,

$$N_{\pi} - N_{\pi'} = a \left[ (z_{j+1} - z_{j})(w_{j} - w_{j+1})T_{cm}T_{cp} \right] bC_{0}$$

$$+ \sum_{n=1}^{j-1} (k_{n} \left[ (z_{j+1} - z_{j})(w_{j} - w_{j+1})T_{cm}T_{cp} \right] bC_{n})$$

$$+ d \left[ (w_{j} - w_{j+1})(z_{j+1}c_{j+1}^{l} - z_{j}c_{j}^{l}) + z_{j+1}(w_{j}c_{j}^{p} - w_{j+1}c_{j+1}^{p}) \right] T_{cm}T_{cp}b$$

$$= (z_{j+1} - z_{j})(w_{j} - w_{j+1})T_{cm}T_{cp}b \left[ aC_{0} + \sum_{n=1}^{j-1} k_{n}C_{n} \right]$$

$$+ d \left[ (w_{j} - w_{j+1})(z_{j+1}c_{j+1}^{l} - z_{j}c_{j}^{l}) + z_{j+1}(w_{j}c_{j}^{p} - w_{j+1}c_{j+1}^{p}) \right] T_{cm}T_{cp}b$$

$$(42)$$

$$D_{\pi} - D_{\pi'} = a \left[ (z_{j+1} - z_j)(w_j - w_{j+1})T_{cm}T_{cp} \right] b$$

$$+ \sum_{n=1}^{j-1} (k_n \left[ (z_{j+1} - z_j)(w_j - w_{j+1})T_{cm}T_{cp} \right] b)$$

$$= (z_{j+1} - z_j)(w_j - w_{j+1})T_{cm}T_{cp} \left[ a + \sum_{n=1}^{j-1} k_n \right] b$$

$$(43)$$

# 4 Cost Efficient Processor Arrangement

In this part, the conditions under which by transposing an adjacent pairwise processor pair the total computing cost performance will improve are found. The conditions under which it is better not transpose an adjacent pairwise processor pair are also found.

# 4.1 The $C_{total}$ Conditions

In this subsection, we first use the simple expression of computing cost, the rational form, to derive some intermediate results. These results exhibit the total computing cost relationships of an original processor arrangement profile,  $C_{total}$ , and that of a transposed processor arrangement profile,  $C'_{total}$ . Incorporated with results from the previous sections regarding the numerators and denominators of the total computing costs, a number of lemmas are then provided.

We can state the difference of the total computing costs of an adjacent pairwise processor arrangement and an original arrangement in a simple form as,

$$C'_{total} - C_{total} = \frac{N_{\pi'}}{D_{\pi'}} - \frac{N_{\pi}}{D_{\pi}}$$

$$\tag{44}$$

$$= \frac{N_{\pi'}D_{\pi} - N_{\pi}D_{\pi'}}{D_{\pi}D_{\pi'}} \tag{45}$$

To obtain the optimal conditions, the expression in (45) will be used. Note that both denominators,  $D_{\pi}$  and  $D_{\pi'}$ , are positive. Therefore to determine the relationships between the total computing cost, it is suffice to consider only the numerator,  $N_{\pi'}D_{\pi} - N_{\pi}D_{\pi'}$ .

Lemma 1 In a single-level tree network, the total cost of a current proces-

sor arrangement,  $C_{total}$ , is less than that of an associated swapped processor arrangement,  $C'_{total}$ , if one of the following conditions holds:

1.

$$N_{\pi'} > N_{\pi}$$

,  $D_{\pi'} < D_{\pi}$ .

2.

$$N_{\pi'} > N_{\pi}$$

,  $D_{\pi'} = D_{\pi}$ .

3.

$$N_{\pi'} > N_{\pi}$$

,  $D_{\pi'} > D_{\pi}$  and  $N_{\pi'}D_{\pi} > N_{\pi}D_{\pi'}$ .

4.

$$N_{\pi'} = N_{\pi}$$

,  $D_{\pi'} < D_{\pi}$ .

5.

$$N_{\pi'} < N_{\pi}$$

,  $D_{\pi'} < D_{\pi}$  and  $N_{\pi'}D_{\pi} > N_{\pi}D_{\pi'}$ .

#### **Proof**

From equation (45):

$$C'_{total} - C_{total} = \frac{N_{\pi'}D_{\pi} - N_{\pi}D_{\pi'}}{D_{\pi}D_{\pi'}}$$

Thus,  $C'_{total} > C_{total}$  when :

$$N_{\pi'}D_{\pi} - N_{\pi}D_{\pi'} > 0 \tag{46}$$

$$N_{\pi'}D_{\pi} > N_{\pi}D_{\pi'} \tag{47}$$

By checking all possible cases of the relationship of  $(N_{\pi}, N_{\pi'})$  and that of  $(D_{\pi}, D_{\pi'})$  that satisfy equation (46) and equation (47), only these conditions result. Thus the lemma is proven.  $\square$

**Lemma 2** In a single-level tree network, the total cost of a current processor arrangement,  $C_{total}$ , is equal to that of an associated swapped processor arrangement,  $C'_{total}$ , if one of the following conditions holds:

1.

$$N_{\pi'} > N_{\pi}$$

,  $D_{\pi'} > D_{\pi}$  and  $N_{\pi'}D_{\pi} = N_{\pi}D_{\pi'}$ .

2.

$$N_{\pi'} = N_{\pi}$$

,  $D_{\pi'} = D_{\pi}$ .

3.

$$N_{\pi'} < N_{\pi}$$

,  $D_{\pi'} < D_{\pi}$  and  $N_{\pi'}D_{\pi} = N_{\pi}D_{\pi'}$ .

#### Proof

From equation (45):

$$C'_{total} - C_{total} = \frac{N_{\pi'}D_{\pi} - N_{\pi}D_{\pi'}}{D_{\pi}D_{\pi'}}$$

Thus,  $C'_{total} = C_{total}$  when :

$$N_{\pi'}D_{\pi} - N_{\pi}D_{\pi'} = 0 (48)$$

$$N_{\pi'}D_{\pi} = N_{\pi}D_{\pi'} \tag{49}$$

By checking all possible cases of the relationship of  $(N_{\pi}, N_{\pi'})$  and that of  $(D_{\pi}, D_{\pi'})$  that satisfy equation (48) and equation (49), only these conditions result. Thus the lemma is proven.  $\square$

Lemma 3 In a single-level tree network, the total cost of a current processor

arrangement,  $C_{total}$ , is greater than that of an associated swapped processor arrangement,  $C'_{total}$ , if one of the following conditions holds:

1.

$$N_{\pi'} < N_{\pi}$$

,  $D_{\pi'} > D_{\pi}$ .

2.

$$N_{\pi'} < N_{\pi}$$

,  $D_{\pi'} = D_{\pi}$ .

3.

$$N_{\pi'} < N_{\pi}$$

,  $D_{\pi'} < D_{\pi}$  and  $N_{\pi'}D_{\pi} < N_{\pi}D_{\pi'}$ .

4.

$$N_{\pi'} = N_{\pi} , D_{\pi'} > D_{\pi}.$$

5.

$$N_{\pi'} > N_{\pi}$$

,  $D_{\pi'} > D_{\pi}$  and  $N_{\pi'}D_{\pi} < N_{\pi}D_{\pi'}$ .

## Proof

From equation (45):

$$C'_{total} - C_{total} = \frac{N_{\pi'}D_{\pi} - N_{\pi}D_{\pi'}}{D_{\pi}D_{\pi'}}$$

Thus,  $C'_{total} < C_{total}$  when:

$$N_{\pi'}D_{\pi} - N_{\pi}D_{\pi'} \quad < \quad 0. \tag{50}$$

$$N_{\pi'}D_{\pi} \quad < \quad N_{\pi}D_{\pi'} \tag{51}$$

By checking all possible cases of the relationship of  $(N_{\pi}, N_{\pi'})$  and of  $(D_{\pi}, D_{\pi'})$  that satisfy equation (50) and equation (51), only these conditions result. Thus the lemma is proven.  $\Box$

**Lemma 4** In a single-level tree network, the relationship between the numerator of a current processor arrangement  $(N_{\pi})$  and the numerator of an associated swapped processor arrangement  $(N_{\pi'})$  can be stated equivalently in terms of  $z_j$ ,  $z_{j+1}$ ,  $C_j$ , and  $C_{j+1}$  as follows:

1.

$$N_{\pi'} > N_{\pi}$$

iff

$$\left[ (w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) + z_{j+1}(w_jc_j^p - w_{j+1}c_{j+1}^p) \right]$$

$$< \frac{1}{d} \left\{ (z_j - z_{j+1})(w_j - w_{j+1}) \cdot \left[ aC_0 + \sum_{n=1}^{j-1} k_n C_n \right] \right\}$$

2.

$$N_{\pi'} = N_{\pi}$$

iff

$$\left[ (w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) + z_{j+1}(w_jc_j^p - w_{j+1}c_{j+1}^p) \right]

= \frac{1}{d} \left\{ (z_j - z_{j+1})(w_j - w_{j+1}) \cdot \left[ aC_0 + \sum_{n=1}^{j-1} k_n C_n \right] \right\}$$

3.

$$N_{\pi'} < N_{\pi}$$

iff

$$\left[ (w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) + z_{j+1}(w_jc_j^p - w_{j+1}c_{j+1}^p) \right]$$

$$> \frac{1}{d} \left\{ (z_j - z_{j+1})(w_j - w_{j+1}) \cdot \left[ aC_0 + \sum_{n=1}^{j-1} k_n C_n \right] \right\}$$

#### **Proof**

From the difference equation of equation (42):

$$N_{\pi} - N_{\pi'} = (z_{j+1} - z_j)(w_j - w_{j+1})T_{cm}T_{cp}b\left[aC_0 + \sum_{n=1}^{j-1} k_nC_n\right]$$

$$+d \left[ (w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) \right.$$

$$+ z_{j+1}(w_jc_j^p - w_{j+1}c_{j+1}^p) \left] T_{cm}T_{cp}b \right.$$

Then, these conditions are obvious from the above equation.  $\Box$

**Lemma 5** In a single-level tree network, the relationship between the denominator of a current processor arrangement  $(D_{\pi})$  and the denominator of an associated swapped processor arrangement  $(D_{\pi'})$  can be stated equivalently in terms of  $z_j$ ,  $z_{j+1}$ ,  $C_j$ , and  $C_{j+1}$  as follows:

1.

$$D_{\pi'} > D_{\pi}$$

iff

$$(z_{j+1}-z_j)(w_j-w_{j+1}) < 0$$

2.

$$D_{\pi'} = D_{\pi}$$

iff

$$(z_{j+1} - z_j)(w_j - w_{j+1}) = 0$$

3.

$$D_{\pi'} < D_{\pi}$$

iff

$$(z_{j+1}-z_j)(w_j-w_{j+1}) > 0$$

## **Proof**

From the difference equation of equation (43):

$$D_{\pi} - D_{\pi'} = (z_{j+1} - z_j)(w_j - w_{j+1})T_{cm}T_{cp}\left[a + \sum_{n=1}^{j-1} k_n\right]b$$

Then, these conditions are obvious from the above equation.  $\Box$

## 4.2 The Intermediate Results

From the lemmas in the previous subsection, a number of intermediate results can be derived as follows.

# 4.2.1 The Intermediate Results from Lemma 1 where $C'_{total} > C_{total}$

1.

$$N_{\pi'} > N_{\pi}, D_{\pi'} < D_{\pi}$$

That is,

$$\left[ (w_{j} - w_{j+1})(z_{j+1}c_{j+1}^{l} - z_{j}c_{j}^{l}) + z_{j+1}(w_{j}c_{j}^{p} - w_{j+1}c_{j+1}^{p}) \right] < \frac{1}{d} \left\{ (z_{j} - z_{j+1})(w_{j} - w_{j+1}) \left[ aC_{0} + \sum_{n=1}^{j-1} k_{n}C_{n} \right] \right\}$$

(52)

and

$$(z_{j+1} - z_j)(w_j - w_{j+1}) > 0 (53)$$

2.

$$N_{\pi'} > N_{\pi}, D_{\pi'} = D_{\pi}$$

That is,

$$\left[ (w_{j} - w_{j+1})(z_{j+1}c_{j+1}^{l} - z_{j}c_{j}^{l}) + z_{j+1}(w_{j}c_{j}^{p} - w_{j+1}c_{j+1}^{p}) \right] < \frac{1}{d} \left\{ (z_{j} - z_{j+1})(w_{j} - w_{j+1}) \left[ aC_{0} + \sum_{n=1}^{j-1} k_{n}C_{n} \right] \right\}$$

(54)

and

$$(z_{i+1} - z_j)(w_j - w_{j+1}) = 0 (55)$$

3.  $N_{\pi'} > N_{\pi}, D_{\pi'} > D_{\pi} \text{ and } N_{\pi'}D_{\pi} > N_{\pi}D_{\pi'}$

That is

$$\left[ (w_{j} - w_{j+1})(z_{j+1}c_{j+1}^{l} - z_{j}c_{j}^{l}) + z_{j+1}(w_{j}c_{j}^{p} - w_{j+1}c_{j+1}^{p}) \right] < \frac{1}{d} \left\{ (z_{j} - z_{j+1})(w_{j} - w_{j+1}) \left[ aC_{0} + \sum_{n=1}^{j-1} k_{n}C_{n} \right] \right\}$$

(56)

and

$$(z_{j+1} - z_j)(w_j - w_{j+1}) < 0 (57)$$

and

$$N_{\pi'}D_{\pi} > N_{\pi}D_{\pi'}$$

4.

$$N_{\pi'} = N_{\pi}, D_{\pi'} < D_{\pi}$$

That is,

$$\left[ (w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) + z_{j+1}(w_jc_j^p - w_{j+1}c_{j+1}^p) \right] = \frac{1}{d} \left\{ (z_j - z_{j+1})(w_j - w_{j+1}) \left[ aC_0 + \sum_{n=1}^{j-1} k_n C_n \right] \right\}$$

(58)

$$(z_{j+1} - z_j)(w_j - w_{j+1}) > 0 (59)$$

5.  $N_{\pi'} < N_{\pi}, D_{\pi'} < D_{\pi} \text{ and } N_{\pi'}D_{\pi} > N_{\pi}D_{\pi'}$

That is

$$\left[ (w_{j} - w_{j+1})(z_{j+1}c_{j+1}^{l} - z_{j}c_{j}^{l}) + z_{j+1}(w_{j}c_{j}^{p} - w_{j+1}c_{j+1}^{p}) \right] >$$

$$\frac{1}{d} \left\{ (z_{j} - z_{j+1})(w_{j} - w_{j+1}) \left[ aC_{0} + \sum_{n=1}^{j-1} k_{n}C_{n} \right] \right\}$$

(60)

and

$$(z_{j+1} - z_j)(w_j - w_{j+1}) > 0 (61)$$

and

$$N_{\pi'}D_{\pi} > N_{\pi}D_{\pi'}$$

# 4.2.2 The Intermediate Results from Lemma 2 where $C_{total}' = C_{total}$

1.

$$N_{\pi'} > N_{\pi}$$

,  $D_{\pi'} > D_{\pi}$  and  $N_{\pi'}D_{\pi} = N_{\pi}D_{\pi'}$

That is

$$\left[ (w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) + z_{j+1}(w_jc_j^p - w_{j+1}c_{j+1}^p) \right] < \frac{1}{d} \left\{ (z_j - z_{j+1})(w_j - w_{j+1}) \left[ aC_0 + \sum_{n=1}^{j-1} k_n C_n \right] \right\}$$

(62)

and

$$(z_{j+1} - z_j)(w_j - w_{j+1}) < 0 (63)$$

$$N_{\pi'}D_{\pi}=N_{\pi}D_{\pi'}$$

2.  $N_{\pi'} = N_{\pi}, D_{\pi'} = D_{\pi}$

That is,

$$\left[ (w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) + z_{j+1}(w_jc_j^p - w_{j+1}c_{j+1}^p) \right] = \frac{1}{d} \left\{ (z_j - z_{j+1})(w_j - w_{j+1}) \left[ aC_0 + \sum_{n=1}^{j-1} k_n C_n \right] \right\}$$

(64)

and

$$(z_{j+1} - z_j)(w_j - w_{j+1}) = 0 (65)$$

3.  $N_{\pi'} < N_{\pi}, D_{\pi'} < D_{\pi}$  and  $N_{\pi'}D_{\pi} = N_{\pi}D_{\pi'}$

That is

$$\left[ (w_{j} - w_{j+1})(z_{j+1}c_{j+1}^{l} - z_{j}c_{j}^{l}) + z_{j+1}(w_{j}c_{j}^{p} - w_{j+1}c_{j+1}^{p}) \right] >$$

$$\frac{1}{d} \left\{ (z_{j} - z_{j+1})(w_{j} - w_{j+1}) \left[ aC_{0} + \sum_{n=1}^{j-1} k_{n}C_{n} \right] \right\}$$

(66)

and

$$(z_{j+1} - z_j)(w_j - w_{j+1}) > 0 (67)$$

$$N_{\pi'}D_{\pi} = N_{\pi}D_{\pi'}$$

## 4.2.3 The Intermediate Results from Lemma 3 where $C'_{total} < C_{total}$

1.  $N_{\pi'} < N_{\pi}, D_{\pi'} > D_{\pi}$

That is,

$$\left[ (w_{j} - w_{j+1})(z_{j+1}c_{j+1}^{l} - z_{j}c_{j}^{l}) + z_{j+1}(w_{j}c_{j}^{p} - w_{j+1}c_{j+1}^{p}) \right] >$$

$$\frac{1}{d} \left\{ (z_{j} - z_{j+1})(w_{j} - w_{j+1}) \left[ aC_{0} + \sum_{n=1}^{j-1} k_{n}C_{n} \right] \right\}$$

(68)

and

$$(z_{j+1} - z_j)(w_j - w_{j+1}) < 0 (69)$$

2.  $N_{\pi'} < N_{\pi}, D_{\pi'} = D_{\pi}$

That is,

$$\left[ (w_{j} - w_{j+1})(z_{j+1}c_{j+1}^{l} - z_{j}c_{j}^{l}) + z_{j+1}(w_{j}c_{j}^{p} - w_{j+1}c_{j+1}^{p}) \right] > \frac{1}{d} \left\{ (z_{j} - z_{j+1})(w_{j} - w_{j+1}) \left[ aC_{0} + \sum_{n=1}^{j-1} k_{n}C_{n} \right] \right\}$$

(70)

and

$$(z_{j+1} - z_j)(w_j - w_{j+1}) = 0 (71)$$

3.  $N_{\pi'} < N_{\pi}, D_{\pi'} < D_{\pi} \text{ and } N_{\pi'}D_{\pi} < N_{\pi}D_{\pi'}$

That is

$$\left[(w_j-w_{j+1})(z_{j+1}c_{j+1}^l-z_jc_j^l)+z_{j+1}(w_jc_j^p-w_{j+1}c_{j+1}^p)\right]>$$

$$\frac{1}{d} \left\{ (z_j - z_{j+1})(w_j - w_{j+1}) \left[ aC_0 + \sum_{n=1}^{j-1} k_n C_n \right] \right\}$$

(72)

and

$$(z_{j+1} - z_j)(w_j - w_{j+1}) > 0 (73)$$

and

$$N_{\pi'}D_{\pi} < N_{\pi}D_{\pi'}$$

4.

$$N_{\pi'} = N_{\pi}, D_{\pi'} > D_{\pi}$$

That is,

$$\left[ (w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) + z_{j+1}(w_jc_j^p - w_{j+1}c_{j+1}^p) \right] = \frac{1}{d} \left\{ (z_j - z_{j+1})(w_j - w_{j+1}) \left[ aC_0 + \sum_{n=1}^{j-1} k_n C_n \right] \right\}$$

(74)

and

$$(z_{j+1} - z_j)(w_j - w_{j+1}) < 0 (75)$$

5.

$$N_{\pi'} > N_{\pi}$$

,  $D_{\pi'} > D_{\pi}$  and  $N_{\pi'}D_{\pi} < N_{\pi}D_{\pi'}$

That is

$$\left[ (w_{j} - w_{j+1})(z_{j+1}c_{j+1}^{l} - z_{j}c_{j}^{l}) + z_{j+1}(w_{j}c_{j}^{p} - w_{j+1}c_{j+1}^{p}) \right] < \frac{1}{d} \left\{ (z_{j} - z_{j+1})(w_{j} - w_{j+1}) \left[ aC_{0} + \sum_{n=1}^{j-1} k_{n}C_{n} \right] \right\}$$

(76)

and

$$(z_{i+1} - z_i)(w_i - w_{i+1}) < 0 (77)$$

and

$$N_{\pi'}D_{\pi} < N_{\pi}D_{\pi'}$$

## 4.3 The Main Results

From the findings in the previous subsection, the conditions for processor arrangement can be divided into two cases as follows:

**4.3.1** Case I

$$(z_j - z_{j+1})(w_j - w_{j+1}) = 0$$

or  $D_{\pi'} = D_{\pi}$

This case includes:

1.

$$N_{\pi'} > N_{\pi}$$

,  $D_{\pi'} = D_{\pi}$ , where  $C'_{total} > C_{total}$ .

From equation (54) and equation (55), one has:

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) < z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p)$$

(78)

2.

$$N_{\pi'} = N_{\pi}$$

,  $D_{\pi'} = D_{\pi}$ , where  $C'_{total} = C_{total}$ .

From equation (64) and equation (65), one has:

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) = z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p)$$

(79)

3.  $N_{\pi'} < N_{\pi}, D_{\pi'} = D_{\pi}$ , where  $C'_{total} < C_{total}$ .

From equation (70) and equation (71), one has:

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) > z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p)$$

(80)

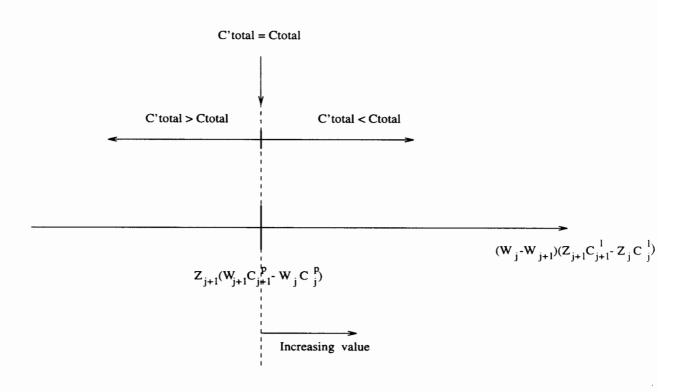

It can be represented by the figure below:

Case I:  $D'_{\pi i} = D'$

In this figure  $(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l)$  is a testing variable and  $z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p)$  is a threshold. If the testing value  $(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l)$  is less than the threshold value  $z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p)$ , then  $C'_{total} > C_{total}$ . If they are equal, then  $C'_{total} = C_{total}$ . Otherwise  $C'_{total} < C_{total}$ .

**4.3.2** Case II  $(z_j - z_{j+1})(w_j - w_{j+1}) \neq 0$  or  $D_{\pi'} \neq D_{\pi}$

Let

$$\Delta = \frac{1}{d} \left\{ (z_j - z_{j+1})(w_j - w_{j+1}) \left[ aC_0 + \sum_{n=1}^{j-1} k_n C_n \right] \right\}$$

(81)

This case includes:

## A. Lemma 1 Related Results

1.  $N_{\pi'} > N_{\pi}$ ,  $D_{\pi'} < D_{\pi}$ , where  $C'_{total} > C_{total}$ .

From equation (52) and equation (53), one has:

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) < z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p) + \underbrace{\Delta}_{pentive}$$

(82)

2.  $N_{\pi'} > N_{\pi}$ ,  $D_{\pi'} > D_{\pi}$ , where  $C'_{total} > C_{total}$ .

From equation (56) and equation (57), one has:

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) < z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p) + \underbrace{\Delta}_{positive}(83)$$

and

$$N_{\pi'}D_{\pi} > N_{\pi}D_{\pi'}$$

3.  $N_{\pi'} = N_{\pi}, D_{\pi'} < D_{\pi}, \text{ where } C'_{total} > C_{total}$ .

From equation (58) and equation (59), one has:

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) = z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p) + \underbrace{\Delta}_{negative}$$

(84)

4.  $N_{\pi'} < N_{\pi}, D_{\pi'} < D_{\pi}, \text{ where } C'_{total} > C_{total}$ .

From equation (60) and equation (61), one has:

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) > z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p) + \underbrace{\Delta}_{negative}(85)$$

and

$$N_{\pi'}D_{\pi} > N_{\pi}D_{\pi'}$$

## B. Lemma 2 Related Results

1.  $N_{\pi'} > N_{\pi}$ ,  $D_{\pi'} > D_{\pi}$ , where  $C'_{total} = C_{total}$ .

From equation (62) and equation (63), one has:

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) < z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p) + \underbrace{\Delta}_{positive}(86)$$

$$N_{\pi'}D_{\pi} = N_{\pi}D_{\pi'}$$

2.  $N_{\pi'} < N_{\pi}, D_{\pi'} < D_{\pi}$ , where  $C'_{total} = C_{total}$ .

From equation (66) and equation (67), one has:

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) > z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p) + \underbrace{\Delta}_{negative}(87)$$

and

$$N_{\pi'}D_{\pi} = N_{\pi}D_{\pi'}$$

## C. Lemma 3 Related Results

1.  $N_{\pi'} < N_{\pi}$ ,  $D_{\pi'} > D_{\pi}$ , where  $C'_{total} < C_{total}$ .

From equation (68) and equation (69), one has:

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) > z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p) + \underbrace{\Delta}_{positive}$$

(88)

2.  $N_{\pi'} < N_{\pi}$ ,  $D_{\pi'} < D_{\pi}$ , where  $C'_{total} < C_{total}$ .

From equation (72) and equation (73), one has:

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) > z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p) + \underbrace{\Delta}_{negative}$$

and

$$N_{\pi'}D_{\pi} < N_{\pi}D_{\pi'}$$

3.  $N_{\pi'} = N_{\pi}, D_{\pi'} > D_{\pi}, \text{ where } C'_{total} < C_{total}.$

From equation (74) and equation (75), one has:

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) = z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p) + \underbrace{\Delta}_{positive}$$

(90)

4.  $N_{\pi'} > N_{\pi}$ ,  $D_{\pi'} > D_{\pi}$ , where  $C'_{total} < C_{total}$ .

From equation (76) and equation (77), one has:

$$(w_{j} - w_{j+1})(z_{j+1}c_{j+1}^{l} - z_{j}c_{j}^{l}) < z_{j+1}(w_{j+1}c_{j+1}^{p} - w_{j}c_{j}^{p}) + \underbrace{\Delta}_{positive}(91)$$

$$and$$

$$N_{\pi'}D_{\pi} < N_{\pi}D_{\pi'}$$

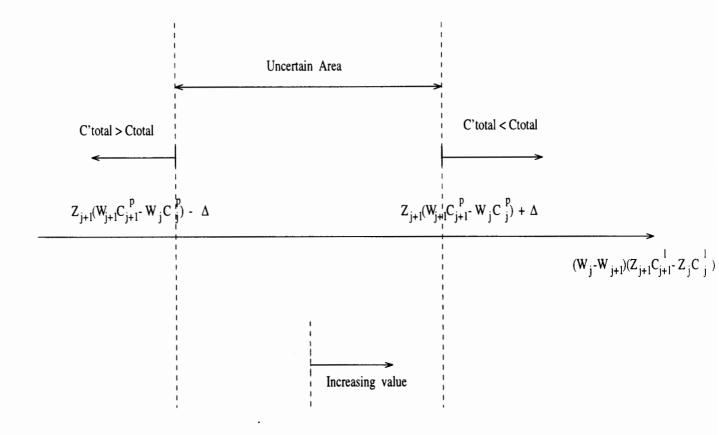

It can be represented by the figure below:

$$\Delta = \frac{1}{d} \left\{ \left| (z_j - z_{j+1})(w_j - w_{j+1}) \right| \left[ aC_0 + \sum_{n=1}^{j-1} k_n C_n \right] \right\}$$

(92)

Note  $\Delta$  is assumed positive here.

In this figure  $(w_j-w_{j+1})(z_{j+1}c_{j+1}^l-z_jc_j^l)$  is a testing variable,  $z_{j+1}(w_{j+1}c_{j+1}^p-w_jc_j^p)+\Delta$  is an upper threshold, and  $z_{j+1}(w_{j+1}c_{j+1}^p-w_jc_j^p)-\Delta$  is a lower threshold. If the testing value  $(w_j-w_{j+1})(z_{j+1}c_{j+1}^l-z_jc_j^l)$  is less than the lower threshold value  $z_{j+1}(w_{j+1}c_{j+1}^p-w_jc_j^p)-\Delta$ , then  $C'_{total}>C_{total}$ . If the

testing value  $(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l)$  is greater than the upper threshold value  $z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p) + \Delta$ , then  $C'_{total} < C_{total}$ . Otherwise, the relationship of  $C'_{total}$  and  $C_{total}$  need further checking as will be discussed later.

## 4.3.3 Uncertain Area Revisited

The uncertain area resulted from the uncertain cases where  $N_{\pi'} > N_{\pi}$ ,  $D_{\pi'} > D_{\pi}$  according to section 4.3.2.A.2, 4.3.2.B.1, 4.3.2.C.4 and  $N_{\pi'} < N_{\pi}$ ,  $D_{\pi'} < D_{\pi}$  according to section 4.3.2.A.4, 4.3.2.B.2, 4.3.2.C.2. So as to simplify the conditions involved in that area, an alternative means of analysis of the two uncertain cases will be provided in the following.

1.

$$N_{\pi'} > N_{\pi}, D_{\pi'} > D_{\pi}$$

Let

$$D_{\pi'} = D_{\pi} + \Delta_D \quad , \Delta_D > 0$$

$$N_{\pi'} = N_{\pi} + \Delta_N \quad , \Delta_N > 0$$

$$\frac{N_{\pi}}{D_{\pi}} - \frac{N_{\pi'}}{D_{\pi'}} = \frac{N_{\pi}}{D_{\pi}} - \frac{(N_{\pi} + \Delta_N)}{(D_{\pi} + \Delta_D)}$$

$$= \frac{N_{\pi}D_{\pi} + N_{\pi}\Delta_{D} - N_{\pi}D_{\pi} - D_{\pi}\Delta_{N}}{D_{\pi}(D_{\pi} + \Delta_{D})}$$

$$= \frac{N_{\pi}\Delta_{D} - D_{\pi}\Delta_{N}}{D_{\pi}(D_{\pi} + \Delta_{D})}$$

(93)

(a)  $C'_{total} > C_{total}$  associated with 4.3.2.A.2.

$$N_{\pi}\Delta_{D} - D_{\pi}\Delta_{N} < 0$$

$$\frac{N_{\pi}}{D_{\pi}} < \frac{\Delta_{N}}{\Delta_{D}}$$

$$< \frac{(N_{\pi'} - N_{\pi})}{(D_{\pi'} - D_{\pi})}$$

(94)

(b)  $C'_{total} = C_{total}$  associated with 4.3.2.B.1.

$$N_{\pi}\Delta_{D} - D_{\pi}\Delta_{N} = 0$$

$$\frac{N_{\pi}}{D_{\pi}} = \frac{\Delta_{N}}{\Delta_{D}}$$

$$= \frac{(N_{\pi'} - N_{\pi})}{(D_{\pi'} - D_{\pi})}$$

(95)

(c)  $C'_{total} < C_{total}$  associated with 4.3.2.C.4.

$$N_{\pi}\Delta_{D} - D_{\pi}\Delta_{N} > 0$$

$$\frac{N_{\pi}}{D_{\pi}} > \frac{\Delta_{N}}{\Delta_{D}}$$

$$> \frac{(N_{\pi'} - N_{\pi})}{(D_{\pi'} - D_{\pi})}$$

(96)

2.  $N_{\pi'} < N_{\pi}, D_{\pi'} < D_{\pi}$

Let

$$D_{\pi} = D_{\pi'} + \Delta_D , \Delta_D > 0$$

$$N_{\pi} = N_{\pi'} + \Delta_N , \Delta_N > 0$$

$$\frac{N_{\pi}}{D_{\pi}} - \frac{N_{\pi'}}{D_{\pi'}} = \frac{(N_{\pi'} + \Delta_N)}{(D_{\pi'} + \Delta_D)} - \frac{N_{\pi'}}{D_{\pi'}}$$

$$= \frac{N_{\pi'}D_{\pi'} + D_{\pi'}\Delta_N - N_{\pi'}D_{\pi'} - N_{\pi'}\Delta_D}{D_{\pi'}(D_{\pi'} + \Delta_D)}$$

$$= \frac{D_{\pi'}\Delta_N - N_{\pi'}\Delta_D}{D_{\pi'}(D_{\pi'} + \Delta_D)} \tag{97}$$

(a)  $C'_{total} > C_{total}$  associated with 4.3.2.A.4.

$$D_{\pi'}\Delta_N - N_{\pi'}\Delta_D < 0$$

$$\frac{N_{\pi'}}{D_{\pi'}} > \frac{\Delta_N}{\Delta_D}$$

$$> \frac{(N_{\pi} - N_{\pi'})}{(D_{\pi} - D_{\pi'})}$$

(98)

(b)  $C'_{total} = C_{total}$  associated with 4.3.2.B.2

$$D_{\pi'}\Delta_N - N_{\pi'}\Delta_D = 0$$

$$\frac{N_{\pi'}}{D_{\pi'}} = \frac{\Delta_N}{\Delta_D}$$

$$= \frac{(N_{\pi} - N_{\pi'})}{(D_{\pi} - D_{\pi'})}$$

(99)

(c)  $C'_{total} < C_{total}$  associated with 4.3.2.C.2.

$$D_{\pi'}\Delta_N - N_{\pi'}\Delta_D > 0$$

$$\frac{N_{\pi'}}{D_{\pi'}} < \frac{\Delta_N}{\Delta_D}$$

$$< \frac{(N_{\pi} - N_{\pi'})}{(D_{\pi} - D_{\pi'})}$$

(100)

Therefore, in the uncertain area, one has:

1.

$$D_{\pi'} > D_{\pi}$$

or  $(z_{j+1} - z_j)(w_j - w_{j+1}) < 0$

(a)  $C'_{total} > C_{total}$ , if

$$C_{total} = \frac{N_{\pi}}{D_{\pi}} < \frac{(N_{\pi} - N_{\pi'})}{(D_{\pi} - D_{\pi'})} \tag{101}$$

(b)  $C'_{total} = C_{total}$ , if

$$C_{total} = \frac{N_{\pi}}{D_{\pi}} = \frac{(N_{\pi} - N_{\pi'})}{(D_{\pi} - D_{\pi'})}$$

(102)

(c)  $C'_{total} < C_{total}$ , if

$$C_{total} = \frac{N_{\pi}}{D_{\pi}} > \frac{(N_{\pi} - N_{\pi'})}{(D_{\pi} - D_{\pi'})} \tag{103}$$

2.

$$D_{\pi'} < D_{\pi}$$

or  $(z_{j+1} - z_j)(w_j - w_{j+1}) > 0$

(a)  $C'_{total} > C_{total}$ , if

$$C'_{total} = \frac{N_{\pi'}}{D_{\pi'}} > \frac{(N_{\pi} - N_{\pi'})}{(D_{\pi} - D_{\pi'})} \tag{104}$$

(b)  $C'_{total} = C_{total}$ , if

$$C'_{total} = \frac{N_{\pi'}}{D_{\pi'}} = \frac{(N_{\pi} - N_{\pi'})}{(D_{\pi} - D_{\pi'})}$$

(105)

(c)  $C'_{total} < C_{total}$ , if

$$C'_{total} = \frac{N_{\pi'}}{D_{\pi'}} < \frac{(N_{\pi} - N_{\pi'})}{(D_{\pi} - D_{\pi'})}$$

(106)

From equation (42) and equation (43), one has:

$$\frac{(N_{\pi} - N_{\pi'})}{(D_{\pi} - D_{\pi'})} = \frac{aC_0 + \sum_{n=1}^{j-1} k_n C_n}{a + \sum_{n=1}^{j-1} k_n} + \frac{d(z_{j+1}c_{j+1}^l - z_j c_j^l)}{(z_{j+1} - z_j)(a + \sum_{n=1}^{j-1} k_n)} + \frac{d(w_j c_j^p - w_{j+1}c_{j+1}^p)z_{j+1}}{(z_{j+1} - z_j)(w_j - w_{j+1})(a + \sum_{n=1}^{j-1} k_n)}$$

(107)

#### 4.3.4 The Resulting Theorems

Theorem 1 In a single-level tree network, if one of the following conditions is satisfied, then the total cost of the current processor arrangement  $C_{total}(\pi_{(p_1,...,p_j,p_{j+1},....,p_N)})$  is less than the total cost of the adjacent pairwise swapped processor arrangement  $C'_{total}(\pi'_{(p_1,...,p_{j+1},p_j,...,p_N)})$  for  $1 \leq j < N$ .

1).

$$(z_{j+1}-z_j)(w_j-w_{j+1})=0$$

and  $(w_j-w_{j+1})(z_{j+1}c_{j+1}^l-z_jc_j^l)< z_{j+1}(w_{j+1}c_{j+1}^p-w_jc_j^p)$

2).  $(z_{j+1}-z_j)(w_j-w_{j+1})\neq 0$  and

$$(w_i - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) \le z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p) - \Delta$$

3).

$$(z_{j+1}-z_j)(w_j-w_{j+1})<0$$

and  $C_{total}<\frac{(N_\pi-N_{\pi'})}{(D_\pi-D_{\pi'})}$

4).

$$(z_{j+1}-z_j)(w_j-w_{j+1})>0$$

and  $C'_{total}>\frac{(N_{\pi}-N_{\pi'})}{(D_{\pi}-D_{\pi'})}$

## **Proof**

The first condition results from equation (78).

The second condition results from equation (82) and equation (84).

The third condition results from equation (101).

The fourth condition results from equation (104).

Thus the theorem is proved.  $\Box$

**Theorem 2** In a single-level tree network, if one of the following conditions is satisfied, then the total cost of the current processor arrangement  $C_{total}(\pi_{(p_1,\ldots,\underline{p_j,p_{j+1}},\ldots,p_N)})$  is equal to the total cost of the adjacent pairwise swapped processor arrangement  $C'_{total}(\pi'_{(p_1,\ldots,\underline{p_{j+1},p_{j}},\ldots,p_N)})$  for  $1 \leq j < N$ .

1).

$$(z_{j+1}-z_j)(w_j-w_{j+1})=0$$

and

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) = z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p)$$

2).

$$(z_{j+1}-z_j)(w_j-w_{j+1})\neq 0$$

and  $C_{total}=\frac{(N_{\pi}-N_{\pi'})}{(D_{\pi}-D_{\pi'})}$

## Proof

The first condition results from equation (79).

The second condition results from equation (102) and equation (105).

Thus the theorem is proved.  $\Box$

**Theorem 3** In a single-level tree network, if one of the following conditions is satisfied, then the total cost of the current processor arrangement  $C_{total}(\pi_{(p_1,...,p_{j+1},...,p_N)})$  is greater than the total cost of the adjacent pairwise swapped processor arrangement  $C'_{total}(\pi'_{(p_1,...,p_{j+1},p_j,...,p_N)})$  for  $1 \leq j < N$ .

1).

$$(z_{j+1} - z_j)(w_j - w_{j+1}) = 0$$

and

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) > z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p)$$

2).

$$(z_{j+1}-z_j)(w_j-w_{j+1}) \neq 0$$

and

$$(w_j - w_{j+1})(z_{j+1}c_{j+1}^l - z_jc_j^l) \ge z_{j+1}(w_{j+1}c_{j+1}^p - w_jc_j^p) + \Delta$$

3).

$$(z_{j+1}-z_j)(w_j-w_{j+1})<0$$

and  $C_{total}>\frac{(N_{\pi}-N_{\pi'})}{(D_{\pi}-D_{\pi'})}$

4).

$$(z_{j+1}-z_j)(w_j-w_{j+1})>0$$

and  $C'_{total}<\frac{(N_{\pi}-N_{\pi'})}{(D_{\pi}-D_{\pi'})}$

## Proof

The first condition results from equation (80).

The second condition results from equation (88) and equation (90).

The third condition results from equation (103).

The fourth condition results from equation (106).

Thus the theorem is proved.  $\Box$

Here:

$$\Delta = \frac{1}{d} \left\{ |(z_j - z_{j+1})(w_j - w_{j+1})| \left[ aC_0 + \sum_{n=1}^{j-1} k_n C_n \right] \right\}$$

$$\frac{(N_{\pi} - N_{\pi'})}{(D_{\pi} - D_{\pi'})} = \frac{aC_0 + \sum_{n=1}^{j-1} k_n C_n}{a + \sum_{n=1}^{j-1} k_n} + \frac{d(z_{j+1}c_{j+1}^l - z_j c_j^l)}{(z_{j+1} - z_j)(a + \sum_{n=1}^{j-1} k_n)} + \frac{d(w_j c_j^p - w_{j+1}c_{j+1}^p)z_{j+1}}{(z_{j+1} - z_j)(w_j - w_{j+1})(a + \sum_{n=1}^{j-1} k_n)}$$

## 5 Bus and Related Networks

## 5.1 Bus Network

A bus network is a special case of a single-level tree network where all link speeds and link costs are equal. The following lemma and theorem can be obtained: **Lemma 6** In a bus network, the total cost of a current processor arrangement,  $C_{total}$ , is less than or equal to (greater than) that of an associated swapped processor arrangement,  $C'_{total}$ , if, for the current processor arrangement,  $C'_{total}$ , if, for the current processor arrangement,

$$c_j^p w_j \le (>) c_{j+1}^p w_{j+1}$$

## Proof

In case of a bus network one has  $z_j = z_{j+1}$  and  $z_j c_j^l = z_{j+1} c_{j+1}^l$ , therefore  $(z_{j+1} - z_j)(w_j - w_{j+1}) = 0$ . For the case  $C'_{total} > C_{total}$ , from condition 1 of theorem 1,2 one has,

$$z_{j+1}(c_{j+1}^p w_{j+1} - c_j^p w_j) \ge 0$$

$c_j^p w_j \le c_{j+1}^p w_{j+1}$

A similar result holds for the case of  $C_{total} > C'_{total}$  if one uses condition 1 of theorem 3. The lemma is thus proved.  $\square$

**Lemma 7** In a bus network, if the processors are arranged such that for every adjacent pair of processors the condition  $c_j^p w_j \leq c_{j+1}^p w_{j+1}$  is satisfied, then there is no other processor arrangement profile with a lower total cost.

## Proof

By contradiction, assume that an underlying processor arrangement profile  $\pi$  is arranged such that for every adjacent pair the condition  $c_j^p w_j \leq c_{j+1}^p w_{j+1}$  holds, and there exists another processor arrangement profile  $\pi'$ , a permutation of  $\pi$ , that has at least one adjacent pair of processors with a condition  $c_j^p w_j > c_{j+1}^p w_{j+1}$  which gives a lower total cost than  $\pi$ . By lemma 6, a total cost of  $\pi'$  can be decreased by swapping a pair of processors with the condition  $c_j^p w_j > c_{j+1}^p w_{j+1}$ . Lemma 6 can then be applied recursively to the resulting processor arrangement profile as far as it has such an adjacent pair of processors with the condition  $c_j^p w_j > c_{j+1}^p w_{j+1}$ . The total cost of the current processor arrangement profile is decreased each time lemma 6 is applied. Finally,  $\pi$  is reached from  $\pi'$  through a series of lemma 6 applications. Therefore a total cost of  $\pi$  is lower than that of  $\pi'$ . This contradicts the hypothesis that  $\pi'$  gives a lower total cost that  $\pi$ . The lemma is thus proved.  $\square$

**Theorem 4** In a bus network, the total cost,  $C_{total}$ , is minimized over all processor arrangement profiles if and only if the processors are arranged to satisfy the following condition:

$$c_1^p w_1 \le c_2^p w_2 \le \dots \le c_N^p w_N$$

**Proof**

Assume that  $c_j^p w_j$  are not all identical.

The "only if" part  $(\Rightarrow)$ : By contradiction, suppose that the processors are arranged in such a way that  $C_{total}$  is minimized over all processor arrangement profiles and there exists at least one adjacent pair of processors in that arrangement such that  $c_j^p w_j > c_{j+1}^p w_{j+1}$ . Then by lemma 6 there exists another processor arrangement with a lower total cost by swapping processor j and (j+1). This contradicts the hypothesis that  $C_{total}$  is minimal. Therefore the  $(\Rightarrow)$  is proved.

The "if" part ( $\Leftarrow$ ): If the processors are arranged such that for every adjacent pair  $c_j^p w_j \leq c_{j+1}^p w_{j+1}$ , then by lemma 7 there is no other processor arrangement that can lower the total cost further. Thus,  $C_{total}$  of such an arrangement is indeed minimal.

The theorem is then proved.  $\Box$

## 5.2 The Related Networks

In this subsection, a single-level tree network with identical processors and a homogeneous single-level tree network are investigated.

**Lemma 8** In a single-level tree network where all processors have the same computing speeds, the total cost of a current processor arrangement,  $C_{total}$ , is less than or equal to (greater than) that of an associated swapped processor arrangement,  $C'_{total}$ , if, for the current processor arrangement,

$$c_j^p \le (>) c_{j+1}^p$$

## Proof

Since  $w_j = w_{j+1}$ , therefore  $(z_{j+1} - z_j)(w_j - w_{j+1}) = 0$ . For the case  $C'_{total} > C_{total}$ , from condition 1 of theorem 1,2 one has,

$$z_{j+1}(c_{j+1}^{p}w_{j+1} - c_{j}^{p}w_{j}) \geq 0$$

$$c_{j}^{p} \leq c_{j+1}^{p}$$

Similarly for the case of  $C_{total} > C'_{total}$  if one uses condition 1 of theorem 3. The lemma is thus proved.  $\square$

**Lemma 9** In a single-level tree network where all processors have the same computing speeds, if the processors are arranged such that for every adjacent pair of processors the condition  $c_j^p \leq c_{j+1}^p$  is satisfied, then there is no other processor arrangement profile with a lower total cost.

## Proof

By contradiction, assume that an underlying processor arrangement profile  $\pi$  is arranged such that for every adjacent pair the condition  $c_j^p \leq c_{j+1}^p$  holds, and there exists another processor arrangement profile  $\pi'$ , a permutation of  $\pi$ , that has at least one adjacent pair of processors with a condition  $c_j^p > c_{j+1}^p$  which gives a lower total cost than  $\pi$ . By lemma 8, a total cost of  $\pi'$  can be decreased by swapping a pair of processors with the condition  $c_j^p > c_{j+1}^p$ . Lemma 8 can then be applied recursively to the resulting processor arrangement profile as far as it has such an adjacent pair of processors with the condition  $c_j^p > c_{j+1}^p$ . The total cost of the current processor arrangement profile is decreased each time lemma 8 is applied. Finally,  $\pi$  is reached from  $\pi'$  through a series of lemma 8 applications. Therefore a total cost of  $\pi$  is lower than that of  $\pi'$ . This contradicts the hypothesis that  $\pi'$  gives a lower total cost that  $\pi$ . The lemma is thus proved.  $\square$

**Theorem 5** In a single-level tree network where all processors have the same computing speeds, the total cost,  $C_{total}$ , is minimized over all processor arrangement profiles if and only if the processors are arranged to satisfy the following condition:

$$c_1^p \le c_2^p \le \dots \le c_N^p$$

## Proof

Assume that  $c_j^p$  are not all identical.

The "only if" part ( $\Rightarrow$ ): By contradiction, suppose that the processors are arranged in such a way that  $C_{total}$  is minimized over all processor arrangement profiles and there exists at least one adjacent pair of processors in that arrangement such that  $c_j^p > c_{j+1}^p$ . Then by lemma 8 there exists another processor arrangement with a lower total cost by swapping processor j and (j+1). This contradicts the hypothesis that  $C_{total}$  is minimal. Therefore the  $(\Rightarrow)$  is proven.

The "if" part ( $\Leftarrow$ ): If the processors are arranged such that for every adjacent pair  $c_j^p \leq c_{j+1}^p$ , then by lemma 9 there is no other processor arrangement which can lower the total cost further. Thus,  $C_{total}$  of such an arrangement is indeed minimal.

The theorem is thus proved.  $\Box$

**Lemma 10** In a homogeneous single-level tree network where all the link speeds and the processor speeds are the same, the total cost of a current processor arrangement,  $C_{total}$ , is less than or equal to (greater than) that of an associated swapped processor arrangement,  $C'_{total}$ , if, for the current

processor arrangement,

$$c_i^p \le (>)c_{i+1}^p$$

## Proof

Since  $w_j = w_{j+1}$  and  $z_j = z_{j+1}$ , therefore  $(z_{j+1} - z_j)(w_j - w_{j+1}) = 0$ . For the case  $C'_{total} > C_{total}$ , from condition 1 of theorem 1,2 one has,

$$z_{j+1}(c_{j+1}^p w_{j+1} - c_j^p w_j) \ge 0$$

$c_j^p \le c_{j+1}^p$

Similarly for the case of  $C_{total} > C'_{total}$  if one uses condition 1 of theorem 3. The lemma is thus proved.  $\Box$

**Lemma 11** In a homogeneous single-level tree network where all the link speeds and the processor speeds are the same, if the processors are arranged such that for every adjacent pair of processors the condition  $c_j^p \leq c_{j+1}^p$  is satisfied, then there is no other processor arrangement profile with a lower total cost.

## **Proof**

The proof is similar to the one in lemma 9 except one uses lemma 10 instead of lemma 8. □

**Theorem 6** In a homogeneous single-level tree network, where all the link and processor speeds are the same, the total cost,  $C_{total}$ , is minimized over all processor arrangement profiles if and only if the processors are arranged to satisfy the following condition:

$$c_1^p \le c_2^p \le \dots \le c_N^p$$

## **Proof**

This is a special case of theorem 5. The proof is similar to the one for theorem 5 except one uses lemma 10 instead of lemma 8 and lemma 11 instead of lemma 9. □

## 6 Analysis Remarks

It should be noted that in a general single-level tree network, as is evident from theorem 1-3 there is no simple condition to check for an optimal total cost processor arrangement. This is due to the fact that there are several interrelated conditions when  $C_{total}$  is compared to  $C'_{total}$ . There may exist two processor arrangements with all adjacent pair conditions compliant to theorem 1 or 2 such that one cannot simply tell which arrangement yields a lower total cost or whether they both are optimal. However, if special

cases of a single-level tree network are considered as shown in section 5, simple optimal conditions for a processor arrangement can be established as indicated in theorem 4, 5, and 6.

The analysis of a processor arrangement in a general single-level tree network, even though it may not provide a simple check for optimality, sheds light on the derivation of the conditions for the optimal processor arrangement in the special case networks. In addition, it is useful, through the use of theorem 1-3, to identify an adjacent processor pair that could be rearranged to reduce total cost in the process of searching for the optimal processor arrangement in a general single-level tree network. This makes the cost efficient processor arrangement algorithm to be discussed appealing in terms of its simplicity, complexity, feasibility, and monotonic improvement of its solutions.

In the case of a bus network as indicated by theorem 4,  $C_{total}$  is minimized over all processor arrangement profiles if and only if the processor costs,  $c_i^p w_i$ , are ordered in a non-decreasing maner. This is exactly the optimality condition found in [8]. Therein the authors use a sequencing with an adjacent pairwise swapping to find a sequence of load distribution with a minimum total cost. This is because in a bus network where all link speeds

are identical and link costs have the same values, to do sequencing, i.e. a logical interchange of the processors, is equivalent to the problem of processor arrangement, a physical interchange of the processors, of this paper.

For a single-level tree network where all processors have the same computing speeds,  $C_{total}$  is minimized over all processor arrangement profiles when the processor cost coefficients,  $c_i^p$ , are ordered in a non-decreasing maner. This can be explained as follows. The root processor always distributes fractions of load through  $l_1, l_2, ..., l_N$  sequentially in this order no matter which processor is attached to which link. Since  $w_j = w_{j+1}$  for all j=1 to N-1, the closed-form expression of  $\alpha_i$  is indepedent of the processor arrangement; consequently the communication time is unchanged due to processor arrangements as well. Moreover  $\alpha_1 > \alpha_2 > ... > \alpha_N$ . Note that in this case  $\frac{\alpha_i}{\alpha_{i+1}} = \frac{(z_{i+1}T_{cm} + wT_{cp})}{wT_{cp}} > 1$ . In order to minimize the total cost the processor with the lowest processor cost coefficient should receive the largest fraction of load  $(\alpha_1)$  and the next lowest processor cost coefficient processor receive the next largest fraction of load  $(\alpha_2)$  and so on.

Similarly for the case of a homogeneous single-level tree network which is a special case of the single-level tree where all of processors have the same speed, the total cost,  $C_{total}$ , is minimized over all processor arrangement pro-

files when the processor cost coefficients,  $c_i^{p_i}s$ , are ordered in a non-decreasing maner.

Note that in our analysis, the processor arrangement does not involve the root processor. It consists only of an arrangement of the children processors.

## 7 Heuristic Processor Arrangement Algorithm

In this section, a discussion of the performance of two basic greedy algorithms for processor arrangement is presented. A heuristic algorithm for processor arrangement, which is a modified version of the two basic algorithms, is proposed so as to improve the performance. This algorithm uses several starting points in order to produce a final solution. The mechanism to generate a new processor arrangement profile,  $\pi'$ , is no longer restricted to an adjacent pairwise processor swapping as in the case of sequencing of [7]. It extends to cover the cases of swapping two processors which are two positions apart, three positions apart and so on. Finally an exhaustive permutation algorithm is presented which serves as a tool to obtain globally optimal solutions for testing purposes.

# 7.1 Two Basic Greedy Processor Arrangement Algorithms