### **Stony Brook University**

## OFFICIAL COPY

The official electronic file of this thesis or dissertation is maintained by the University Libraries on behalf of The Graduate School at Stony Brook University.

© All Rights Reserved by Author.

# Electron Transport Through Aluminum Oxide Tunnel Barriers and OPE-Based Molecular Junctions

A Dissertation Presented

by

#### Xueqing Liu

to

The Graduate School

in Partial Fulfillment of the Requirements

for the Degree of

### Doctor of Philosophy

in

**Physics**

Stony Brook University

August 2007

#### Stony Brook University

The Graduate School

#### Xueqing Liu

We, the dissertation committee for the above candidate for the Doctor of Philosophy degree, hereby recommend acceptance of this dissertation.

> Konstantin K. Likharev – Dissertation Advisor Professor, Department of Physics and Astronomy

> Chris J. Jacobsen – Chairperson of Defense Professor, Department of Physics and Astronomy

> James E. Lukens Professor, Department of Physics and Astronomy

> > Andreas Mayr Professor Department of Chemistry

This dissertation is accepted by the Graduate School.

Lawrence Martin Dean of the Graduate School

#### Abstract of the Dissertation

#### Electron Transport Through Aluminum Oxide Tunnel Barriers and OPE-Based Molecular Junctions

by

#### Xueqing Liu

**Doctor of Philosophy**

in

#### **Physics**

Stony Brook University

2007

This work presents results of a study of electron transport through aluminum-oxide based tunnel barriers and single-molecule transistors. Both systems have the potential for a dramatic increase of the density and performance of integrated circuits with critical dimensions well below the scaling limits of the conventional semi-conductor technology. Studies of these two systems are also united by a common experimental approach - measurement of very small (down to  $10^{-14}$  A) currents within a broad temperature range (from 4.2 K to 350 K).

Transport properties of  $(Nb/)Al/AlO_x/Nb$  tunnel barriers have been studied for structures formed by (i) thermal oxidation and (ii) plasma oxidation, before and after their rapid thermal post-annealing at temperatures up to 650°C. The post-annealing results in a substantial increase of the barrier height of the thermally formed aluminum oxide, which (within a broad range of RTA temperatures) may be substantially higher than that of the plasma-

grown  $AlO_x$  barriers. This fact, together with high endurance of annealed barriers under electric stress, may eventually lead to the fabrication of  $AlO_x$  and  $SiO_2$  /  $AlO_x$  layered ("crested") barriers for advanced floating-gate memories.

Electron transport through single molecular devices has been studied for structures of three types: (i) co-planar Au electrodes with 5-nm-scale gaps formed by e-beam lithography, (ii) co-planar Au electrodes with 1 - 2 nm-scale gaps formed by electromigration, and (iii) nanowires crosspoints with vertical gaps of 3 to 5 nm formed by under-etched aluminum oxide layers. Two types of Oligo(Phenylene Ethynylene) based molecules (with or without naphthalene diimide groups working as acceptors), capped with iso-cyanide terminal groups, have been investigated. For both molecules, nonlinear current-voltage curves with discrete current steps, due to tunneling through one or a few molecules, have been observed, and their dependences on the gate voltage and temperature have been studied in detail.

Key Words: electron transport, aluminum oxide, crested barrier, rapid thermal annealing, single-electron transistor, electromigration, molecular junction.

### Contents

| Li            | st of                | Figur  | es                                                               | viii |

|---------------|----------------------|--------|------------------------------------------------------------------|------|

| $\mathbf{Li}$ | st of                | Table  | S                                                                | xi   |

|               | Ack                  | nowle  | dgements                                                         | xii  |

| 1             | Intr                 | oduct  | ion                                                              | 1    |

| 2             | $\operatorname{Cre}$ | sted T | unnel Barrier: Simulation and Barrier Engineering                | 5    |

|               | 2.1                  | Opera  | ting Principle in Flash Memory                                   | 5    |

|               | 2.2                  | What   | 's a Crested Tunnel Barrier                                      | 6    |

|               | 2.3                  | Calcu  | lation of Tunneling Current Through Metal-Insulator-Metal        |      |

|               |                      | Juncti | ions                                                             | 9    |

|               | 2.4                  | Trans  | mission Coefficients                                             | 11   |

|               | 2.5                  | Select | ion of Barrier Parameters                                        | 13   |

| 3             | Tra                  | nsport | Through ${\rm AlO_x}$ - based Tunnel Barriers                    | 16   |

|               | 3.1                  | Backg  | round                                                            | 16   |

|               | 3.2                  | Sampl  | e Fabrication                                                    | 17   |

|               |                      | 3.2.1  | Thermally/Plasma Grown AlO <sub>x</sub> as Single-Layer Barriers | 17   |

|               |                      | 3.2.2  | Thermally/Plasma Grown AlO <sub>x</sub> as Double-layered Bar-   |      |

|               |                      |        | riers                                                            | 19   |

|               | 3.3                  | Post I | Fabrication - Rapid Thermal Annealing                            | 20   |

|               | 3.4                  | HR-T   | EM Characterization of AlO <sub>x</sub> Structures               | 22   |

|               |                      | 3.4.1  | Thermally Grown Aluminum Oxide                                   | 22   |

|               |                      | 3.4.2  | Plasma Oxidized Aluminum Oxide                                   | 25   |

|               | 3.5                  | Electr | ical Characterization for $(Nb/)Al/AlO_x/Nb$ Barriers            | 25   |

|               |                      | 3.5.1  | $TO - AlO_x$ with Different Oxygen Exposures                     | 29   |

|               |                      | 3.5.2  | Annealing Effects on $TO - AlO_x$ Layers                         | 31   |

|               |                      | 3.5.3  | $PO-AlO_x$ with Different Oxygen Exposure and Power              | 35   |

|               |                      | 3.5.4  | Annealing Effects on $PO - AlO_x$ Layers                         | 38   |

|   | 3.6<br>3.7<br>3.8    | 3.5.5 Discussion: Formation of Aluminum Oxide Simulation Results          | 41<br>41<br>46<br>49 |

|---|----------------------|---------------------------------------------------------------------------|----------------------|

| 4 | Elec                 | ctron Transport in Single-molecule Devices                                | 50                   |

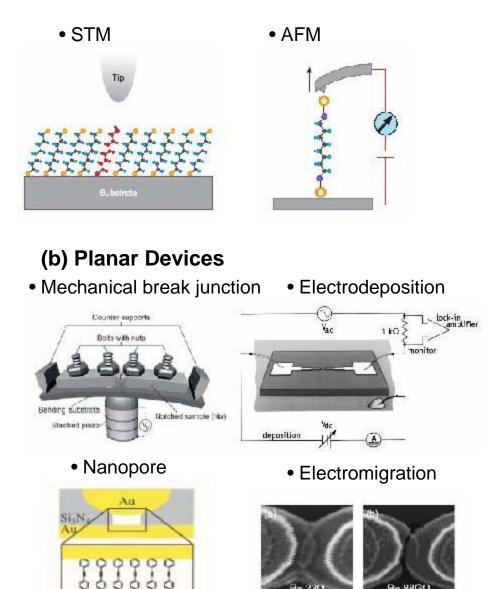

| • | 4.1                  | Introduction to Single-molecule Devices                                   | 50                   |

|   | 4.2                  | Fabrication Methods of Single Molecule Junctions                          | 53                   |

|   | 4.3                  | Basic Concepts in Single-electron Transport Theory                        | 55                   |

|   | 4.4                  | Interesting Molecules                                                     | 60                   |

|   | 1.1                  | 4.4.1 Alkane Chains                                                       | 60                   |

|   |                      | 4.4.2 Oligo(Phenylene-Ethylene)s and Their Derivatives                    | 61                   |

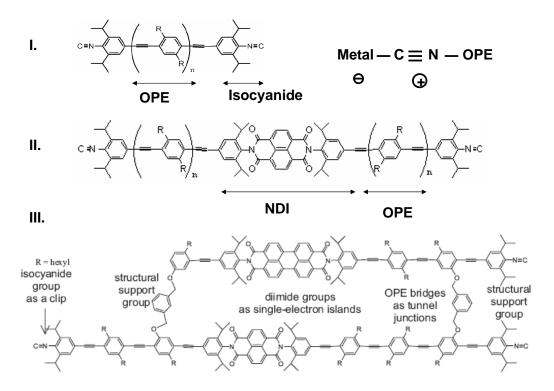

|   |                      | 4.4.3 Mayr's Molecules                                                    | 62                   |

| 5 | Mo                   | lecular Junctions Based on Co-planar Gaps                                 | 65                   |

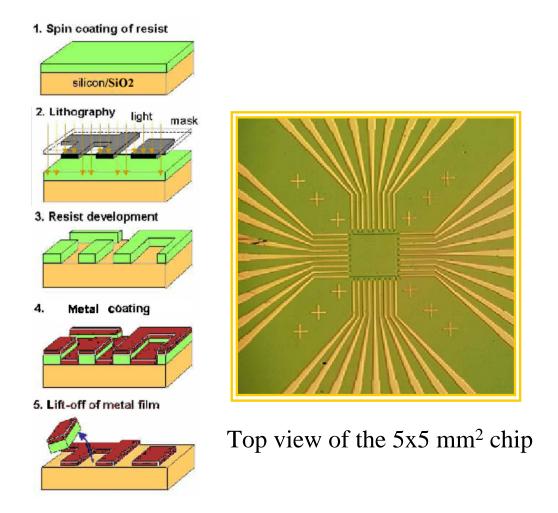

|   | 5.1                  | Fabrication of Nanogap by E-beam Lithography                              | 65                   |

|   | 5.2                  | Molecular Deposition Method                                               | 66                   |

|   | 5.3                  | Electrical Characterization and Discussion                                | 66                   |

| 6 | Mo                   | lecular Junctions Formed by Electromigration                              | 72                   |

|   | 6.1                  | Introduction                                                              | 72                   |

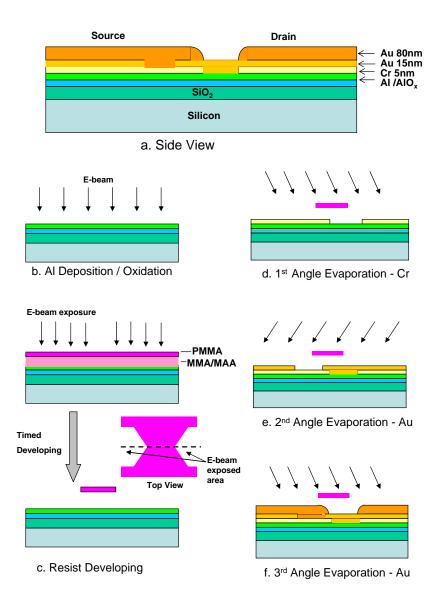

|   | 6.2                  | Fabrication of Au-nanowire Junctions                                      | 73                   |

|   | 6.3                  | Electromigration in Gold Nanowires                                        | 77                   |

|   | 6.4                  | Electrical Characterization                                               | 80                   |

|   |                      | 6.4.1 Control Experiment - No Molecules                                   | 82                   |

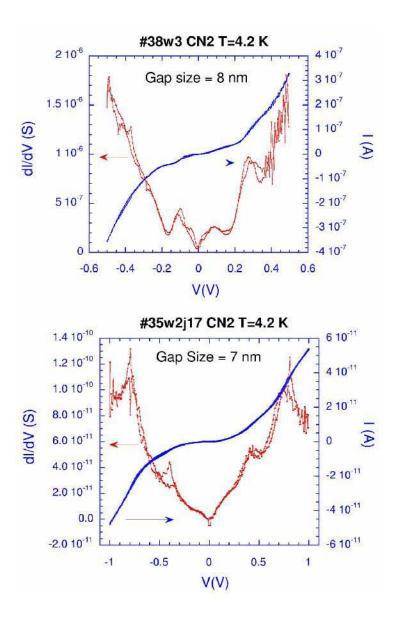

|   |                      | 6.4.2 Oligo(phenylene-ehtynylene)s with Naphthalenediimide                |                      |

|   |                      | Group                                                                     | 87                   |

|   |                      | 6.4.3 Oligo(phenylene-ethynylene) Chains                                  | 92                   |

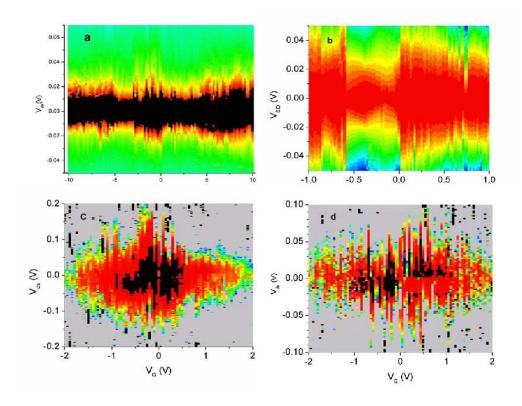

|   | 6.5                  | Effect of Gate Modulation                                                 | 97                   |

|   | 6.6                  | Temperature Effect                                                        | 105                  |

|   | 6.7                  | Summary                                                                   | 108                  |

| 7 | $\operatorname{Cro}$ | •                                                                         | 109                  |

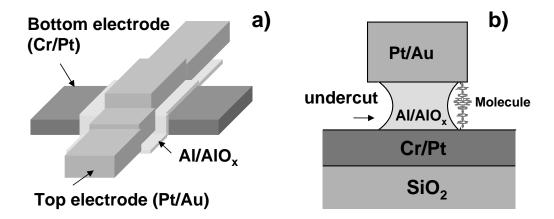

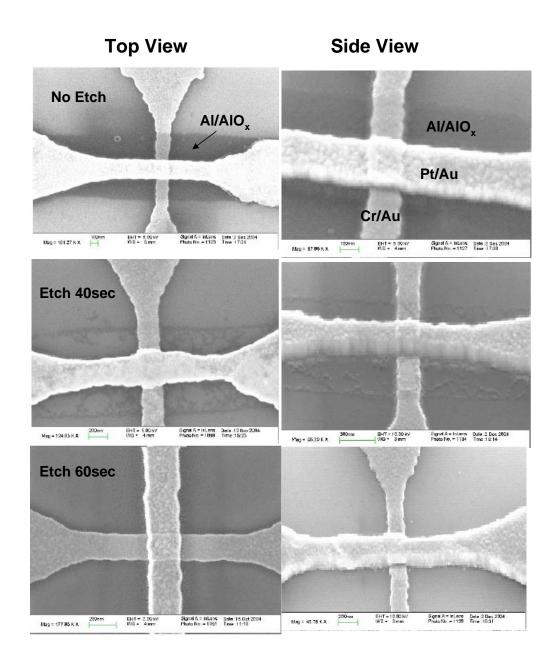

|   | 7.1                  | Device Fabrication and Sample Preparation                                 | 109                  |

|   |                      | 7.1.1 Fabrication of Pt/Al/AlO <sub>x</sub> /Pt/Au Cross-point Structures |                      |

|   |                      | 7.1.2 Sample Preparation                                                  | 111                  |

|   | 7.2                  | TEM and AFM Characterization of Pt and Pt/Al Interface                    | 113                  |

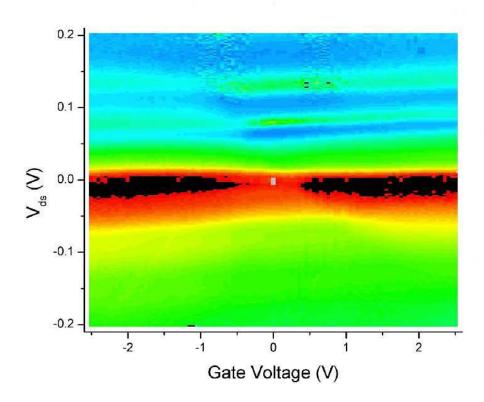

|   | 7.3                  | Electrical Measurement of OPE chains                                      | 115                  |

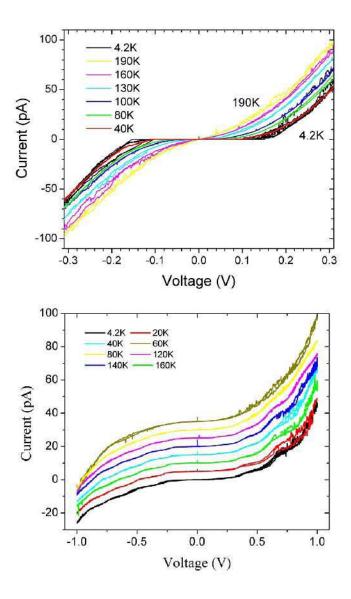

|   |                      | 7.3.1 Low Temperature $I - V$ Characteristics                             | 115                  |

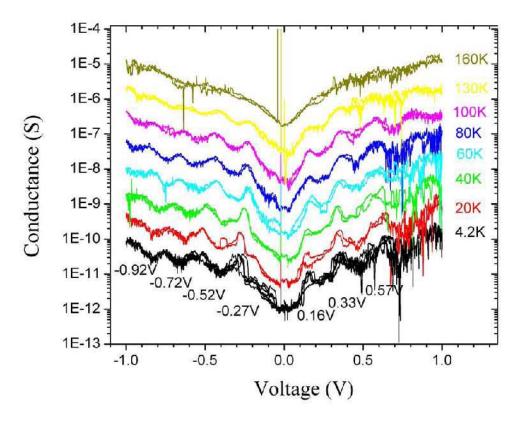

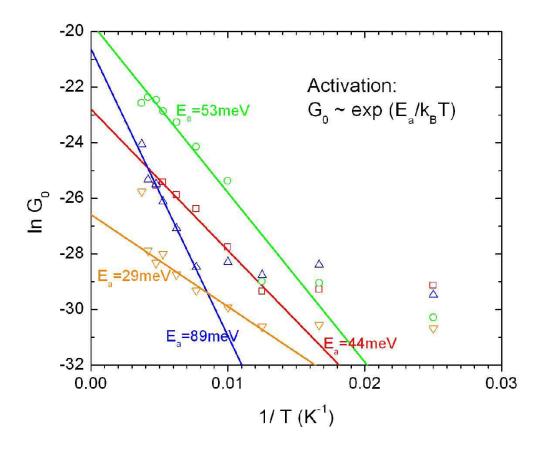

|   | <del></del> 4        | 7.3.2 Temperature Dependence                                              | 118                  |

|   | 7.4                  | Electrical Measurement of OPE-NDI Molecules                               | 125                  |

|              | 7.5 Conclusion                                          | 128 |

|--------------|---------------------------------------------------------|-----|

| 8            | Conclusion  8.1 Summary of the Crested Barriers Studies |     |

| $\mathbf{A}$ | Electrical Measurement Setup                            | 133 |

| В            | Ellipsometry Measurement for Self-assembled Molecules   | 140 |

| Bi           | ibliography                                             | 142 |

### List of Figures

| 2.1  | Schematic diagram of a floating gate memory                         | 7  |

|------|---------------------------------------------------------------------|----|

| 2.2  | Conduction band diagrams of various tunnel barriers                 | 8  |

| 2.3  | Illustration of the potential barrier as a stack of N square pieces | 12 |

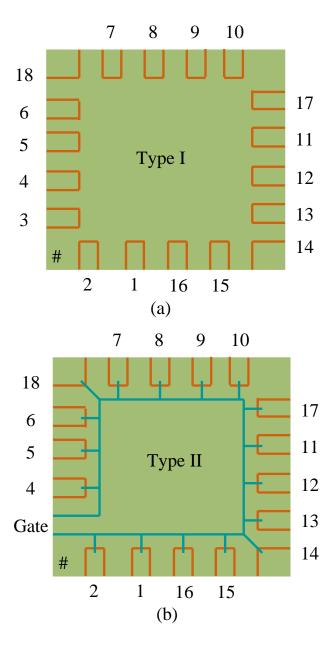

| 3.1  | Layout of the chip and wafer                                        | 20 |

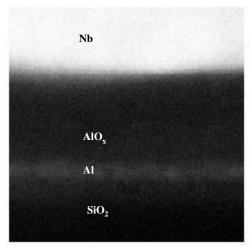

| 3.2  | High resolution TEM picture of thermally grown aluminum oxide       | 23 |

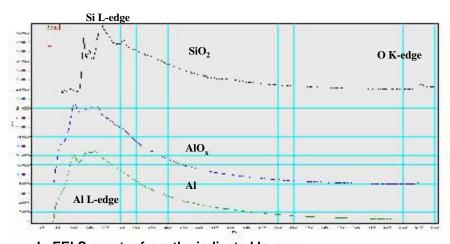

| 3.3  | EELS spectroscopy for annealed thermally grown aluminum oxide       | 24 |

| 3.4  | High resolution TEM picture of plasma-grown aluminum oxide          | 26 |

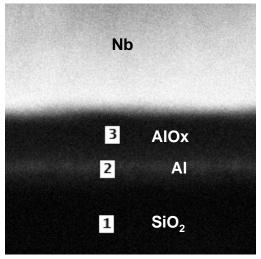

| 3.5  | Z contrast image and EELS spectroscopy of 15-mTorr-plasma           |    |

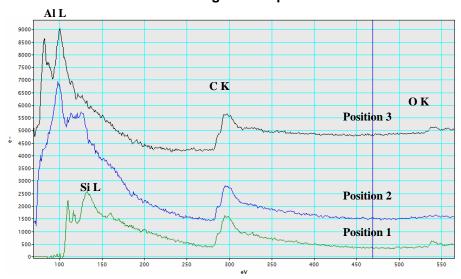

|      | oxide                                                               | 27 |

| 3.6  | Z contrast image and EELS spectroscopy of 75-mTorr-plasma           |    |

|      | oxide                                                               | 28 |

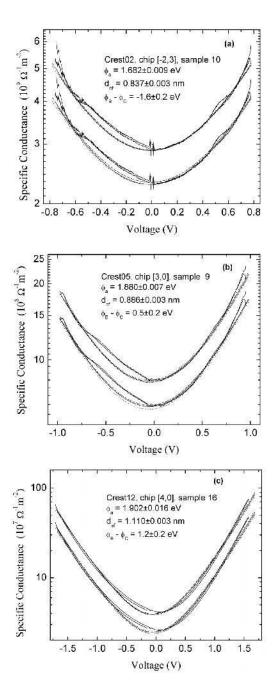

| 3.7  | Theoretical fitting results for thermally grown aluminum oxide      | 30 |

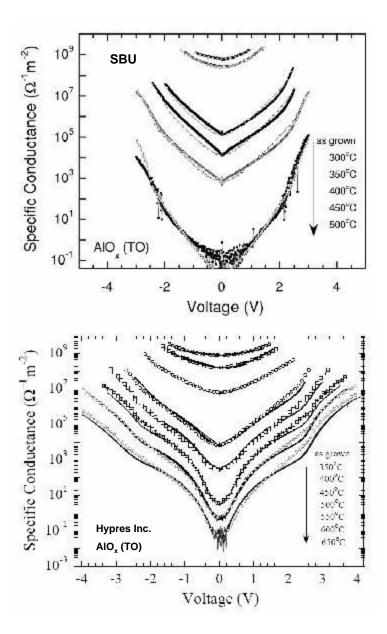

| 3.8  | Rapid thermal annealing for thermally grown aluminum oxide          | 32 |

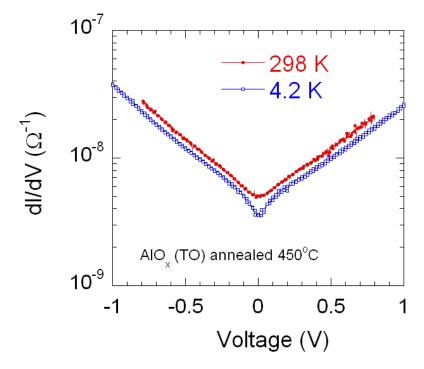

| 3.9  | Differential conductance measured at room and liquid helium         |    |

|      | temperatures for annealed "Crest 5"                                 | 33 |

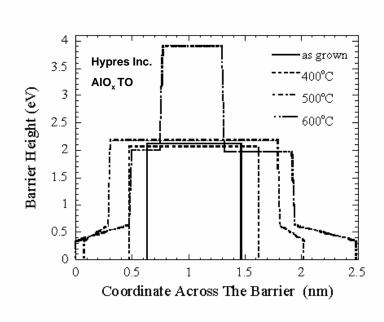

| 3.10 | Barrier profiles for a thermal oxide with various annealing tem-    |    |

|      | peratures                                                           | 36 |

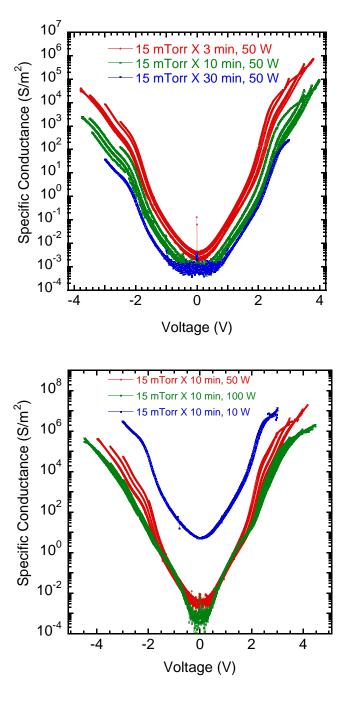

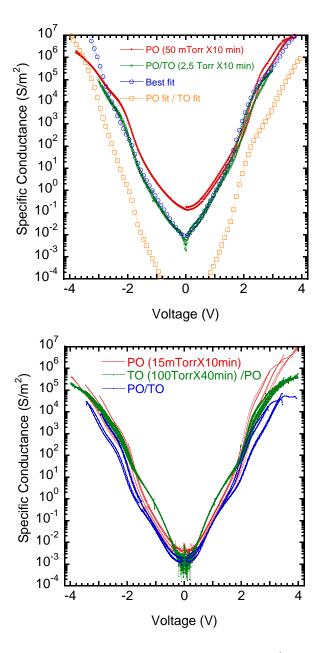

| 3.11 | Specific differential conductance for plasma oxide with various     |    |

|      | oxygen exposure conditions and rf-plasma powers                     | 37 |

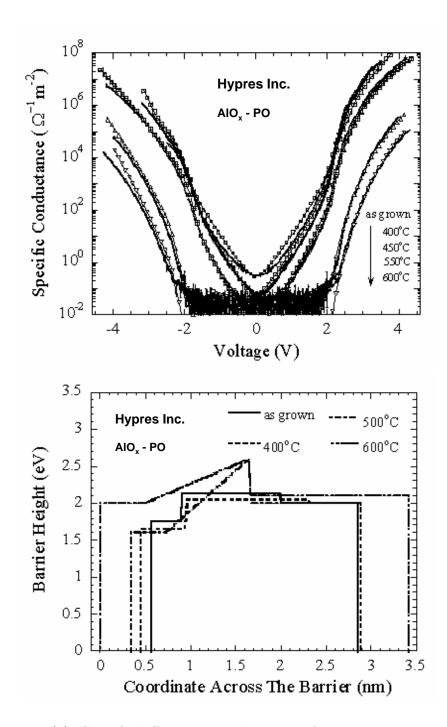

| 3.12 | Specific differential conductance of plasma-grown aluminum ox-      |    |

|      | ide at various rapid thermal annealing temperatures with fitting    |    |

|      | results                                                             | 39 |

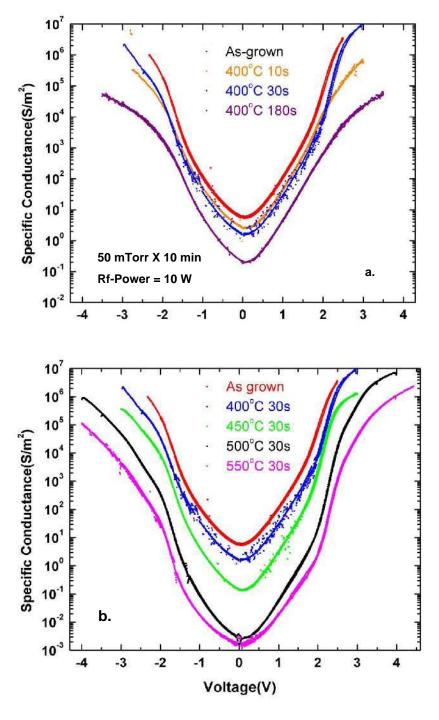

| 3.13 | Specific differential conductance of low-rf-power plasma oxide      |    |

|      | at various rapid thermal annealing conditions                       | 42 |

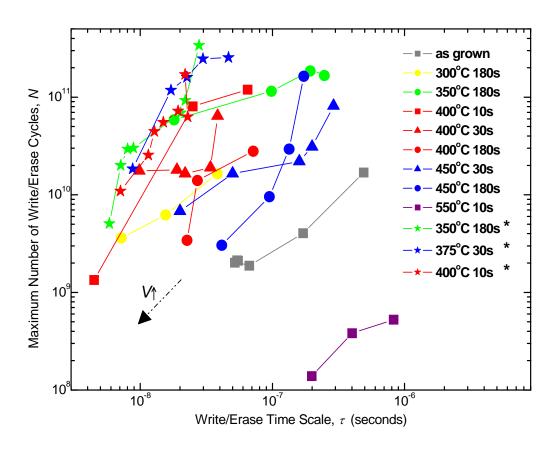

| 3.14 | Field endurance as a function of write/erase speed for low-rf-      |    |

|      | power plasma oxide                                                  | 43 |

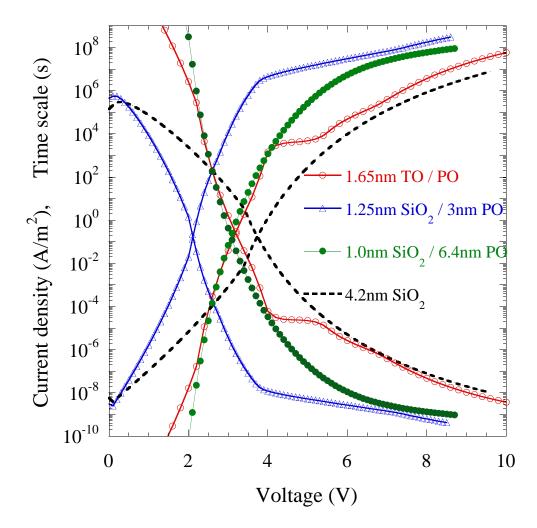

| 3.15 | Simulated current density and recharging time constant for alu-     |    |

|      | minum oxide based layered structures                                | 45 |

| 3.16 | Specific differential conductance of double-layered aluminum oxide  | 47 |

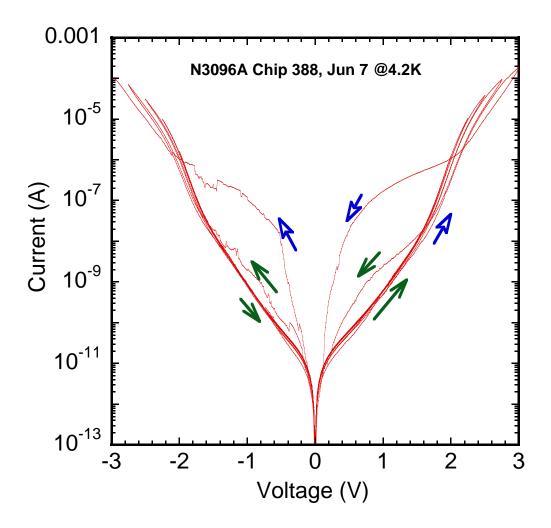

| 3.17                     | I-V plot for a double-layered tunnel junction (wafer "N3096") with switching effect.                                                                                           |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1                      | Various experimental techniques for measuring single molecule conductance.                                                                                                     |

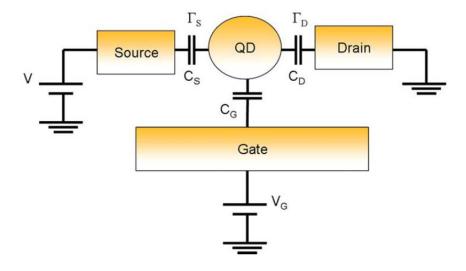

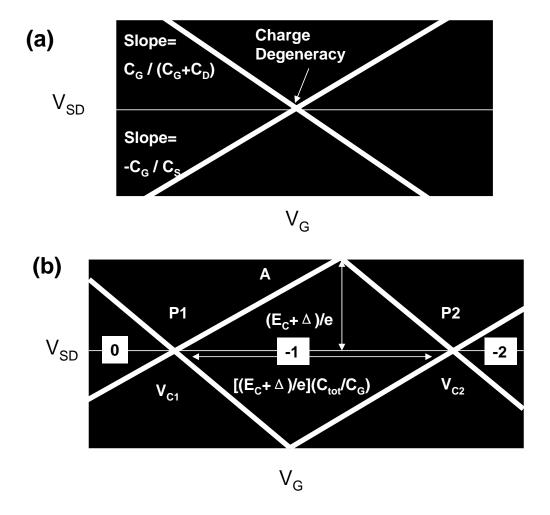

| 4.2<br>4.3<br>4.4        | Schematic diagram of a single-molecule transistor                                                                                                                              |

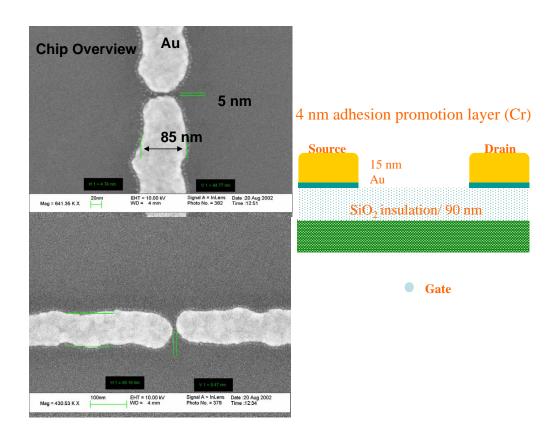

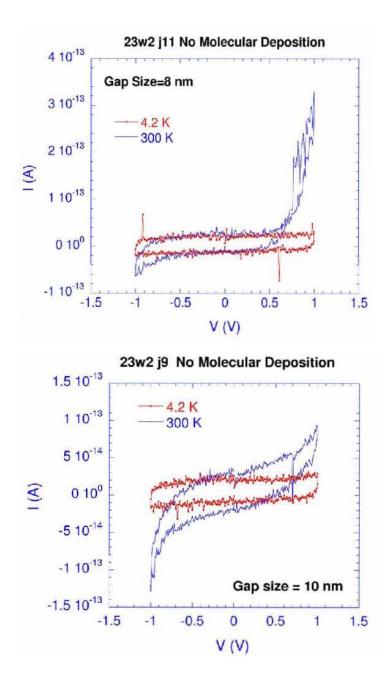

| 5.1<br>5.2<br>5.3<br>5.4 | Wafer fabrication procedures and chip top-view SEM pictures of the planer electrode gaps $I-V$ characteristics of planar support structures before the deposition of molecules |

| 6.1                      | Fabrication procedures of nanostructure for electromigration                                                                                                                   |

| 6.2                      | Wire pattern for chips with silicon or aluminum back-gate                                                                                                                      |

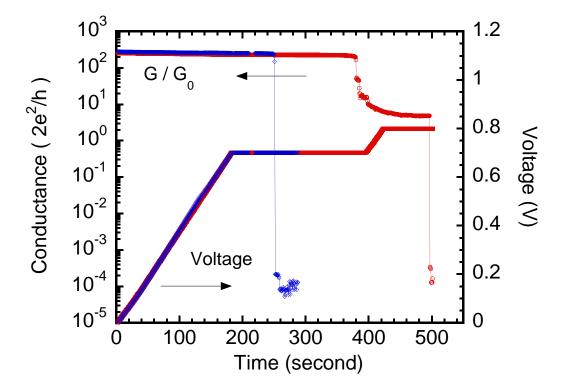

| 6.3                      | Current / conductance vs. time traces during wire-breaking .                                                                                                                   |

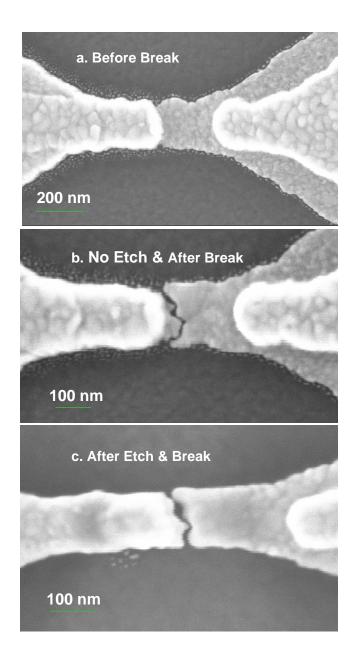

| 6.4                      | SEM pictures of electromigrated nanostructures                                                                                                                                 |

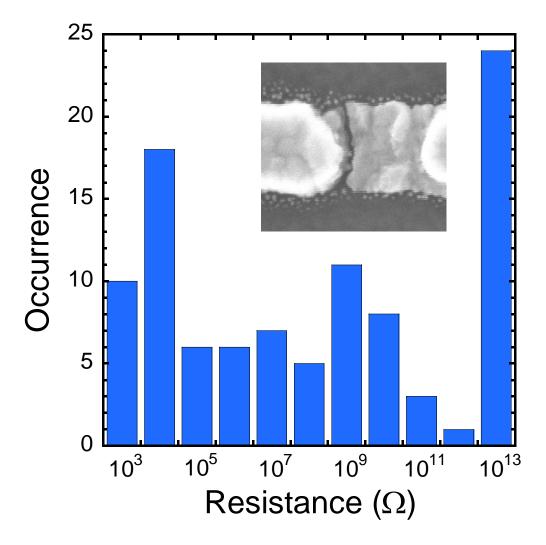

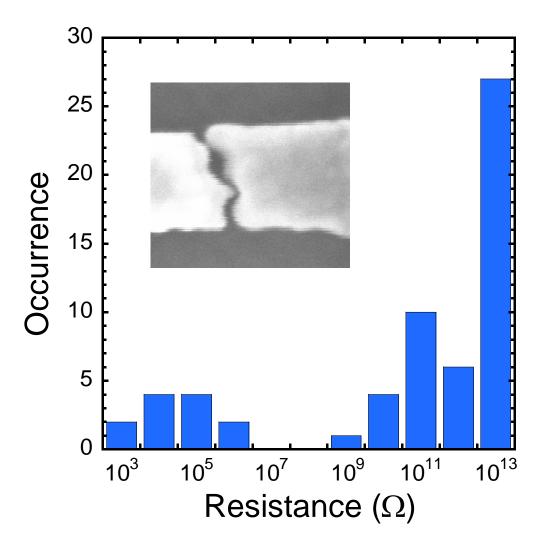

| 6.5                      | Histogram of $R_{\rm br}$ for only plasma-cleaned samples                                                                                                                      |

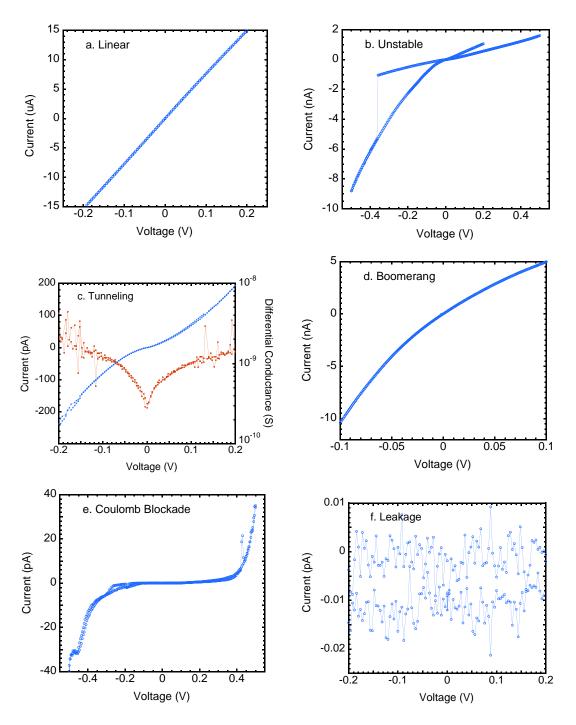

| 6.6<br>6.7               | Histogram of $R_{br}$ for samples with wet-etch treatment I-V plots for control samples without molecules                                                                      |

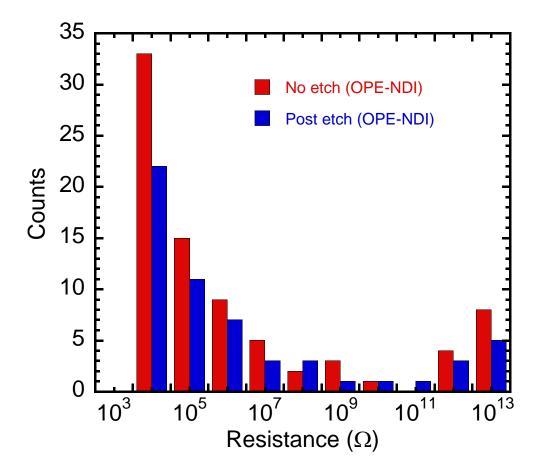

| 6.8                      | Histogram of $R_{\rm br}$ for samples with OPE-NDI molecules                                                                                                                   |

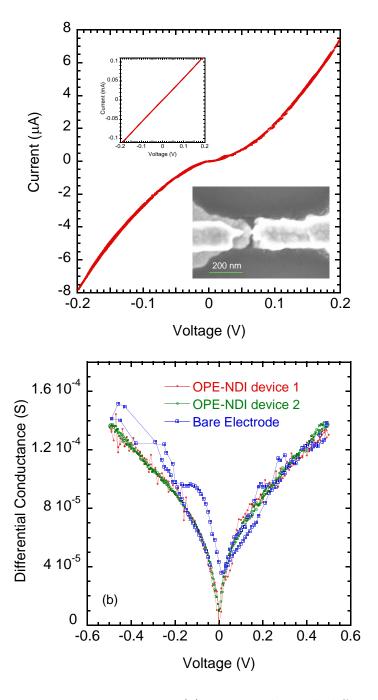

| 6.9                      | Linear $I-V$ plots for OPE-NDI devices                                                                                                                                         |

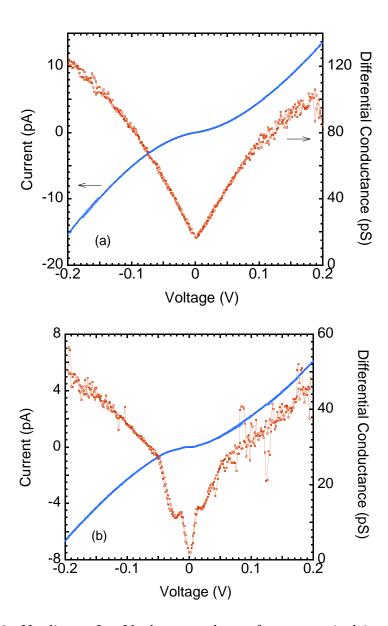

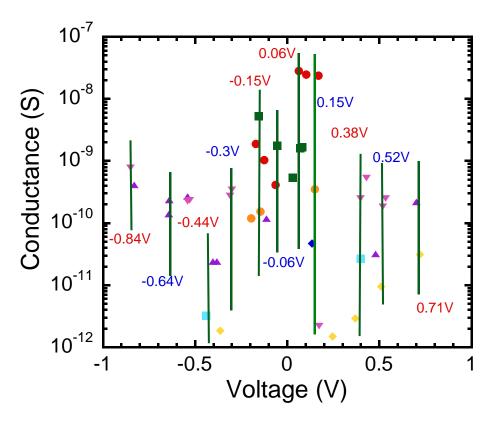

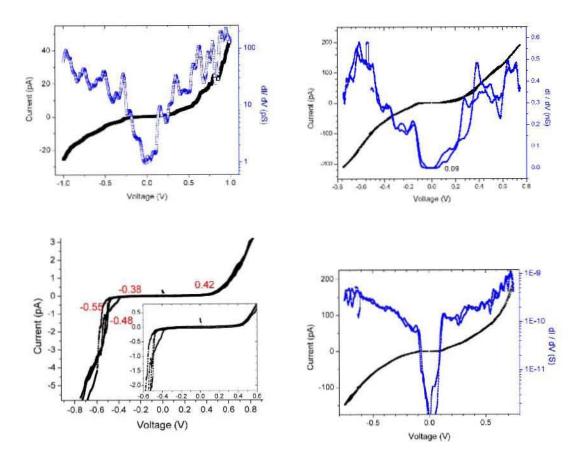

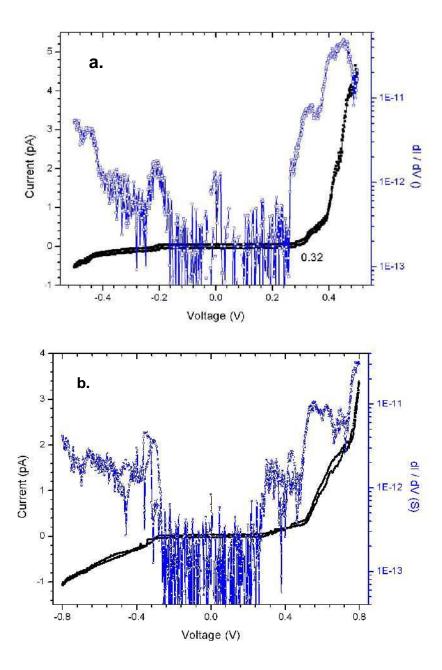

| 6.10                     | Nonlinear $I-V$ and $G-V$ plots for OPE-NDI devices                                                                                                                            |

|                          | Strongly nonlinear I-V for OPE-NDI devices                                                                                                                                     |

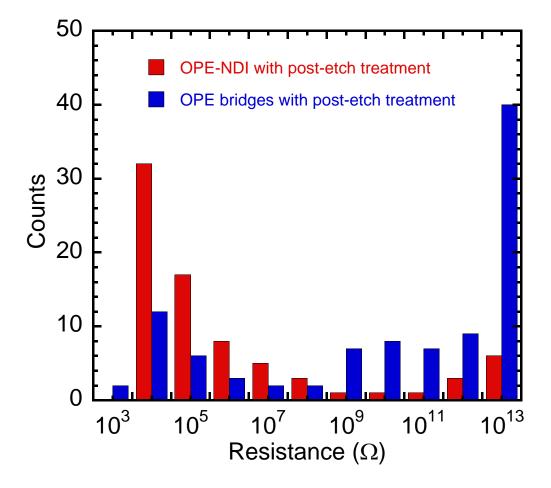

|                          | Histogram of $R_{\rm br}$ for both OPE and OPE-NDI molecules                                                                                                                   |

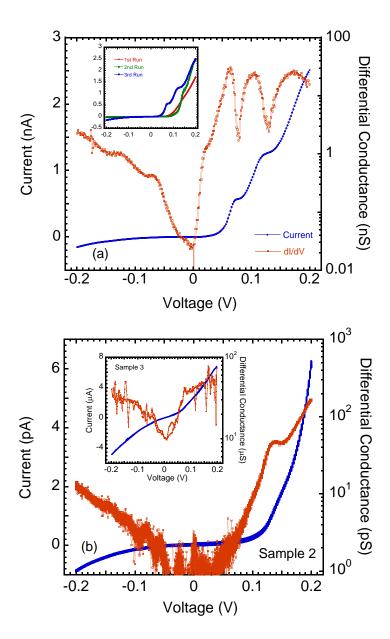

| 6.13                     | Strongly nonlinear $I - V$ for OPE devices                                                                                                                                     |

|                          | Coulomb-blokcade like $I-V$ plots for OPE devices Plot of differential conductance peak and voltage steps for OPE                                                              |

|                          | devices                                                                                                                                                                        |

| 6.16                     | No or weakly gate dependence                                                                                                                                                   |

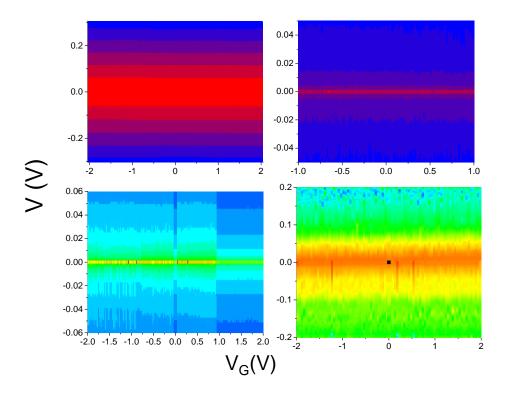

|                          | $G - V - V_G$ plots for both OPE-NDI and OPE devices 10                                                                                                                        |

|                          | $G - V - V_G$ plot for one OPE device                                                                                                                                          |

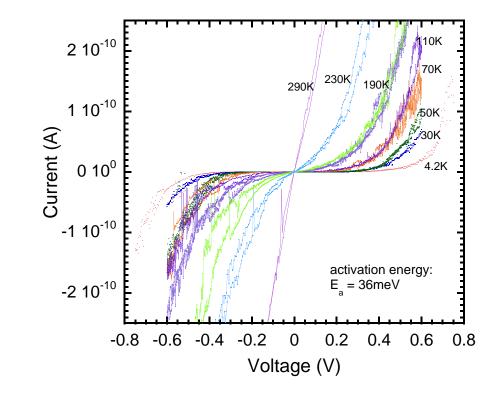

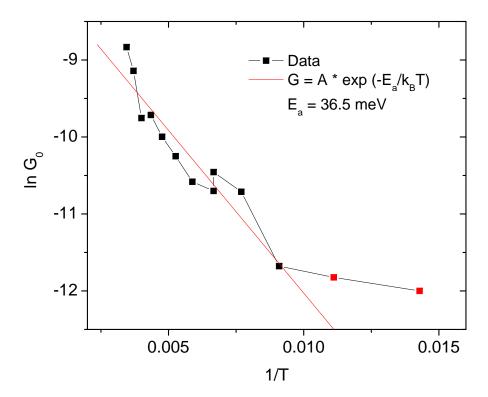

|                          | I-V characteristics under different temperatures                                                                                                                               |

| 0.20                     | Arrhenius plot of zero bias conductance for an OPE device 19                                                                                                                   |

| 7.1<br>7.2               | Geometry of the crosspoint devices                                                                                                                                             |

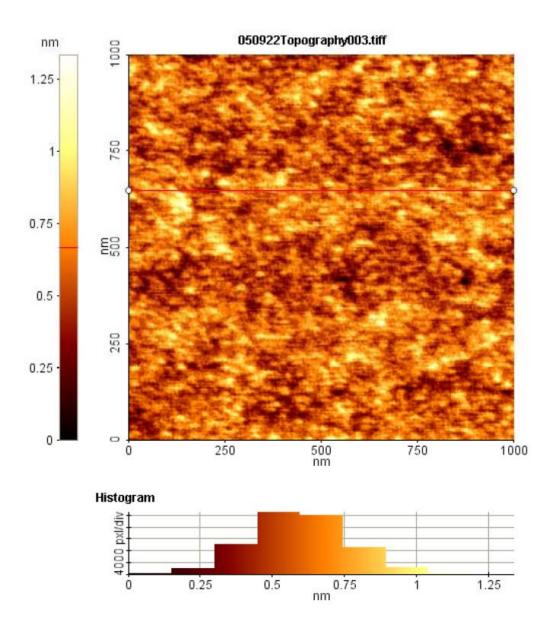

| 7.3                      | AFM image of Pt surface                                                                                                                                                        |

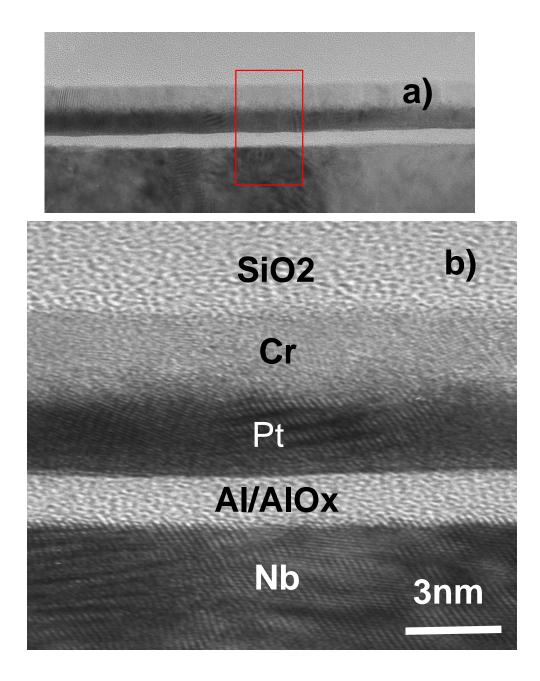

| 7.4                      | High-resolution TEM images of the test structures                                                                                                                              |

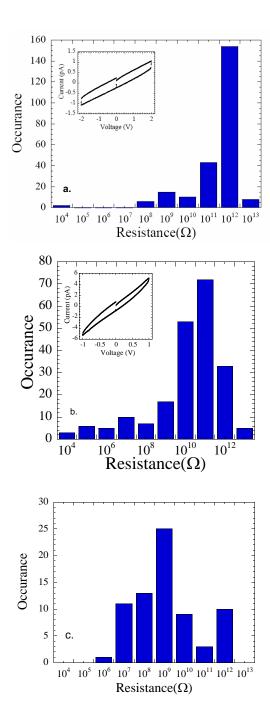

| 7.5  | Histograms of room temperature leakage resistance of the sup-   |      |

|------|-----------------------------------------------------------------|------|

|      | port structure at 50 mV bias voltage                            | 117  |

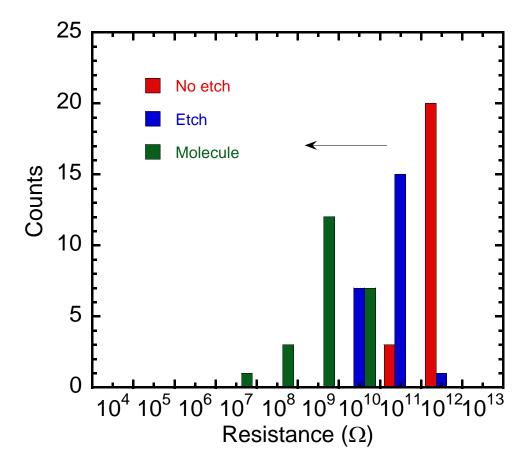

| 7.6  | Histograms of resistance of interesting devices                 | 119  |

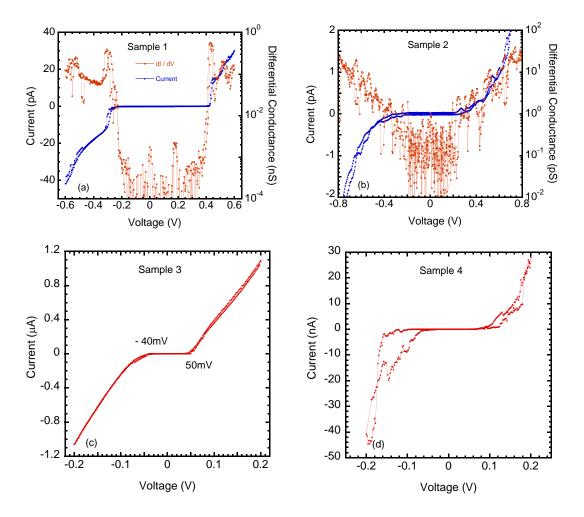

| 7.7  | DC-IV and $GV$ curves for 4 selected high resistance junctions  |      |

|      | at 4.2 K                                                        | 120  |

| 7.8  | DC-IV curves for two selected high resistance junctions at var- |      |

|      | ious temperature. For one junction, the curves are offset for   |      |

|      | clarity                                                         | 122  |

| 7.9  | Differential conductance as a function of bias voltage and tem- |      |

|      | perature T. The curves are offset for clarity                   | 123  |

| 7.10 | Arrhenius plot of the zero bias conductance for four different  |      |

|      | OPE-devices                                                     | 124  |

| 7.11 | DC-IV curves for two selected high resistance junctions (OPE-   |      |

|      | NDI) at 4.2 K                                                   | 126  |

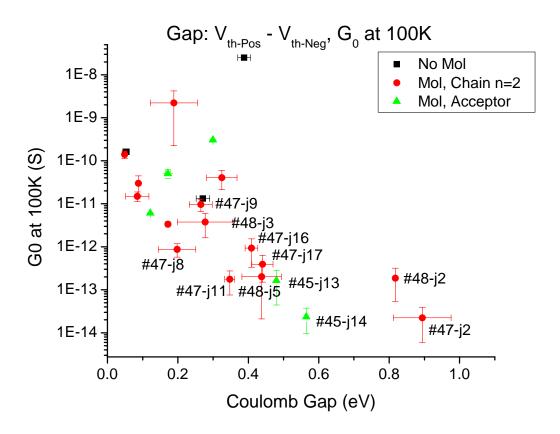

| 7.12 | Coulomb gap distribution with zero-bias conductance $\dots$     | 127  |

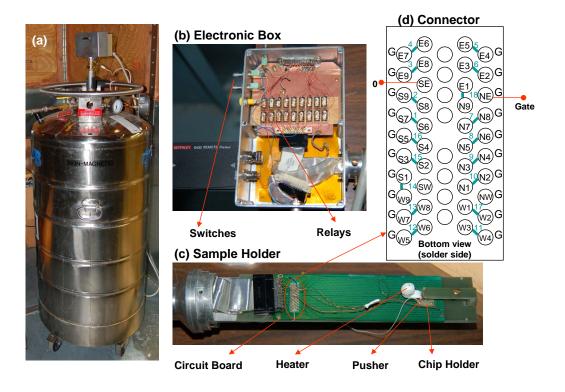

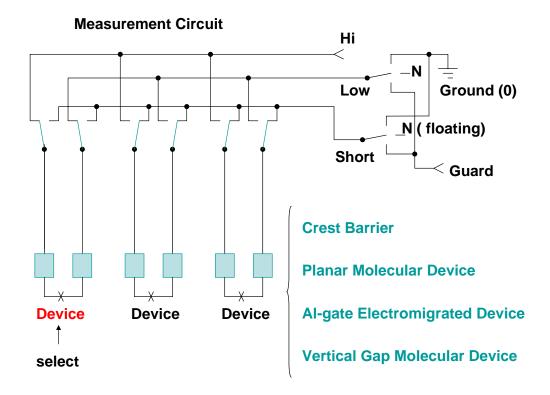

| A.1  | The actual measurement setup                                    | 134  |

| A.2  | The Schematic diagram of electronic wiring circuit              | 135  |

| A.3  | Front panel of labview program                                  | 136  |

|      | 1 0                                                             |      |

| B.1  | Two types of molecular SAM used for eliipsometry measurement    | s141 |

### List of Tables

| 2.1 | List of values of dielectric constant, band gap and conduction band offset for various dielectric materials [20] - [26]       | 14  |

|-----|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Thermal Oxidation Process Parameters                                                                                          | 18  |

| 3.2 | Plasma Oxidation Process Parameters                                                                                           | 18  |

| 3.3 | Processing parameters of PO / TO double-layer aluminum oxide tunnel barriers                                                  | 21  |

| 6.1 | Summary of experimental results on single molecular transistors                                                               |     |

|     | by electromigration methods [171]                                                                                             | 74  |

| 6.2 | Summary of the fabrication information of all the wafers fabri-                                                               |     |

|     | cated for electromigration                                                                                                    | 75  |

| 6.3 | Summary of low-temperature $I-V$ characteristics of all electromigrated junctions. Each category of $I-V$ displays the number |     |

|     | of junctions in this range, as well as the percentage rate. $\ . \ . \ .$                                                     | 95  |

| 7.1 | Aluminum sputtering conditions                                                                                                | 111 |

| 7.2 | Wafer fabrication information                                                                                                 | 111 |

| B.1 | Ellipsometry measurement of OPE SAMs                                                                                          | 141 |

### Acknowledgements

First and foremost, I would like to express my profound gratitude to my advisor, Prof. Konstantin K. Likharev, for his advice, extensive support and guidance toward my Ph. D. degree. He taught me not only the way to do scientific research, but also the way to become a professional scientist. He is a lifetime role model for me. Without his encouragement and support, none of the work presented here would have been possible.

My graduate studies at Stony Brook has been greatly enriched by the wonderful condensed matter physics group. I am deeply indebted to Dr. Yuri Polyakov for all these years of crucial support on measurement techniques and for sharing his marvelous expertise on electronics. I am very grateful to Dr. Wei Chen for his extensive knowledge in nanofabrication and generous support on wafer fabrication and SEM imaging for molecular junctions. I also thank Dr. Vijay Patel and Dr. Sergey K. Tolpygo for their continuous effort on fabrication of aluminum oxide films, Dr. Elena Cimpoiasu for many fruitful discussions and great collaboration. I especially thank Prof. Andreas Mayr for his encouragement, advice and tremendous synthetic support of all kinds of molecules. Further, I would also like to thank my dissertation committee for their time, patience and invaluable advices. It is my pleasure to have gotten to know such outstanding scientists as Prof. Chris J. Jacobsen and Prof. James E. Lukens.

I would like to thank X. Wang for her kind help on RTA at Yale University, L. Zhang, R. Klie, Y. M. Zhu for their constant support on TEM imaging at the Brookhaven National Lab, and Y. Sun, M. Rafailovich for their technical expertise on Langmuir Blodgett film depositon at the Department of Material Science at Stony Brook. I thank Pete Davis for his never ending supply of liquid helium, Bent Nielsen for his help and kindness, and Pernille Jensen for her help and support on administrative issues.

I benefited much from discussions with Nikita Simonian, Jingbin Li, Dmitri Strukov who generously share their insights. I thank Zhongkui Tan for his dedicated work and collaboration. I learned a great deal from my friends Radu Ionas, Flaminia Talos, Moustapha Thioye, A. K. M. Newaz, Diyar Talbayev,

Xiyue Miao, Tianshi Lu, Haijiang Gong, Robert Richter, Stella Christie, Bartlomiej Czech. I will miss you guys.

Last and most, words can not express my gratitude towards my parents and my beloved husband Peng. Their enormous love and unlimited support through the years have made my life a joy and kept me focused on my interest. Without my dear husband Peng, I could never have been able to accomplish the work as torturing as writing a thesis. This dissertation is as much theirs as it is mine.

### Chapter 1

### Introduction

The field of semiconductor electronics has been the most significant technological advance of the past half century. Since the introduction of the integrated circuit in the late 1950s, the number of individual transistors that can be placed on a single integrated circuit chip has approximately doubled in every 18 months (as first pointed out by Gordon E. Moore of Intel, so this trend has been dubbed Moore's Law). The demand for higher computing power and larger data storage capacity has been the driving force in the past decades for more advanced chip technology. Fundamentally, the integrated circuit (IC) industry has employed the "top-down" approach, in which the devices are fabricated by processes such as optical Si lithography, doping thin-fim deposition, etching and metallization. The key advantage is that the parts are both patterned and built in place so that no assembly step is needed.

As the size of the individual electron device approaches nanometer scale, we are approaching the physical limit of top-down silicon technology [1], including transistor scalability, device performance and power dissipation [2]. When the device size is shrinking to the nanometer scale (< 10 nm), the tunnel dielectric will suffer from direct tunneling [3] and severe stress-induced leakage current [4], [5]. The huge intensity of heat generated by millions of transistors will also result in chip performance degradation or even function failure. Lithographic techniques used to produce the circuitry on the silicon wafers are limited by the wavelengths at which they work. While the silicon-based technology may still serve as a mainstream platform for most IC technologies in the next 15 - 20 years, alternative technologies have been suggested in terms of channel materials, transistors, circuits and system-level architectures [10].

Memory is one of the most important parts of any contemporary electronics devices, including all modern computers, cell phones, digital cameras, portable digital audio/video players [6], [7]. It can store data for a certain period of time dependent or independent of external power supply based on

its volatility. Most forms of modern random access memory provide volatile storage, including high speed dynamic random access memory (DRAM) and static random access memory (SRAM), which means they lose all data when the system is powered down. Nonvolatile memories can retain the stored information without power, e.g., read-only memory (ROM), flash memory, etc. At the moment, flash memory is the fastest growing segment of the memory market because of its portability and non-volatility. However, flash memory has slow program and erase speed ( $\mu$ s and ms scale, respectively), compared to that of CMOS logic (ns), primarily due to the requirement of 10-year retention time and reliability concerns. It would be a great achievement to develop a non-volatile memory system with both fast speed comparable to volatile RAM and the 10-year retention ability, such as "NOVORAM" [13] - [18], a highly scalable, non-volatile, floating gate, random-access memory. Such technology would not only save space and energy, but also allow for computers to be turned on and off with the simple press of a button, bypassing the annoyingly slow start-up sequence.

For a floating gate memory (or "flash" memory), silicon dioxide is widely used as the tunnel dielectric. To keep scaling down the transistor as Moore's law demands, the tunnel barrier engineering has been intensively studied. For example, a high-k dielectric, such as  $Al_2O_3$  or  $Si_3N_4$ , is physically thicker than  $SiO_2$  for the same equivalent oxide thickness (EOT), hence substantially reducing the leakage current due to direct tunneling. Another option is to use layered "crested" barriers [13]. At the optimum choice of the potential barrier heights (i.e. conduction band offsets) of the layers and their dielectric constants k, such "crested" barriers could change their transparency by more than 16 orders of magnitude at mere doubling of the voltage applied to the barrier, which is favorable for "NOVORAM" applications.

Other alternative nanodevice concepts, for example, quantum interference devices or single-electronics, offer some potential advantages over MOSFETs, including a broader choice of possible materials. Unfortunately, the minimum features of these devices (e.g., the single-electron transistor island size) for room-temperature operation should be below  $\sim 1$  nm. Since the relative accuracy of their definition has to be of the order of 10%, the absolute accuracy should be of the order of an angstrom or less, far too small for the current and even realistically envisioned future lithographic techniques.

This is why there is a rapidly growing consensus that the impending crisis in the microelectronics progress may only be resolved by a radical paradigm shift from lithography to bottom-up fabrication. In the latter approach, the smallest active devices should be formed in some special way, ensuring their fundamental reproducibility. Opposite to the top-down method, the bottom-

up approach offers much more scalable materials and devices, more flexible material choices, high component packing density and low power dissipation, by employing inexpensive chemistry to promote self-assembly of complex mesoscopic architectures. While the traditional semiconductor technology is reaching the end of the roadmap, molecular nanotechnology opens doors leading to molecular level engineering. The nanoscale components can be inorganic nanocrystals such as nanotubes and semiconductor nanowires, or organic molecular components such as molecular monolayers, molecular wires, single molecules and supramolecules with different architectures. There are a great number of molecular species available, with the potential to be tailored for different device applications by chemical synthesis and surface engineering. These molecular components have great potential in building ultra-dense, low power and low cost computing chips.

However, integrated circuits consisting of molecular-size devices alone are hardly viable, because of their limited functionality. For example, the voltage gain of a 1-nm-scale transistor, based on any known physical effects (e.g., the field effect, quantum interference, or single-electron charging), cannot exceed one, i.e., the level necessary for the operation of virtually any active analog or digital circuits. This is why the only plausible way toward high-performnce nanoelectronic circuits is to integrate nanoscale (e.g., molecular) devices, with the connecting nanowires, on top of CMOS chips whose field-effect transistors would provide the circuit with the necessary additional functionality, in particular high voltage gain. The practical implementation of such hybrid integration, of course, faces several hard challenges, in particular that of interfacing the nanowires with cruder, lithographically-defined CMOS-level wiring. We believe that the recent suggestion of a specific species of CMOS/nanodevice hybrids, called "CMOL" (standing for CMOs/MOLecular circuits) [11] has opened an efficient way for the solution of the interfacing problem.

A CMOL circuit would combine an advanced CMOS subsystem with two mutually perpendicular arrays of parallel nanowires and similar nanodevices formed at each crosspoint of the nanowires. The reason for this topology is that parallel nanowire arrays may be fabricated by several high-resolution patterning technologies, such as nanoimprint or interference lithography. These novel technologies cannot be used for pattering of arbitrary integrated circuits, in particular because they lack an adequate layer alignment accuracy; fortunately the crosspoint topology does not require such alighment. This approach requires a nanodevice formation process that also does not need lithographic patterning.

The purpose of this thesis work was two-fold: (1) to explore the possibilities of implementation of specially engineered "crested" barriers for fast,

scalable, nonvolatile random-access memories; and (2) to study single-electron integrable molecular devices for the possible future use as sub-10-nm crosspoint latching switches in CMOL circuits. The outline of the thesis is as follows.

In Chapter 2 we give an introduction to the layered "crested" barriers and their advantages over traditional SiO<sub>2</sub> tunnel barriers. The main transport mechanism is based on direct tunneling and the calculation of tunneling current will be demonstrated. The transmission coefficient may be calculated by joint solution of the Schrödinger and Poisson equations.

Chapter 3 describes the fabrication and electrical characterization of aluminum oxide barriers grown by thermal and plasma oxidation of aluminum thin film, with rapid thermal post-annealing of the resulting junctions. The barrier parameters, such as barrier height, and barrier thickness have been extracted from numerical fittings employing the quantum tunneling model. TEM characterization of these barriers will be also presented. Some initial experimental data for the double layer barriers, combining these two types of  ${\rm AlO}_{\rm x}$ , are also shown.

A brief introduction to electron transport in single-molecule junctions will be given in Chapter 4, with a brief summary of current experimental techniques to realize molecular devices. We are particularly interested in oligo(phelene-ethylene) based molecules with, or without the center naphthalene diimide acceptor group.

In Chapters 5-7, we investigate electron transport through single molecular devices for three types of structures: (i) co-planar Au electrodes with  $\sim$  5 nm gaps formed by e-beam lithography, (ii) co-planar Au electrodes with 1  $\sim$  2 nm gaps formed by electromigration, and (iii) nanowires crosspoints with vertical gaps of 3  $\sim$  5 nm formed by under-etched aluminum oxide layers. We use two types of oligo(phenylene-ethynylene) based molecules capped with isocyanide terminal groups: (i) molecular wire-like OPE chains with one or two rings in the middle; (2) molecular transistor-like OPE-NDI (naphthalenedimide) chains, where the NDI group is served as a single-electron island in the middle. Their current-volatage characteristics and dependences on the gate voltage and temperature have been studied in detail. We have observed nonlinear current-voltage curves with either conductance peaks or Coulomb blockade with single-electron addition energy above 100 meV.

### Chapter 2

### Crested Tunnel Barrier: Simulation and Barrier Engineering

In this chapter, we first introduce the concept of crested tunnel barriers and their applications on nonvolatile memory devices. A charge transport model is presented to calculate the tunneling current through layered barriers. The numerical algorithm is based on the joint solution of Schröinger equation and Poisson equation. Barrier engineering will be discussed to find the optimized barrier parameters.

### 2.1 Operating Principle in Flash Memory

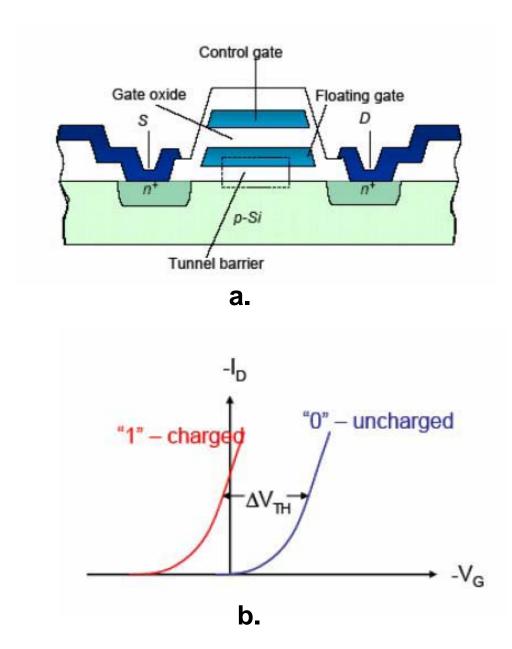

The demand for non-volatile semiconductor devices has grown rapidly in recent years. Among the different categories in non-volatile semiconductor devices including ROM, EPROM, EEPROM, etc., flash memory has been considered as of the most interest. The basic operating principle for flash memory lies in the charge storage in the floating gate of a metal-oxide semiconductor field effect transistor (MOSFET), as illustrated in Figure 2.1 a. Charge is stored on the floating gate of flash memory after electrons are transported through the tunnel oxide from the channel generated in the silicon substrate. The tunnel oxide, usually silicon oxide, must be sufficiently thin for high electric field to induce tunneling of electrons toward the floating gate, but still thick enough to trap the charges in the conduction band of the floating gate. Upon the removal of the gate voltage, the field in the tunnel barrier should be small to prevent charge from tunneling back to the substrate. By applying appropriate voltages to the control gate, source, and drain electrodes, charge carriers travel

through the tunnel oxide and are stored on the floating gate even after the voltages are removed. The amount of charge stored on the floating gate of the MOSFET can be modified to alternate between two distinct values, usually defined as the "0" erased state and the "1" programmed state, as shown in 2.1 b.

The state of a flash memory device is detected by applying a gate voltage  $V_G$  with a value between the two possible threshold voltages. In one state, the transistor conducts current, while in the other state, no current flows. Even if the power supply is interrupted, the stored charge will keep the requested memory state for later use.

#### 2.2 What's a Crested Tunnel Barrier

The programming speed in nonvolatile floating-gate memory cells is rather slow for standard silicon dioxide barriers (of the order of miliseconds). The main reason is that such uniform barrier cannot combine the low transparency necessary for long retention time with the high transparency necessary for fast write/erase time. This drawback limits the application of floating-gate memories to compete with random-access memories and flash memories.

The crested barrier concept proposed by Likharev [13] provides an exciting opportunity for the radical improvement of nonvolatile semiconductor memories. By carefully engineering the barrier profile, we could obtain memories with high programming speed comparable to DRAM ( $\sim 10~\rm ns$ ) and long retention time ( $\sim 10~\rm years$ ) at the same time. The transparency of such barriers is much more sensitive to the applied voltage than the traditional uniform layers, due to the faster decrease of tunnel barrier height. As a result, it could be used in fast, bit-addressable nonvolatile random access memories (NOVORAM), a leading candidate for multi-terabit memory chips with scalability.

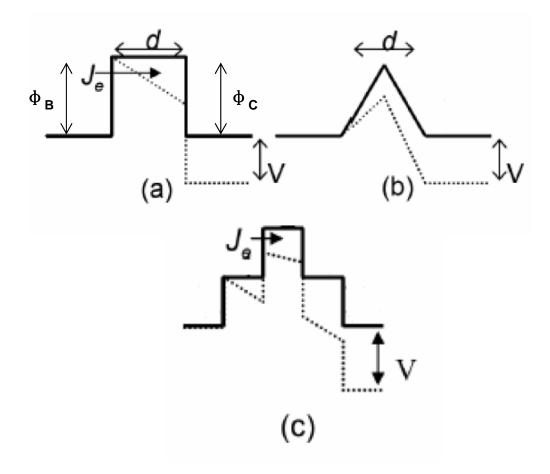

The schematic representation of a floating gate memory is shown in Figure 2.1 a. with three corresponding conducting band edge diagrams (Figure 2.2). The solid lines represent the diagrams at V = 0, while dotted lines show the effective band-offset after voltage V is applied.

(1) Uniform barrier: Usually we use three parameters to describe the potential of the oxide with uniform barriers: the average barrier height  $\phi_a$  ( $\phi_a = (\phi_B + \phi_C)/2$ ), barrier asymmetry  $\Delta \phi = \phi_C - \phi_B$ , and the barrier thickness d, where  $\phi_B$  and  $\phi_C$  are the tunnel barrier heights at the oxide interfaces with the base electrode and the counter electrode. It is widely used in conventional floating gate memory devices, e.g., silicon oxide. Although it could retain a few years retention time, the write/erase time is in millisecond range, much slower than the current DRAM ( $\sim 10 \text{ ns}$ ). The reason is that the

Figure 2.1: a. Schematics of a floating gate memory; b. Influence of charge of the floating gate on MOSFET's current.

Figure 2.2: Conduction band edge diagrams of various type of tunnel barriers: (a) a typical uniform barrier; (b) idealized crested barriers (c) crested, layered barriers. Dashed lines show the barrier tilting caused by applied voltage V.

barrier transparency depends slowly on the applied electric field. The highest part of the barrier (close to the source electrode) is weakly affected by the applied voltage  $\phi_{max}(V) \approx \phi_{max}(0)$ .

- (2) Triangular or "crested" barrier refers to a tunnel barrier with the highest barrier height in the middle and gradually decreasing side barriers toward the conducting electrodes. The transparency of this type of barrier is much more sensitive to the applied electric field, due to the fact that maximum potential (close to the middle of the barrier) is strongly dependent on voltage V:  $\phi_{\text{max}}(V) = \phi_{\text{max}}(0) - eV/2$ . Calculations [13] show that the floating gate recharging time could change from  $10^8$  s to  $10^{-8}$  s when the voltage changes from  $V_0$  to  $2V_0$  (here,  $V_0$  characterize the maximum voltage created by stored charge). This dramatic improvement enables possible applications of such barriers in NOVORAM. The implementation of crested barriers is straightforward, if the barrier shaping may be achieved with either a gradual change of the layer composition [28], [29], or by modulation doping [30] in A<sub>3</sub>B<sub>5</sub> compounds. However, the maximum barrier height for these materials is too small to provide sufficient retention time at room temperature. For most wide-bandgap materials, it is not yet possible to make such graded barriers that are compatible with current technology.

- (3) A layered tunnel barrier may be fabricated by stacking two or three layers of dielectric materials with appropriate barrier parameters and suggested as an alternative to the triangular barriers. Calculations [13] show that the layered barrier could perform as good as the triangular barrier, by combining, say, a three-year retention time with a 10-ns programming time. The electric field necessary for write/erase can be as low as  $\sim 6$  MV/cm, which ensures high endurance of such barrier under electric stress. At the optimum choice of their potential barrier heights and dielectric constants, the transparency of the tunnel barrier can be changed to more than 16 orders of magnitude by merely doubling the applied voltage. The applications of the layered barriers include bit-addressable nonvolatile random access memories (NOVORAM), fast single- and few-electron memories, electrostatic data storage (ESTOR) systems [14] [18].

### 2.3 Calculation of Tunneling Current Through Metal-Insulator-Metal Junctions

Based on the free electron approximation [9], the coherent tunneling current through typical metal-insulator-metal devices may be calculated by jointly solving Schröinger equation and Poisson equation. Assuming that the energy of the tunnel electron and the transverse component of the momentum are both conserved, the tunneling current density is given by:

$$J = \frac{em_e}{2\pi^2 \hbar^3} \int_0^\infty dE_x \int_0^\infty dE_\perp \mathcal{T}(E_x, E_\perp) [f_L(E_x, E_\perp) - f_R(E_x, E_\perp)]. \tag{2.1}$$

where  $\mathcal{T}$  is the transmission coefficient;  $E_x$ ,  $E_{\perp}$  are the local energy and the transverse energy of a tunneling electron;  $m_e$  is the effective mass of the transverse electron and  $f_L$ ,  $f_R$  are the equilibrium Fermi-Dirac distribution functions in the left and right electrodes.

For anmetal-insulator-metal (MIM) junction, we could use a 1D model to describe the barrier profile. The tunneling current density includes the carrier transport in both directions between two metal contacts. In the case of T=0, the Fermi energy function of the metal is written as:

$$f_i(E_x, E_\perp) = \begin{cases} E_{fi} & \text{if } E_x \le E_{fi}, \\ 0 & \text{if } E_x > E_{fi}, \ i = L, R. \end{cases}$$

(2.2)

where  $E_{fL}$  and  $E_{fR}$  are Fermi energies of the left and right metal electrodes respectively. The current density J could be simplified as:

$$J = J_{L->R} - J_{R->L}$$

$$= em_e/(2\pi^2\hbar^3) \left\{ eV \int_0^{E_{fL}-eV} \mathcal{T}(E_x) dE_x + \int_{E_{fL}-eV}^{E_{fL}} \mathcal{T}(E_x) (E_{fL} - E_x) dE_x \right\}.$$

(2.3)

For the case of T > 0, we assume that the electrons are distributed according to equilibrium Fermi-Dirac distribution in the left and right electrodes, determined by the bulk Fermi levels on the respective sides of the barrier:

$$f_L(E_x, E_\perp) = 1/(1 + \exp(\frac{E_x + E_\perp - E_{fL}}{k_B T})),$$

$$f_R(E_x, E_\perp) = 1/(1 + \exp(\frac{E_x + E_\perp - E_{fL} + eV}{k_B T})).$$

(2.4)

The current density is thus given by:

$$j = \frac{em_e}{2\pi^2\hbar^3}k_BT \int_0^\infty \mathcal{T}(E_x)dE_x \int_0^\infty [f_L(E_x, E_\perp) - f_R(E_x, E_\perp)]dE_\perp.$$

(2.5)

After integration over the transverse energy  $dE_{\perp}$  for the second integral, we obtain:

$$j = \frac{em_e}{2\pi^2\hbar^3}k_BT \int_0^\infty \mathcal{T}(E_x)ln(\frac{1 + e^{(E_{fL} - E_x)}/k_BT}{1 + e^{(E_L - E_x - eV)/k_BT}})dE_x.$$

(2.6)

This is called the Tsu-Esaki formula. The logarithmic term is called the supply

function.

#### 2.4 Transmission Coefficients

The key quantity in the tunneling current is the transmission coefficient  $\mathcal{T}$ . Several methods of its calculation have been developed. One of the most commonly used is the WKB (Wentzel-Kramers-Brillouin) approximation. The wavefunction is approximated as an exponential function, and the amplitude or the phase is taken to be slowly changing. For a simple trapezoidal tunnel barrier, the transmission coefficient  $\mathcal{T}$  is given by:

$$|\mathcal{T}|^2 \approx \exp(-2\int_0^d dx \left[\frac{2m_e}{\hbar^2}(U(x,V) - E)\right]^{\frac{1}{2}}),$$

(2.7)

where U(x, V) is the potential function of the barrier at the applied voltage V, d is the width of the barrier. The probability of barrier penetration is exponentially dependent on the product of the barrier height and thickness.

Although the WKB approximation provides good estimation for the transmission coefficient  $\mathcal{T}$ , it has drawbacks, especially for the thin and sharp barriers for metallic electrodes in a few nanometer range. It is questionable to apply the formula to gate stacks with ultra-thin interfacial oxide layer with thickness comparable to the de Broglie wavelength of the tunneling electron, since the method does not include quantum mechanical interferences of the incident and reflected waves at the interfaces it does not properly treat the transmission near the band edges or through propagating states [20]. Our calculations [19] have shown a significant difference between WKB calculation and the exact solution for 1-nm-thin barriers, which is equivalent to be a  $\sim 3\%$  error for average barrier height  $\phi_a$  and  $\sim 10\%$  error for effective barrier thickness  $d_{ef}$  (=  $(m_e/m_0)^{1/2}d$ , where  $m_0$  is the electron mass).

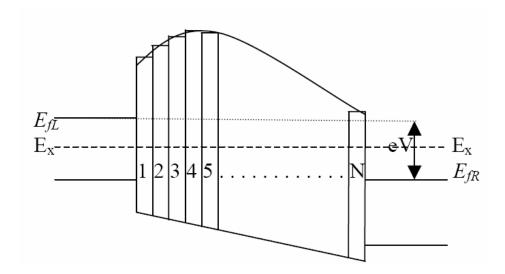

A more accurate way to calculate the transmission coefficient  $\mathcal{T}$  is obtained by numerically solving the Schrödinger equation and Poisson equation. We solve for  $\mathcal{T}$  using transfer matrix formalism [27]. By breaking the potential barrier into N square pieces (Figure 2.3), the transmission coefficient can be calculated to arbitrary precision within the independent-electron picture. For each slice i, the Schrödinger equation can be solved analytically. Assuming that a one-band parabolic dispersion model is used for all the dilelectric layers, we use plane wave functions to describe the incoming and outgoing electrons through each slice:

$$\psi(x) = A_i e^{ik(x - X_i)} + B_i e^{-ik(x - X_i)}, \quad X_i < x \le X_{i+1}$$

(2.8)

Figure 2.3: Illustration of the potential barrier divided as N equal pieces.

with

$$k = \sqrt{2m(E - U)}$$

where U is the potential energy of the barrier, and  $X_i$  is the position of the  $i^{th}$  slice. The boundary conditions require continuity of the wave function and its spatial derivative, which satisfy:

$$|\psi(x)|_{x=X_i^-} = |\psi(x)|_{x=X_i^+}$$

(2.9)

$$\frac{1}{m_i^-} \frac{d\psi(x)}{dx} |_{x=X_i^-} = \frac{1}{m_i^+} \frac{d\psi(x)}{dx} |_{x=X_i^+}$$

(2.10)

where the + and - symbols are used for the left and right sides of a specific interface  $X_i$ .

As a result, we obtain  $2 \times 2$  matrices:  $\mathbf{b}_{i+1,i}$  from boundary conditions and the propagation matrix  $\mathbf{p}_{i+1}$  for  $i^{th}$  slice as follows:

$$\begin{pmatrix} A_{i+1} \\ B_{i+1} \end{pmatrix} = \mathbf{p}_{i+1} \mathbf{b}_{i+1,i} \begin{pmatrix} A_i \\ B_i \end{pmatrix}. \tag{2.11}$$

Matrices  $\mathbf{p_i}$  and  $\mathbf{b_{i+1,i}}$  are expressed as follows:

$$\mathbf{p}_{i} = \begin{pmatrix} e^{jk_{i}a} & 0 \\ 0 & e^{-jk_{i}a} \end{pmatrix}; \mathbf{b}_{i+1,i} = \frac{1}{2} \begin{pmatrix} 1 + k_{i}m_{i+1}/k_{i+1}m_{i} & 1 - k_{i}m_{i+1}/k_{i+1}m_{i} \\ 1 - k_{i}m_{i+1}/k_{i+1}m_{i} & 1 + k_{i}m_{i+1}/k_{i+1}m_{i} \end{pmatrix}$$

(2.12)

For the whole barrier, we obtain:

$$\begin{pmatrix} A_{N+1} \\ 0 \end{pmatrix} = \tau_{N+1} \begin{pmatrix} A_0 \\ B_0 \end{pmatrix} \tag{2.13}$$

where the inverse of  $\tau_{N+1} = \mathbf{b}_{N+1,N} \mathbf{p}_N \mathbf{b}_{N,N-1} \dots \mathbf{p}_2 \mathbf{b}_{1,0}$  is also called the "transfer matrix". The transmission coefficient  $\mathcal{T}$  is calculated to be:

$$\mathcal{T} = \frac{m_L k_R}{m_R k_L} \left| \frac{A_{N+1}}{A_0} \right|^2 = \frac{m_L k_R}{m_R k_L} |\tau_N(1,1)|^2$$

(2.14)

where  $m_L$  and  $m_R$  is the effective electron mass,  $\hbar k_{L,R}$  is the x component of the momentum of electron in left/right electrodes,  $|A_0|^2$  is the amplitude of the incoming wave function in the left electrode,  $|A_{N+1}|^2$  is the amplitude of the outgoing wave function in the right electrode. The tunneling current can be computed easily after the transmission coefficient  $\mathcal{T}$  has been obtained.

For layered tunnel barriers with different barrier height and dielectric constant, the electrons tunneling into the dielectric create an electrostatic potential. To account for this effect, we solve the 1D Poisson equation and Schrödinger equation in a self-consistent manner, which results an increase the average barrier height substantially [19]. We also account for hot electron relaxation in classically allowed region of the barrier by introducing an exponential decay in the "propagation" matrix  $(e^{jk_ia}$  to  $e^{jk_ia}e^{-a/L})$ . The parameter L is the inelastic relaxation length, which is typically of around 0.1 - 0.5 nm. Such relaxation suppresses the current resonances due to the over-barrier reflection [31].

#### 2.5 Selection of Barrier Parameters

There are several factors that need to be taken into account when selecting the appropriate materials to demonstrate a crested barrier. The key parameters to characterize a tunnel barrier include the barrier height, dielectric constant, thickness and effective mass of each dielectric layer.

The barrier height U relates to work function W of the metal electrode and electron affinities  $\chi$  of the dielectric by  $U = W - \chi$ , where W is defined as the difference between the vacuum level and the Fermi energy of the metal electrode and  $\chi$  is the difference between the vacuum level and the conduction band level of the dielectric. U is the most important parameter that will determine the barrier performance. Ideally, the barrier height of the center layer is expected to be 1 - 2 eV higher than that of the side layers. The fast suppression of such barrier under applied voltage will enhance the fast change

| Material  | Dielectric | Band gap | $\varphi_B$ - Si | $\varphi_B$ - Au | $\varphi_B$ - Nb | Effective |

|-----------|------------|----------|------------------|------------------|------------------|-----------|

|           | Constant   | (eV)     | (eV)             | (eV)             | (eV)             | mass      |

| $SiO_2$   | 3.9        | 9        | 3.5              | 4.0              | 3.2              | 0.5       |

| $Al_2O_3$ | 9          | 9        | 2.8              | 3.4              | 2.6              | 0.2 - 0.5 |

| $Si_3N_4$ | 7.8        | 5.3      | 2.4              | 2.9              | 2.1              | 0.4       |

| $HfO_2$   | 18         | 6        | 1.5              | 2.1              | 1.3              | 0.2       |

| $ZrSiO_x$ | 12.6       | 6        | 1.5              | 2.1              | 1.3              | -         |

| $ZrO_2$   | 25         | 5        | 1.4              | 2.0              | 1.2              | -         |

Table 2.1: List of values of dielectric constant, band gap and conduction band offset for various dielectric materials [20] - [26].

of the tunnel current.

Dielectric constant for different tunnel layers will also affect the performance of the barrier. High-k dielectric has low leakage current at low bias due to the increased physical thickness (corresponding to the same EOT for Si). Under applied bias, the voltage redistributes over the barrier layers in the way that the electric field in each layer is inversely proportional to their dielectric constant. At the high field, the high-k layer has only a minor impact on the magnitude of the tunneling current. The barrier height of the high-k dielectric becomes an important factor for the crested barrier to realize high current at high voltages. The best combination would be high-k layer with high barrier height in the center and low-k layer with low barrier height on both sides. It is challenging to find materials that meet these requirements since most high-kdielectrics usually have low band-offsets and vice versa. However, incorporating high-k dielectrics into the crested barrier even as side layers still give a better performance than using the uniform silicon dioxide barrier. Table 2.1 lists the reported dielectric constants, band gaps and conduction band offset of interesting dielectric materials. In addition, the effective mass  $m_e$  and physical thickness d of each layer will affect the performance of crested barriers as a whole  $(m_e/m_0)^{1/2}d$ .

In summary, to build a crested barrier with steep I-V, we need to consider the electron affinity and dielectric constant of the dielectrics, the work function of the metal electrode and the effective thickness of each layer. A high-k dielectrics is desirable to be incorporated in the stack to improve the low field performance. High conduction-band offset for a dielectric is a must for the center layer.

It is a challenge to find an appropriate combination of materials for crested barrier layers. Experiments [34] indicate that just a few known CMOScompatible materials may combine the barrier height sufficient for thermionic current suppression at room temperature (above 1.5 eV), with the necessary high breakdown field (above 10 MV/cm) and negligible trap-assisted tunneling. The list of such candidate materials is essentially limited to (1) silicon dioxide; (2) low-trap density silicon nitride [32], [33]; (3) aluminum oxide grown by a variety of methods including thermal [37] and plasma [38] oxidation.

### Chapter 3

### Transport Through $AlO_x$ - based Tunnel Barriers

#### 3.1 Background

As mentioned in Section 2.5, in the beginning of our work it seemed that aluminum oxide represents a good material choice for fabrication of crested barriers for nonvolatile random access memories (NOVORAM) [18], since it has high dielectric constant, large band gap and large barrier height. Together with their good thermal and mechanical stability, aluminum-oxide barriers serve as the basic components of devices used in low-temperature superconductor electronics, including superconducting quantum computing, metallic single-electronics and spintronics.

Aluminum oxide has been intensively investigated for the past decade, however, literature data concerning properties of these barriers are scattered rather broadly, especially in the range of relatively high oxygen exposure,  $E \geq 10^5$  Pa-s corresponding to specific zero-field conductances below  $\sim 10^{10}~\Omega^{-1}m^{-2}$  For thermally grown oxides [37], the average tunnel barrier height U are in the range from 1.7 eV to 2.5 eV [39] - [45], but values as low as 1.2 eV [46], and as high as 4.75 eV [47], or even 20 eV [48], have also been derived from the data. Similarly, for plasma-grown layers [38], most reported values of barrier height are in the range from 1.7 to 2.3 eV [49] - [52], but numbers as high as 3.6 eV have also been claimed [53]. The published results for the apparent barrier asymmetry are scattered even more, from a few tenths of eV all the way up to 6 eV [47], and the only apparent consensus is that the barrier is always higher at the top interface (near the counter electrode). The most important sources of these differences are probably those of the film fabrication, including the substrate temperature that has not always been carefully monitored, and dif-

ferent counter electrode materials. The scattering of the results may be also attributed to the variety of techniques used for barrier height measurement, including I-V curve fitting methods [39], [40], [42]-[45], [47], [48], [50]- [53], photoelectric effect [41], [43], [49] and ballistic electron emission spectroscopy [46].

In addition, the effect of thermal annealing on tunnel barriers is also very interesting to study. It was noticed previously that post-annealing may improve tunneling magnetoresistance of junctions between magnetic layers [54]-[60]. Some changes in the average barrier height at annealing were noticed in references [54], [56], and [57]-[60]. However, the change was typically small (due to low annealing temperature), so that no definite conclusions could be drawn even about the sign of the effect.

In this chapter, we will discuss detailed studies on thermally grown and plasma grown aluminum oxide. We have carried out current-voltage measurements for these tunnel barriers. Using the quantum tunneling model based on joint solution of Schrödinger and Poisson equations, we have extracted the barrier parameters (barrier height, barrier thickness, etc.) for aluminum oxide barriers, which will be used for further design of crested barriers.

### 3.2 Sample Fabrication

### 3.2.1 Thermally/Plasma Grown $AlO_x$ as Single-Layer Barriers

Two types of samples were obtained respectively from Prof. J. Luken's fabrication laboratory (SBU) (2-inch deposition tool) and Hypres, Inc. (6-inch tool in industrial environment). Table 3.1 and 3.2 show all the wafers with single aluminum oxide layers as tunnel barriers, grown by thermal (TO) or plasma oxidation (PO) with processing parameters including base electrode, oxidation pressure, oxidation time, and rf-plasma power.

For simplicity, we will describe the fabrication process at SBU here. The oxide layers have been grown on 2-inch silicon wafers ( $\rho = 10~\Omega*cm$ ) covered by 500 nm of thermally grown SiO<sub>2</sub>, in a cryopumped vacuum system with a base pressure close to  $2 \times 10^{-7}$  torr, as components of standard Nb-trilayer junctions.

First, a 150-nm-thick niobium base film has been deposited using dc-magnetron sputtering at a rate of 1.6 nm/s. Then, without breaking the vacuum, a 10-nm-thick aluminum film has been deposited by the same method at a lower speed (0.5 nm/s). It is well known that at these conditions aluminum wets the niobium surface, forming a smooth uniform coating [61].

| Wafer    | Base Electrode  |      | Al Interlayer | Thermal Oxidation |       |  |

|----------|-----------------|------|---------------|-------------------|-------|--|

|          | Metal Thickness |      | (nm)          | Pressure          | Time  |  |

|          |                 | (nm) |               | (Torr)            | (min) |  |

| Crest 2  | Nb              | 150  | 8-10          | 2.5               | 10    |  |

| Crest 5  | Nb              | 150  | 8-10          | 100               | 40    |  |

| Crest 12 | Nb              | 150  | 8-10          | 100               | 2400  |  |

| KL669    | Nb              | 150  | 8-10          | 100               | 40    |  |

| VJCB 4   | Nb              | 50   | 3             | 100               | 50    |  |

Table 3.1: Thermal Oxidation Process Parameters

| Wafer    | Base Electrode |           | Al Interlayer | Plasma Oxidation |       |       |

|----------|----------------|-----------|---------------|------------------|-------|-------|

|          | Metal          | Thickness | (nm)          | Pressure         | Time  | Power |

|          |                | (nm)      |               | (mTorr)          | (min) | (W)   |

| Crest 19 | Nb             | 150       | 8-10          | 15               | 10    | 50    |

| N3081    | Nb             | 150       | 8-10          | 15               | 10    | 50    |

| VJCB2    | Nb             | 125       | 6             | 15               | 10    | 50    |

| VJCB3    | Nb             | 125       | 6             | 75               | 10    | 50    |

| VJCB6    | Nb             | 50        | 6             | 15               | 3     | 50    |

| VJCB7    | Nb             | 50        | 5             | 15               | 30    | 50    |

| VJCB14   | Nb             | 50        | 6             | 15               | 10    | 50    |

| VJCB13   | Al             | 50        | -             | 15               | 10    | 50    |

| VJCB17   | Al             | 50        | -             | 15               | 10    | 10    |

| VJCB18   | Al             | 50        | -             | 15               | 10    | 100   |

| VJCB20   | Al             | 50        | -             | 15               | 10    | 250   |

| VJCB21   | Al             | 50        | -             | 5                | 10    | 100   |

Table 3.2: Plasma Oxidation Process Parameters

After that, the aluminum film has been oxidized either thermally at room temperature or in oxygen plasma. In the former case, a well-monitored amount of ultra-high-purity (semiconductor-grade) oxygen has been let into the vacuum chamber for a certain time. The same gas has been used for the plasma oxidation, but in this case a 13.56 MHz source has been connected, via a tuned resonant circuit, to a dc-insulated copper plate on which the substrate had been mounted. This has resulted in a 50 W rf plasma discharge and wafer dc self-biasing to approximately -80 V relative to the ground (vacuum chamber walls). The wafer has been kept at room temperature by its thermal anchoring to the water-cooled copper plate.

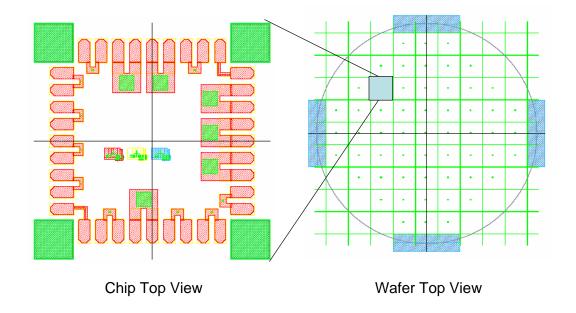

After oxidation, the chamber has been pumped down to the base pressure and a niobium 100-nm-thick counter-electrode has been deposited in situ in the same way as the base electrode. The fabrication had been completed by sample patterning into junctions of various area  $(3\times3,30\times30,$  and  $300\times300~\mu\text{m}^2)$  using optical lithography with PMMA resist and reactive ion etching in SF<sub>6</sub> plasma. Here, the same photoresist mask was first used for the counter electrode shape definition using RIE, and later for a lift-off of a sputtered 150-nm-thick SiO<sub>2</sub> insulation layer from the junction surface (the so-called self-aligned lift-off process). The lift-off has opened contacts of junction counter electrodes with the following thicker niobium wiring layer (300 nm), with wiring configured for four-point measurements. Figure 3.1 shows the layout of the chip, where the green square area corresponding to a tri-layer junction.

We have fabricated 5 wafers under thermal oxidation with different oxygen exposures. Two of them were reproduced at Hypres, Inc. and SBU at different time, in order to check the reproducibility of these wafers. A total of 12 wafers have been fabricated under plasma oxidation at SBU and Hypres, Inc., to study the oxide behavior under different oxygen exposure conditions (pressure, time and power). A digital control system responsible for plasma oxidation has been developed in order to change these parameters precisely. Among them, wafers "Crest 19", "N3081", "VJCB2" and "VJCB14" have been fabricated under the same oxygen exposure conditions.

### 3.2.2 Thermally/Plasma Grown $AlO_x$ as Double-layered Barriers

Single-dielectric layers have been fabricated to learn about the physical and electrical characteristics of the individual layers, in order to understand and design multi-layer samples. We have tried the two-layer samples with PO-grown and TO-grown aluminum oxides.

Table 3.3 lists the set of wafers with double-layer aluminum oxide barriers,

Figure 3.1: Left: Layout (top view) of our chip containing 18 junctions with three different areas  $3 \times 3, 30 \times 30, 300 \times 300 \ \mu \text{m}^2$ . Right: Top view of the whole wafer.

which contains  $PO - AlO_x$  and  $TO - AlO_x$  heterostructures. The aluminum oxide has been grown in the same method as described above (Section 3.2.1) at SBU and Hypres, Inc. Most wafers have the plasma oxidized layer as the first tunnel barrier, followed by sputtering a thin aluminum layer with thickness varying from 1 nm to 3 nm. The second thin aluminum layer has been thermally oxidized under the same condition as wafer "Crest 2" or "Crest 5" without breaking the vacuum. Wafer "VJCB15" has the reverse aluminum oxide heterostructure from the others. The thermally oxidized layer has been first fabricated, followed by a deposition of relatively thick aluminum layer (3.8 nm) and plasma oxidized under the same condition as wafer "Crest 19".

### 3.3 Post Fabrication - Rapid Thermal Annealing

Rapid thermal anneal (RTA) is a process used in semiconductor device fabrication, which consists of heating a single wafer at a time in order to affect its electrical properties. Unique heat treatments are designed for different effects. Wafers can be heated in order to activate dopants, change film-to-film or film-to-wafer substrate interfaces, densify deposited films, change states of grown

| Wafer  | Oxidation | Base Electrode |                 | Al   | Oxidation Condition |       | ion   |

|--------|-----------|----------------|-----------------|------|---------------------|-------|-------|

|        | Type      | Metal          | Metal Thickness |      | Pressure            | Time  | Power |

|        |           |                | (nm)            | (nm) | (mTorr)             | (min) | (W)   |

| N3080  | Plasma    | Nb             | 150             | 8-10 | 15                  | 10    | 50    |

|        | Thermal   |                |                 | 1.0  | 2500                | 10    | -     |

| N3094  | Plasma    | Nb             | 150             | 8-10 | 15                  | 10    | 50    |

|        | Thermal   |                |                 | 1.3  | 100000              | 40    | -     |

| N3096  | Plasma    | Nb             | 135             | 13   | 15                  | 10    | 50    |

|        | Thermal   |                |                 | 1.3  | 100000              | 40    | -     |

| VJCB15 | Thermal   | Al             | 50              | -    | 100000              | 40    | -     |

|        | Plasma    |                |                 | 3.8  | 15                  | 10    | 50    |

| VJCB16 | Plasma    | Al             | 50              | -    | 15                  | 10    | 50    |

|        | Thermal   |                |                 | 1.5  | 100000              | 40    | -     |

| VJCB19 | Plasma    | Al             | 50              |      | 15                  | 10    | 50    |

|        | Thermal   |                |                 | 3.0  | 100000              | 40    | -     |

Table 3.3: Processing parameters of PO / TO double-layer aluminum oxide tunnel barriers.

films, repair damage from ion implantation, move dopants or drive dopants from one film into another or from a film into the wafer substrate.

Several  $5 \times 5$  mm<sup>2</sup> chips from each wafer have been subjected to rapid thermal annealing (RTA) in inert atmosphere (N<sub>2</sub> or Ar), using the rapid thermal module (Model No. RTM 2016-M-2F-FC) made by Process Products Corporation and capable of providing temperature excursions from room temperature to  $1250^{\circ}$ C at heating rates up to  $300^{\circ}$ C/sec and cooling rates of approximately  $100^{\circ}$ C/sesc. The specimen can be held at constant temperatures accurately  $\pm 2.5^{\circ}$ C. Specimen temperature is automatically controlled by a built-in programmable "Micristar" controller. The power controller provides power to Tungsten halogen lamps arranged around the quartz chamber, which are designed to provide infra-red (I. R.) energy, either directly or being reflected onto the specimen. The "Micristar" controller is also used to control the process gas (e.g., nitrogen) by setting their sequence and flow paths using air operated valves.

After initial electrical characterization for quality checking, the samples have been loaded into the quartz chamber and placed close to the thermal couple (within 0.005 inches) to prepare for the heating. The inert gas ( $N_2$  or Ar) has been letting into the chamber. After waiting for over 30 minutes (long enough to let the inert gas be filled in the chamber), the chamber has been pre-warmed up to 200°C in 20 seconds for soft starting the system, which in-

sures a consistent starting point for each run and prolongs the life of the lamps. Following this pre-conditioning of the oven, the heating temperature has been increased very fast in a speed of  $50-100^{\circ}\text{C/sec}$ , reaching the targeted temperature in only a few seconds. The sample has been kept at this temperature for a certain time, usually 30 to 180 seconds. After the heater was turned off, the chamber has been immediately cooled down by water cooling and venting. We have studied the effect of annealing temperature and annealing time on both thermally oxidized and plasma oxidized aluminum oxide structures, which will be discussed later.

RTA were also done in Yale University by X. Wang under similar conditions. The annealing results for samples from the same wafer are reproducible with each other.

### 3.4 HR-TEM Characterization of $AlO_x$ Structures

Let us first look at the physical properties of as-grown and annealed  ${\rm AlO_x}$  structures using high resolution transmission electron microscopy (HRTEM). HRTEM is used to study the physical thickness and morphology of aluminum oxide films. HRTEM is an imaging mode of the transmission electron microscope (TEM) that allows the imaging of the crystallographic structure at atomic scale. Z-contrast imaging allows us to study the oxide barrier thickness and crystallinity of our samples due to different mass of the elements in each layer. The resolution is about 1Å. All the TEM analysis has been done at Brookhaven National Lab by R. F. Klie and L. H. Zhang.

#### 3.4.1 Thermally Grown Aluminum Oxide

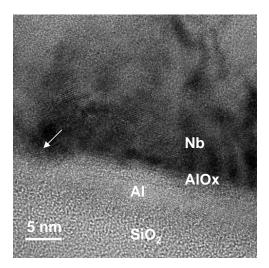

Wafer "Crest 5" and "VJCB4" have been made from SBU tools under similar oxidation conditions, except that "Crest 5" had niobium base electrode while "VJCB4" had aluminum base electrode. Two TEM images of selected samples from wafer "VJCB4" are shown in Figure 3.2. We observe a very thin aluminum oxide layer of only 1 - 2 nm. In some areas the Nb top-layer penetrates through the  ${\rm AlO}_{\rm x}$  layer into the aluminum layer. The bottom aluminum layer does not seem to be continuous, which could be the results of the artifacts of TEM slice preparation rather than those of the sample fabrication.

After the sample (from wafer "Crest 5") has been rapid thermally annealed at  $400^{\circ}$ C for 30 seconds, we could see a much more clear interface between Al and AlO<sub>x</sub> layers. The film thickness appeared to increase after annealing. The picture quality is affected by the fact that the base Nb electrode is

a. As-grown Aluminum Oxide

b. Annealed Aluminum Oxide

Figure 3.2: High resolution TEM picture of thermally grown aluminum oxide: (a) as grown sample from wafer "VJCB4"; (b) annealed sample from wafer "Crest 5". The annealing conditions are as follows: heating temperature = 400°C, ramping rate = 25°C/min, heating time (at 400°C) = 2 minutes, Chamber oxygen pressure  $\sim 5 \times 10^{-8}$  Pa.

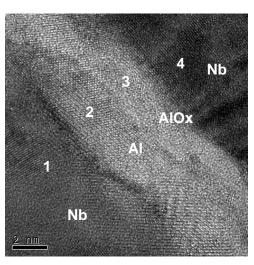

Figure 3.3: Results of the electron loss spectroscopy for two energy ranges from the positions indicated in Figure 3.2: (1) Nb base electrode (2) Al layers (3) AlO<sub>x</sub> layer, and (4) Nb counterelectrode. The spectra are background subtracted, and corrected for multiple scattering contributions. The carbon K-edge present in all the spectra stems from the carbon build-up during the spectrum acquisition and is apparently not a feature of the initial sample structure.

relatively thick and polycrystalline, so its surface is uneven at a-few-nanometer scale. Nevertheless, the images reveal an amorphous  $\mathrm{AlO_x}$  layer with a thickness of  $\sim 3$  nm. Figure 3.3 shows the electron energy loss spectroscopy across the sample at four different positions: bottom Nb, Al,  $\mathrm{AlO_x}$  and top Nb. The Al L-edge of the  $\mathrm{AlO_x}$  layer shows a much stronger first peak, usually indicating an amorphous oxide. An interfacial layer is visible between  $\mathrm{AlO_x}$  and top Nb layer.

### 3.4.2 Plasma Oxidized Aluminum Oxide

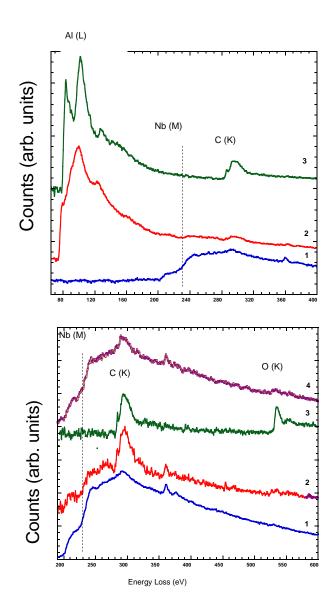

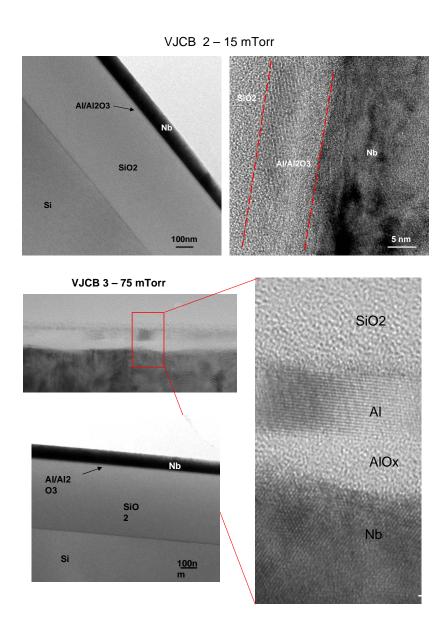

Samples from wafer "Crest 19" have a thick Nb base electrode ( $\sim 150$  nm). It is difficult to make specimen thin enough for TEM analysis because thick Nb layer tends to peel off easily when cutting to slices. Wafer "VJCB2" has been fabricated in the same plasma-oxidation condition (50 W rf-plasma, 15 mTorr×10 minutes) as "Crest 19" except using aluminum base electrode instead of Nb, fabricated particularly for TEM imaging purpose. Samples with higher plasma oxidation pressure (15 W, rf-plasma, 75 mTorr×10 minutes) have been also investigated by TEM imaging.

Let us first look at plasma oxide with 50 W oxidation power. Figure 3.4a shows a TEM image in a cross-sectional view with Nb electrode on top and the silicon substrate on the bottom. From TEM images, we could see a relatively continuous layer of Al film by its crystalline structures from aluminum oxide layer by its amorphous property. The Al and AlO<sub>x</sub> layers is about 5 nm and 4 nm thick, respectively. The Z-contrast image (Figure 3.5) also shows directly the difference between the heavy Nb electrode (Z=41), and the lighter Al, AlO<sub>x</sub>, and SiO<sub>2</sub> layers.

Similar structures are found for plasma oxide with 75 mTorr oxidation pressure, with a slightly thicker aluminum oxide thickness of 5 nm. The total thickness of Al/AlO<sub>x</sub> is about 10 nm. From the EELS plot (Figure 3.6), it is interesting to note here that the O K-edge signal in the AlO<sub>x</sub> film appears stronger than in the 50-W plasma sample ("VJCB2", Figure 3.5), indicating a higher O-concentration in the plasma grown AlO<sub>x</sub>-layers under higher pressure. Moreover, the Al L-edge of the AlO<sub>x</sub> layer shows a much stronger first peak, usually the sign of an amorphous oxide.

### 3.5 Electrical Characterization for $(Nb/)Al/AlO_x/Nb$ Barriers

Direct I-V measurements of both as-oxidized and annealed junctions have been carried out both at room and liquid-helium (4.2 K) temperatures. Volt-

Figure 3.4: High-resolution transmission-electron-microscope images of plasma-grown aluminum oxide layers with different oxygen exposures (a) 15 mTorr (b) 75 mTorr.

a. Z-contrast image of Sample VJCB2.

b. EELS spectra from the indicated layers.

Figure 3.5: Z-Contrast images and EELS spectroscopy of 15-mTorr plasmagrown aluminum oxide.

a. Z-contrast image of sample VJCB3.

b. EELS spectra from the position indicated in a.

Figure 3.6: Z-Contrast images and EELS spectroscopy of 75-mTorr plasmagrown aluminum oxide.