# **Stony Brook University**

# OFFICIAL COPY

The official electronic file of this thesis or dissertation is maintained by the University Libraries on behalf of The Graduate School at Stony Brook University.

© All Rights Reserved by Author.

# Scheduling divisible loads for parallel and real time systems, distributed networks, and computational grids

A Dissertation Presented

by

Taeyoung Lim

to

The Graduate School

in Partial Fulfillment of the

Requirements

for the Degree of

Doctor of Philosophy

in

Electrical Engineering

Stony Brook University

December 2007

#### Stony Brook University

The Graduate School

#### Taeyoung Lim

We, the dissertation committee for the above candidate for the Doctor of Philosophy degree, hereby recommend acceptance of this dissertation.

Thomas G. Robertazzi, Dissertation Advisor Professor, Department of Electrical & Computer Engineering

Sangjin Hong, Chairperson of Defense Associate Professor, Department of Electrical & Computer Engineering

Milutin Stanacevic, Assistant Professor, Department of Electrical & Computer Engineering

> Hussein Badr, Associate Professor, Department of Computer Science

This dissertation is accepted by the Graduate School

Lawrence Martin Dean of the Graduate School

#### Abstract of the Dissertation

Scheduling divisible loads for parallel and real time systems, distributed networks, and computational grids

by

Taeyoung Lim

Doctor of Philosophy

in

Electrical Engineering

Stony Brook University

2007

In this dissertation, four scheduling problems in parallel video processing systems, real-time systems, networks, and computational grids are considered.

Communication delay in a processor network is very critical to the throughput of a parallel video processing system. The interaction of communication and computation is examined here in a number of contexts. First, a simultaneous distribution and collection method (SD) from the root processor to children processors via a multiport switch network is proposed. For the proposed mechanism, we analyze the video encoding time and derive a closed-form solution for a multi-port star interconnect network. The results show that the total encoding time is significantly faster than a previous method, Parallel Interlaced (PI) [1], based on a bus network. In addition,

we achieve scalability in terms of the number of processors because of the concurrent communication.

The deleterious impact of communication on computation for computers is one of the factors that affect performance of computers in a network. A scheduling method considering this interference of communication on computation is proposed in detail and analyzed here from the perspective of divisible load theory in heterogeneous networks and grids. Each processor is divided into two virtual processors with different computing speeds according to the degree of overlapping communication. These two virtual processors are used to obtain one equivalent computing speed. Through this process we obtain the closed-form solution for the processing time considering the effect of communication on computation. In addition, interference aware scheduling is extended from sequential distribution to simultaneous distribution and applied to parallel video processing. A concurrent scheduling method considering communication interference (IA-COMP) reflects more realistic and accurate results in this specific application.

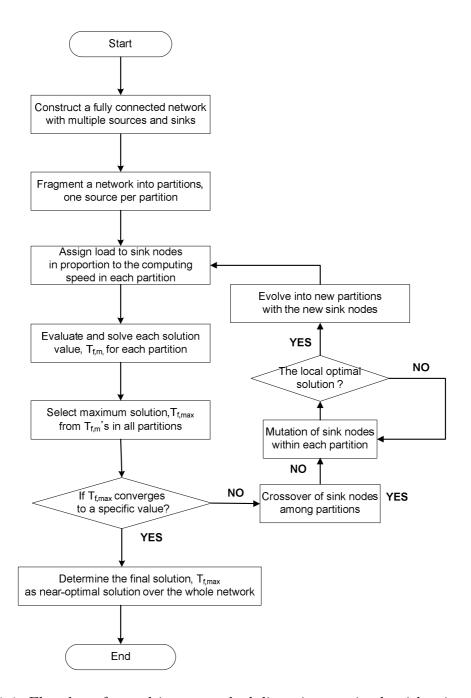

It will be increasingly common that multiple source nodes originate workload to sink nodes in very large heterogeneous networks. A multi-source scheduling scheme through network partitioning is proposed. All sink nodes are involved in only one partition associated with a single source node. In partitioning the network, the sum of computing speeds of the sink nodes in each partition should be similar to one another for the initial network partition. Each partition is evaluated by running an optimal single-source sequential load distribution scheduling method whenever network partitioning is repeated. After every evaluation, new partitions could be

constructed by transferring sink nodes from one partition to another or rearranging the sequence of sink nodes receiving load from the source node within a partition. We iterate this partitioning and evaluation via a genetic algorithm until a globally near-optimal solution is approached or obtained.

It has been increasingly important to provide performance guarantees to deadlineconstrained jobs originating from large scale experiments. To satisfy the deadline of workloads, computing and communication capability should be guaranteed and each workload should be estimated through a schedulability test before submission. In doing so, divisible load theory (DLT) has recently been extended with real-time characteristics, where the job with the earliest deadline is the first scheduled. However, such a method still is limited to only a homogeneous cluster environment. In this paper, scheduling heuristics involving network partitioning are proposed for large scale heterogeneous Grid/cluster systems. The minimum number of nodes obtained from a homogeneous model is used in two-level schedulability test of a job in the original heterogeneous system. The entire network is fragmented into small partitions, where the minimum number of children nodes are selected to be just large enough to satisfy the deadline of each job for each partition. Intensive simulations show that our proposed real-time scheduling method via DLT provides not only feasible solutions applicable to a heterogeneous system, but shows also good performance than in terms of the rejection ratio of jobs.

#### All glory to my Lord, Jesus Christ

To my late mother, Bunja Park and my father, Kyusu Lim,

To my wife, Eunjung Yoon and two sons, Konhah and Chanhah

# Contents

| Li | List of Figures x   |        |                                                                    |     |  |  |  |

|----|---------------------|--------|--------------------------------------------------------------------|-----|--|--|--|

| Li | List of Tables xiii |        |                                                                    |     |  |  |  |

| A  | cknov               | wledge | ments                                                              | xiv |  |  |  |

| 1  | Intr                | oducti | ion                                                                | 1   |  |  |  |

|    | 1.1                 | Backg  | round                                                              | 1   |  |  |  |

|    | 1.2                 | Motiva | ation                                                              | 3   |  |  |  |

|    | 1.3                 | Contri | bution                                                             | 4   |  |  |  |

|    | 1.4                 | Outlin | ıe                                                                 | 6   |  |  |  |

| 2  | Con                 | currer | nt Scheduling                                                      | 9   |  |  |  |

|    | 2.1                 | Concu  | rrent Communication In Parallel Video Processing                   | 12  |  |  |  |

|    |                     | 2.1.1  | Interconnect Topology                                              | 12  |  |  |  |

|    |                     | 2.1.2  | Scheduling Scenario                                                | 16  |  |  |  |

|    |                     | 2.1.3  | Notation                                                           | 17  |  |  |  |

|    | 2.2                 | Simult | caneous Distribution Scheduling (SD)                               | 18  |  |  |  |

|    |                     | 2.2.1  | No computation on the root processor (SD-NO) $\ \ldots \ \ldots$ . | 18  |  |  |  |

|    |                     | 2.2.2  | Computation on the root processor (SD-COMP)                        | 21  |  |  |  |

|    | 2.3                 | Perfor | mance Analysis And Comparison                                      | 26  |  |  |  |

|    |                     | 2.3.1  | Speedup of the SD-NO method                                        | 26  |  |  |  |

|   |      | 2.3.2   | Speedup of the SD-COMP method                          | 27 |

|---|------|---------|--------------------------------------------------------|----|

|   | 2.4  | Conclu  | usion                                                  | 29 |

| 3 | Inte | erferen | ce Aware Scheduling                                    | 31 |

|   | 3.1  | Seque   | ntial Distribution Model and definition                | 32 |

|   |      | 3.1.1   | Sequential distribution model for a heterogeneous tree | 32 |

|   |      | 3.1.2   | Notation                                               | 33 |

|   | 3.2  | Interfe | erence aware scheduling (IA)                           | 34 |

|   |      | 3.2.1   | Timing Diagram for Sequential Distribution             | 34 |

|   |      | 3.2.2   | Analytical solution                                    | 37 |

|   | 3.3  | Nume    | rical Solution and comparison                          | 44 |

|   |      | 3.3.1   | Numerical Solution Parameters                          | 44 |

|   |      | 3.3.2   | Numerical Solution Results                             | 44 |

|   | 3.4  | Interfe | erence Aware Scheduling In Parallel Video Processing   | 47 |

|   |      | 3.4.1   | Notation for the IA method                             | 47 |

|   |      | 3.4.2   | Interference aware scheduling (IA-COMP)                | 48 |

|   |      | 3.4.3   | Comparison of the SD-COMP and IA-COMP method           | 52 |

|   | 3.5  | Conclu  | usions                                                 | 55 |

| 4 | Mu   | lti-sou | rce scheduling                                         | 56 |

|   | 4.1  | Motiva  | ation                                                  | 56 |

|   | 4.2  | Multi-  | source scheduling in a large heterogeneous network     | 59 |

|   |      | 4.2.1   | Problem formulation and definition                     | 59 |

|   |      | 4.2.2   | Two source scheduling                                  | 61 |

|   |      | 4.2.3   | Network partitioning                                   | 64 |

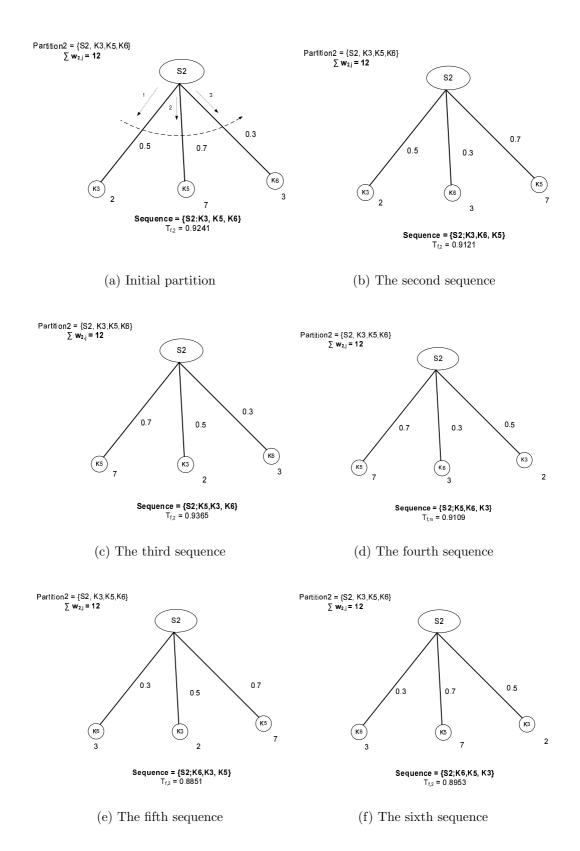

|   |     | 4.2.4  | Load distribution sequencing                             | 66  |

|---|-----|--------|----------------------------------------------------------|-----|

|   | 4.3 | Multi- | source scheduling via genetic algorithm                  | 71  |

|   |     | 4.3.1  | Genetic algorithm heuristics                             | 71  |

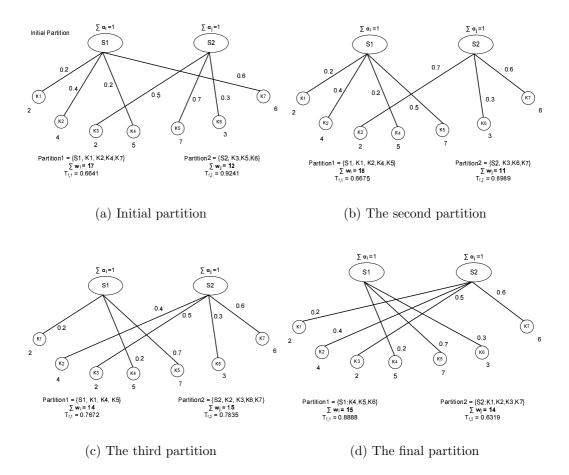

|   |     | 4.3.2  | Network partitioning via crossover operator              | 73  |

|   |     | 4.3.3  | Load sequencing via mutation operator                    | 75  |

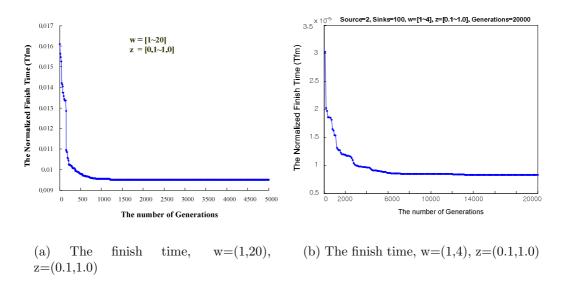

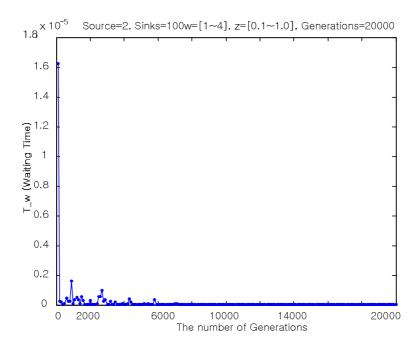

|   | 4.4 | Perfor | mance analysis and comparison                            | 78  |

|   | 4.5 | Conclu | asion                                                    | 80  |

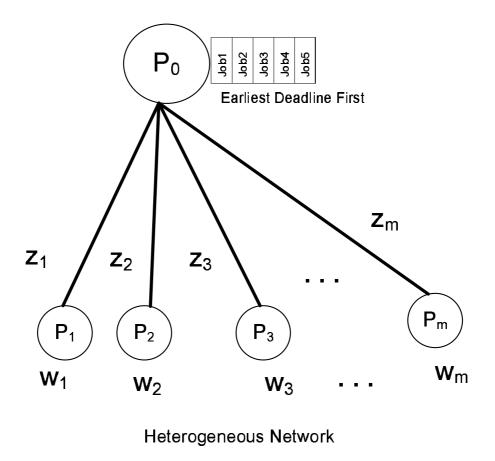

| 5 | Rea | l-time | scheduling                                               | 82  |

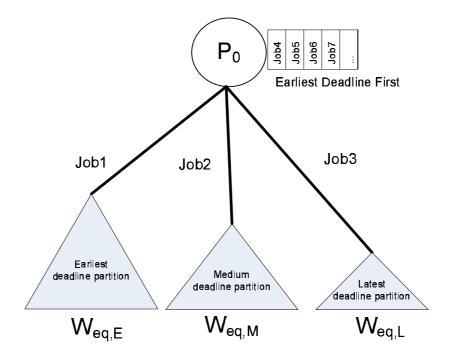

|   | 5.1 | Model  | s and problem description                                | 86  |

|   |     | 5.1.1  | Models and definition                                    | 86  |

|   |     | 5.1.2  | Problem description                                      | 88  |

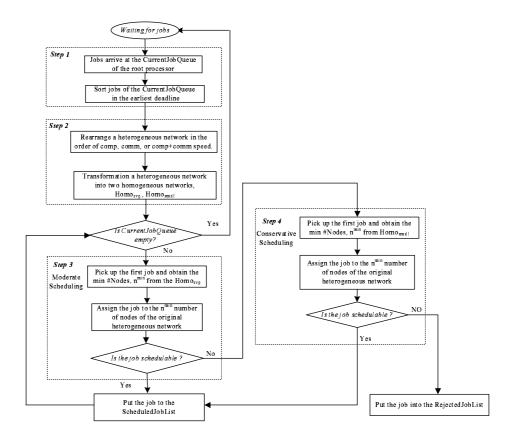

|   | 5.2 | Deadli | ine-constrained scheduling in a heterogeneous model      | 89  |

|   |     | 5.2.1  | Application specific scheduling in a heterogeneous model | 89  |

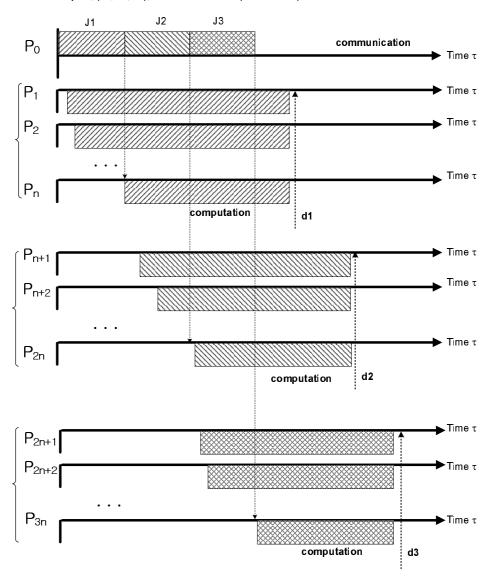

|   |     | 5.2.2  | Deadline-constrained network partitioning                | 93  |

|   | 5.3 | Perfor | mance analysis and comparison                            | 100 |

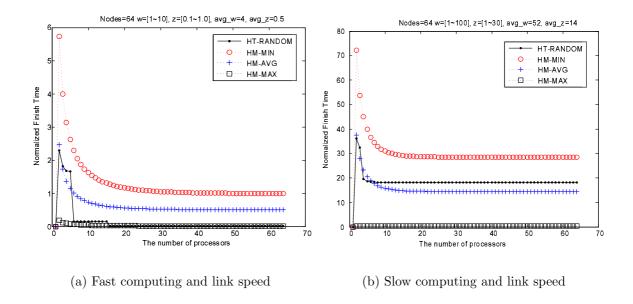

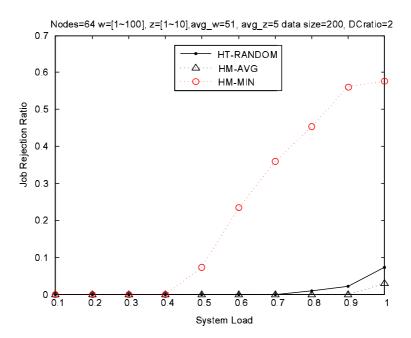

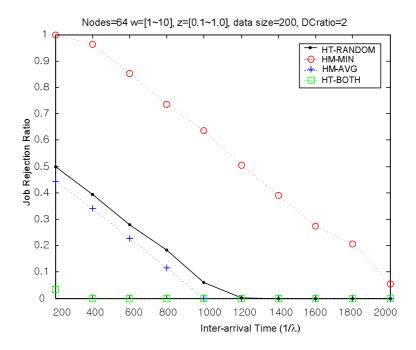

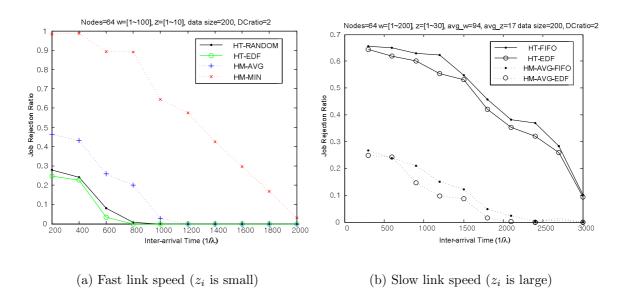

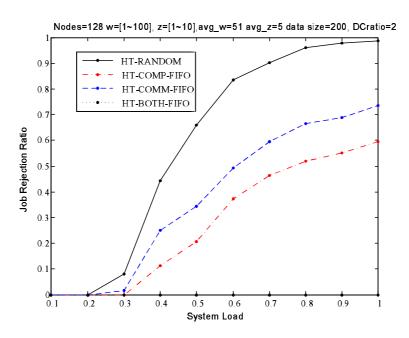

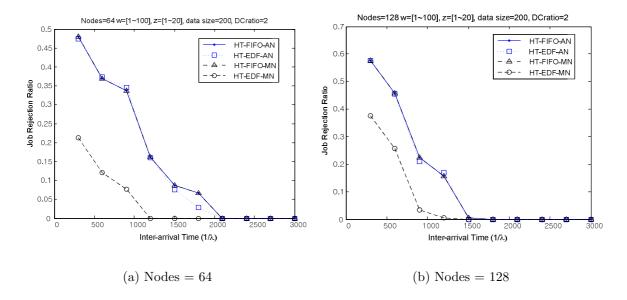

|   |     | 5.3.1  | Simulation parameters                                    | 100 |

|   |     | 5.3.2  | Performance analysis                                     | 100 |

|   | 5.4 | Conclu | asion                                                    | 107 |

| 6 | Fut | ure Re | search and Conclusion                                    | 109 |

|   | 6.1 | Conclu | asion                                                    | 109 |

|   | 6.2 | Future | e research                                               | 111 |

# List of Figures

| 1-1 | A multi-source heterogeneous Grid/cluster network configuration of       |    |

|-----|--------------------------------------------------------------------------|----|

|     | the ATLAS project                                                        | 3  |

| 2-1 | Block diagram for multi-port interconnection network                     | 12 |

| 2-2 | The simultaneous load distribution in a tree network                     | 16 |

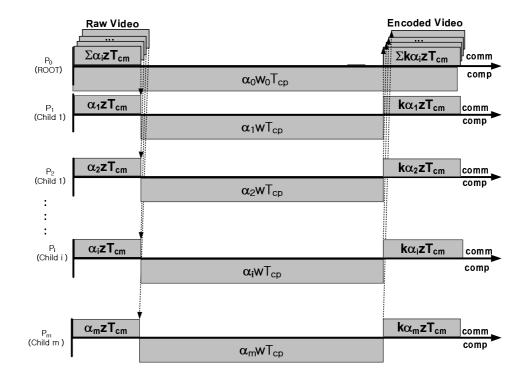

| 2-3 | The timing diagram for the SD-NO method                                  | 20 |

| 2-4 | The timing diagram for the SD-COMP method                                | 21 |

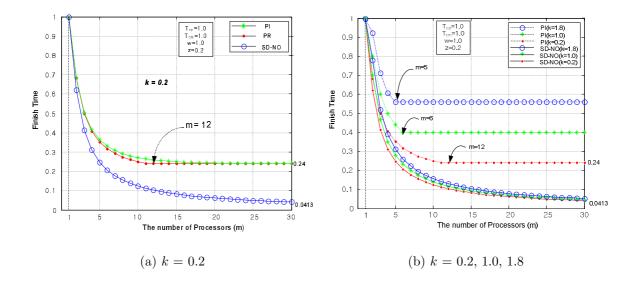

| 2-5 | The finish time versus the number of processors for SD-NO, PI and        |    |

|     | PR load scheduling methods                                               | 26 |

| 2-6 | The finish time versus the number of processors for SD-COMP, SD-NO,      |    |

|     | PI, and PR load scheduling methods on a homogeneous network              | 28 |

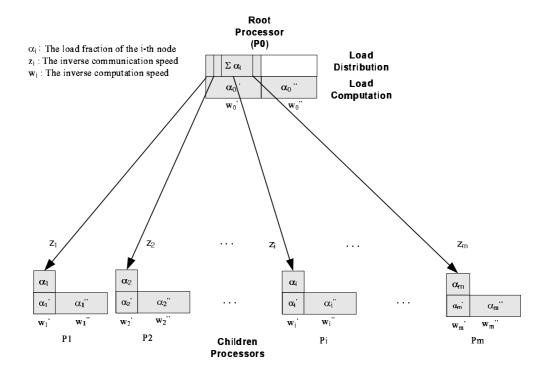

| 3-1 | Interference aware sequential load distribution in a tree topology       | 33 |

| 3-2 | Timing diagram for IA (Interference Aware) sequential distribution       |    |

|     | and simultaneous start                                                   | 35 |

| 3-3 | The equivalent processor concept for IA (interference aware) scheduling. | 40 |

| 3-4 | Timing diagram of the equivalent processor for Interference Aware se-    |    |

|     | quential distribution and simultaneous start scheduling                  | 41 |

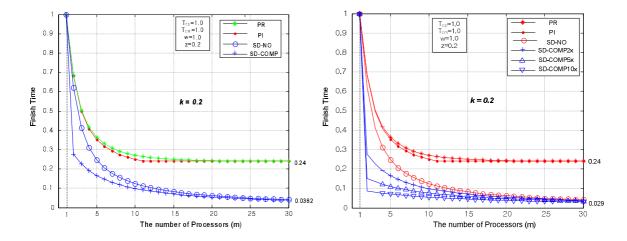

| 3-5 | The IA (Interference Aware) scheduling versus the SD (Sequential Dis-           |    |

|-----|---------------------------------------------------------------------------------|----|

|     | tribution) Scheduling                                                           | 45 |

| 3-6 | The IA (Interference aware) scheduling method versus than the SD                |    |

|     | (Sequential Distribution) method in terms of communication speed                | 46 |

| 3-7 | The timing diagram for the IA-COMP(Interference Aware scheduling                |    |

|     | with computation the root processor) method                                     | 50 |

| 3-8 | The SD-COMP scheduling method versus IA-COMP method                             | 53 |

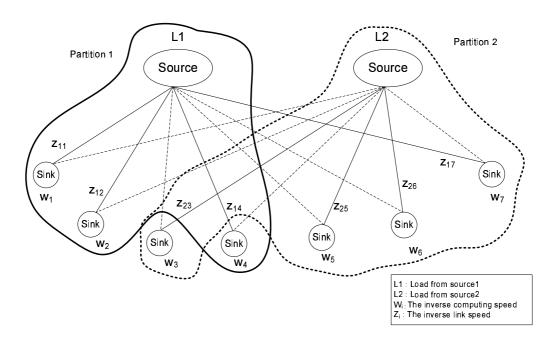

| 4-1 | Multi-source heterogeneous network                                              | 60 |

| 4-2 | Two partitions should be created so that the sum of the computing               |    |

|     | speed $(\frac{1}{w})$ of both partitions can be similar each other if possible  | 62 |

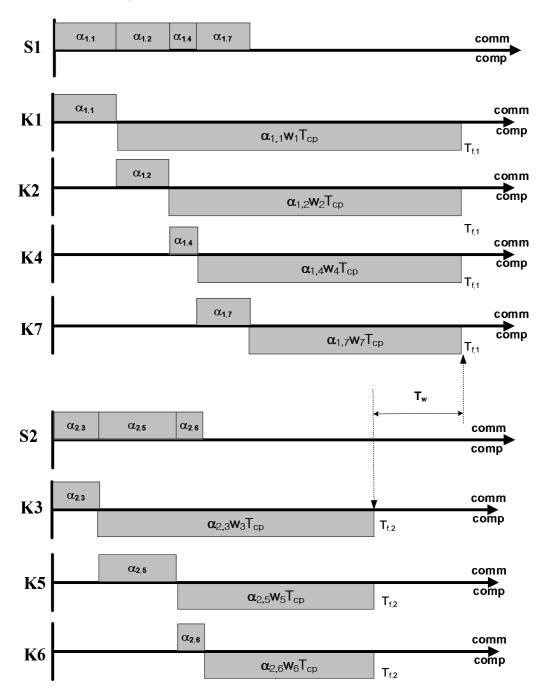

| 4-3 | Timing diagram for multi-source scheduling with sequential distribu-            |    |

|     | tion in a network with two source and seven sink nodes. $T_{f,1}$ and $T_{f,2}$ |    |

|     | are the finish times and $T_w$ is the waiting time                              | 63 |

| 4-4 | Flowchart for multi-source scheduling via genetic algorithm in grid             |    |

|     | network                                                                         | 67 |

| 4-5 | The network partitioning via the crossover operator                             | 74 |

| 4-6 | Node sequencing via the mutation operator                                       | 76 |

| 4-7 | The near-optimal solutions for the finish time, $T_{f,m}$                       | 78 |

| 4-8 | The near-optimal solutions for the waiting time, $Tw$                           | 80 |

| 5-1 | A heterogeneous Grid/cluster system example, TeraPaths network con-             |    |

|     | figuration of the ATLAS project                                                 | 84 |

| 5-2 | A heterogeneous model with deadline-constrained jobs                            | 90 |

| <b>3-3</b> | I liming diagram for a neterogeneous model                             | 91  |

|------------|------------------------------------------------------------------------|-----|

| 5-4        | Transformation of a heterogeneous network into a homogeneous network   | 93  |

| 5-5        | Deadline-constrained network partitioning in a heterogeneous tree net- |     |

|            | work                                                                   | 96  |

| 5-6        | Timing diagram for deadline-constrained network partitioning in a het- |     |

|            | erogeneous tree network                                                | 97  |

| 5-7        | Two-level schedulability test in a heterogeneous model                 | 98  |

| 5-8        | The finish time for heterogeneous and transformed homogeneous models.  | 103 |

| 5-9        | The rejection ratio for heterogeneous and transformed homogeneous      |     |

|            | models with the system load                                            | 103 |

| 5-10       | The rejection ratio for heterogeneous and transformed homogeneous      |     |

|            | models with inter-arrival time $(1/\lambda)$                           | 104 |

| 5-11       | EDF versus FIFO in a heterogeneous and homogeneous model               | 105 |

| 5-12       | The rejection ratio of application specific heterogeneous systems      | 106 |

| 5-13       | Minimum nodes network partitioning in a heterogeneous model            | 107 |

| 6-1        | Multi-source real-time scheduling scenario                             | 111 |

# List of Tables

| 2.1 | The Properties of topologies. $'n'$ : a dimension of Hypercube, $'p'$ : |     |

|-----|-------------------------------------------------------------------------|-----|

|     | the number of nodes along one edge of Mesh and Torus, $'h'$ : the       |     |

|     | height of the binary tree. (K. Hwang et al. [2], Duato et al. [3],      |     |

|     | http://www.netlib.org/benchmark/top500~[4]).                            | 13  |

| 3.1 | The ratio of SD-COMP to IA-COMP method in terms of finish time          |     |

|     | for the number of processors                                            | 54  |

| 3.2 | The ratio of SD-COMP to IA-COMP method in terms of finish time          |     |

|     | with communication speed decreased                                      | 54  |

| 5.1 | The notations for the algorithms tested in the simulation               | 101 |

## Acknowledgements

With the help of my wonderful advisor, Professor Thomas G. Robertazzi, I can stand here and express this thanks now. He has been considerate in inspiring me to investigate new problems as well as scrupulous in proofreading all of the papers including the dissertation. He has shown the role model to be followed as a real scholar and researcher.

I would like to thank the committee members of the final defense, Professor Sangjin Hong, Hussein Badr, and Milutin Stanacevic for their invaluable comments on the this dissertation. Especially, the assistance of Professor Hong is very appreciated. I am thankful to Professor Petar M. Djurić for providing facilities and to the colleagues in the COSINE Laboratory and to the Korean colleagues in the department of Electrical and Computer Engineering, Stony Brook University. The assistance of Dr. Jason Hung in developing equations and Kyoung-su Park in programming experiments is very helpful.

My thanks should go to Dr. Dantong Yu and Dr. Dimitrios Katramatos in the Grid Group, BNL(Brookhaven National Laboratory). Through the TeraPaths project I has involved in BNL, my works are truly motivated and get more fruitful in the last two main chapters.

I am also grateful to the current and old members who I has met in the Nanume church, especially to the pastor, Tae Jun Suk, elders and deacons and small group members. They have prayed for me every turning point of study abroad that I has been either by the rivers of water or in the valley of the shadow.

In general, I would like to thank my family for love and prayer during the Ph.D

study. Especially, my late mother, Bunja Park poured out her love to my spirit and

from her I inherited my faith in God. My father, Kyusu Lim and the parents-in-law,

Kyungsim Park and Yeosung Yoon have been praying for my study day and night. I

also want to share the joy with the family members and friends, especially the sister,

Miae Lim.

Last, but not least, I must give special thanks to my wife, Eunjung Yoon and two

sons, Konhah and Chanhah who have gone through this challengeable journey with

overflowing love and confidence and made me happy all the way.

December 2007

Stony Brook, NY

Taeyoung Lim

The gospel to the poor;

To heal the brokenhearted.

$(Luke\ 4:18,19)$

# Chapter 1

### Introduction

#### 1.1 Background

In this dissertation, four outstanding scheduling problems and their performance modelings are considered.

First, in parallel video processing, various scheduling algorithms to assign video frames to multiple processors have been presented to find both the maximum processing throughput and I/O utilization. Load (video frame) partition schemes through DLT (divisible load theory) are shown to obtain a good performance in parallel video encoding [5]. However the scheduling algorithms based on sequential communication have inherent limitations on communication in terms of throughput and the optimal number of processors. Concurrent scheduling algorithms on concurrent communication and a star and tree network topology are investigated using divisible load analysis [6,7], since the star and tree topology is a good solution for master-worker style of parallel applications with independent divisible tasks.

Second, when both communication and computation on each processor are executed simultaneously, the computing capability experiences degradation due to the impact of communication on the same processor in networks and grids. It is meaningful to model communication interference on computation with estimating computing power more accurately in the presence of interference in networks and grids.

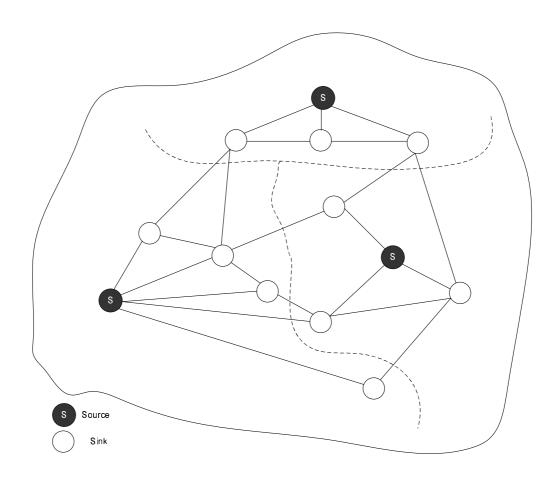

The third problem involves very large heterogeneous networks. Here, it will be increasingly common that multiple source nodes create and originate large amounts of data (workload) and any sink node can receive data from one of a number of source nodes. For high energy and nuclear physics experiments, large amounts of data originate from distant experiments. Such data requires a high computational power and network based computing platforms in these types of experiments. Minimizing the time to process workload originated from various sources presents a great challenge that could give rise to a range of new applications.

Finally, it has been also important to provide performance guarantees to deadline-constrained jobs originating from large scale experiments. To efficiently cope with these heavy workloads, divisible load theory (DLT) with real-time characteristics has been recently important in a heterogeneous grid/cluster systems, where the job with the earliest deadline is first scheduled. grid systems are inherently heterogeneous, since the different nodes in each site are connected to one another with different link speeds. A major trend is that cluster systems are also heterogeneous in the computing capability as well as in the link speed, the so-called heterogeneous cluster systems [8].

#### 1.2 Motivation

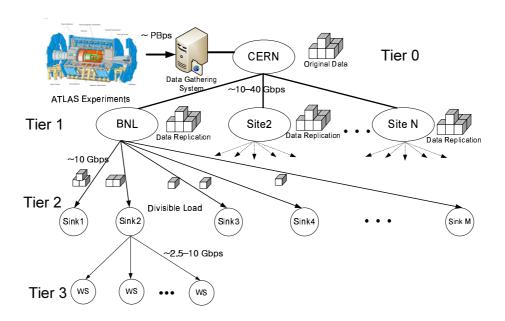

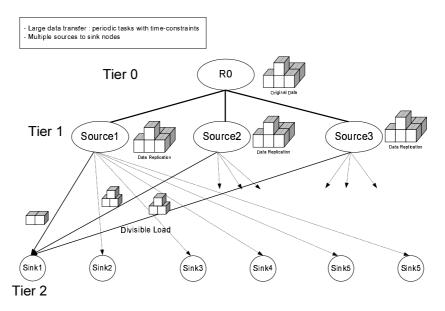

Figure 1-1: A multi-source heterogeneous Grid/cluster network configuration of the ATLAS project.

For high energy and nuclear physics experiments, large amounts of data originate from distant experiments. For example, a couple of universities in tier-2 sites should connected through a couple of WAN (wide area network)s to BNL (Brookhaven National Laboratory) in the ATLAS project [9,10] as shown in Fig 1-1. In this configuration, large bulk data can be delivered from multiple sites in tier-1 to a site in tier-2. Also, each site can have heterogeneous cluster systems with different computing capability and there is a heterogeneous computing and link capability even within each cluster system. Specifically, the hardware of RACF (RHIC ATLAS Computing Facility) of STAR project consists of a combination of commodity-based processing servers, enterprise class UNIX servers and highly-specialized mass storage systems connected together by a high-speed network infrastructure. The RACF is an exam-

ple of heterogeneous system with currently over 4000 processors and different link speeds. Such data require a high computational power and network based computing platforms. To satisfy the deadline of each job, sophisticated scheduling algorithms with respect to deadlines are needed. All of these recently emerging platforms require a sophisticated scheduling strategy to efficiently make use of distributed computers, high-speed networks and storage resources in terms of deadlines.

#### 1.3 Contribution

For concurrent scheduling in parallel video processing, three contributions are made. First, a concurrent scheduling policy is significant for showing not only a more efficient scheduling method for parallel video encoding but also good scalability in the number of processors. Second, the extensive discussion here relating various interconnection topologies to this work should be of interest to other researchers. Third, the choice of scheduling policy has a greater impact on performance than whether or not the root node does computation for the network considered in this work. All in all divisible load modeling as it has been developed for parallel video processing by researchers including ourselves, has been shown to be a useful and cost effective tool for system performance prediction.

As for interference aware scheduling with sequential distribution in a tree topology, the following contributions are made: First, interference aware (IA) scheduling can be analytically modeled. Optimal load allocations, speedup and makespan are found in closed form equation. Second, interference aware scheduling produces a realistic modeling with a larger makespan and smaller speedup than modeling that does not take communication interference into account. Third, the results and policies with a tree topology here can be extended to other scheduling policies and interconnection topologies.

For multi-source scheduling, a specific network partitioning technique via the use of a genetic algorithm is proposed. The network is fragmented into several partitions matching the number of source nodes. Computation in each partition is independently performed on a single source and multiple sink nodes. That is, a complicated problem for multi-source scheduling is simplified into several single source scheduling problems after network partitioning. Through this algorithm we can obtain the effect of the concurrent communication with simultaneous distribution policy.

For deadline-constrained scheduling, real-time modeling from the perspective of DLT (divisible load theory) and application specific scheduling algorithms are proposed in a fully heterogeneous Gird/cluster systems. The minimum number of nodes obtained through a homogeneous model to satisfy the deadline of a job is applied to network partitioning. Through application specific scheduling it is possible to adapt the sequence of load distribution to the characteristics of a job. To enhance network performance guarantee for deadline constrained jobs, every job is scheduled with DLT (divisible load theory) and the EDF (earliest deadline first) policy where each job is sorted in the order of the earliest deadline to be evaluated if each job is schedulable within its deadline.

#### 1.4 Outline

In this dissertation, four kinds of different scheduling methods, concurrent scheduling and interference aware scheduling, multi-source scheduling, and deadline-constrained scheduling algorithms are proposed for parallel system and fully heterogeneous grid networks. These algorithms deal with concurrent communication in parallel video processing, communication interference on processing, workloads originating from multiple sources, and deadlines in real-time systems, respectively. The primary network is a fully heterogeneous tree network which is commonly used in parallel/cluster systems and grid networks.

In chapter 2, a simultaneous distribution scheduling method for parallel video processing based on multi-port communication is proposed. Here we discuss an efficient scheduling mechanism, SD (Simultaneous Distribution), for parallel video processing which distributes raw video loads and collects encoded video results concurrently among the root (control) processor and each child worker processor in a star topology with a multi-port interconnect. We consider two cases: one is that load is assigned to the root processor (SD-COMP) and the other is that no load is assigned to the root processor (SD-NO). For the two cases, we obtain closed-form solutions for the total video processing time, and then compare these results in terms of the performance under the optimal number of processors which is proposed for previous scheduling algorithms, such as PI and PR [1, 11]. Both of the two cases using our strategies show much better performance in video processing and several times less finish time for the parameters we use than those under the optimal number

of processors of previous methods, such as PI and PR. From the practical point of view, feasible hardware interconnect networks, such as fat-tree or a multi-port tree network, are investigated and proposed for concurrent scheduling methods in parallel video processing.

In chapter 3, we consider communication interference on computation and propose Interference aware (IA) scheduling method to realistically model sequential distribution in a tree network. It is a very common situation in networks and grids that both communication and computation on each processor are executed simultaneously. When the impact of communication in sending or receiving load is considered, the traditional divisible load sequential distribution model should be modified. In this paper we analytically develop an optimal scheduling policy in the presence of interference of communication on computation for the sequential distribution and simultaneous start scheduling method which is one of traditional DLT (divisible load theory) models [12,13]. This particular load distribution policy is chosen for illustrative purposescertainly other scheduling policies could be modeled in an interference aware context. In addition, the interference aware scheduling method considering concurrent communication (IA-COMP) is proposed and applied to parallel video processing. The IA-COMP method shows a little bit slow finish time due to the communication interference than the SD-COMP method, but the IA-COMP is found to be more realistic and accurate modeling.

In chapter 4, a multi-source scheduling scheme through network partitioning is proposed. All sink nodes are involved in only one partition associated with a single source node. In partitioning the network, the sum of computing speeds of the sink nodes in each partition should be similar one another for the initial network partition. Each partition is evaluated by running an optimal single-source sequential load distribution scheduling method whenever network partitioning is repeated. After every evaluation, new partitions could be constructed by transferring sink nodes from one partition to another or rearranging the sequence of sink nodes receiving load from the source node within a partition. We iterate this partitioning and evaluation via a genetic algorithm until a globally near-optimal solution is approached or obtained.

In chapter 5, divisible load theory (DLT) has been extended with real-time characteristics, where the job with the earliest deadline is the first scheduled. To satisfy the deadline of workloads, computing and communication capability should be guaranteed and each workload should be estimated through a schedulability test before submission. In this chapter, deadline-constrained network partitioning scheduling is proposed for large scale heterogeneous grid/cluster systems. The minimum number of nodes obtained from a homogeneous model is used in testing the schedulability of a job in the original heterogeneous system. The entire network is fragmented into small partitions with the minimum number of processors for each job with deadline constraint, where the minimum number of children nodes are selected to be just enough to satisfy the deadline of each job.

# Chapter 2

# Concurrent Scheduling

In parallel video processing, various scheduling algorithms have been presented such as PI (parallel interlaced) and PR (parallel recursive) which can assign video frames to multiple processors. For these two algorithms other researchers [1,11] found both the maximum processing throughput and I/O utilization, and the optimal number of processors for each of algorithms under a bus architecture, using divisible load analysis [6,7]. However the scheduling algorithms have inherent limitations of a bus architecture on communication in terms of throughput and the optimal number of processors.

A scheduling method considering result collection as well as load distribution overheads was first proposed by Barlas [14] in modeling the divisible load like video processing and database query processing. Those applications are based on architecture which shares a single communication channel and which is modeled on a tree topology which consists of the single root node and several children nodes. In [5], divisible load like video frames are considered with respect to software functional-

ity to minimize the processing time of the video encoding on a bus architecture. Each video frame is divided into 16 x 16 blocks and each block is distributed to children processors. Since software functionality like motion estimation demanding much time is performed for each divided block on each child processor, this load partition scheme obtains a good performance in parallel video encoding. Results and problems in scheduling divisible load on a star and tree network (including a bus architecture) were covered in [15]. The authors show that the star and tree topology is a good solution for master-worker style of parallel applications with independent divisible tasks.

Here, we propose an efficient scheduling mechanism, SD (Simultaneous Distribution), for parallel video processing which distributes raw video loads and collects encoded video results concurrently among the root (control) processor and each child worker processor in a star topology with a multi-port interconnect. Note that simultaneous distribution was proposed by Piriyakumar and Murthy [16] and analyzed by Hung and Robertazzi [17]. We consider two cases: one is that load is assigned to the root processor and the other is that no load is assigned to the root processor. For the two cases, we obtain closed-form solutions for the total video processing time, and then compare these results in terms of the performance under the optimal number of processors which is proposed for previous scheduling algorithms, such as PI and PR [1,11]. Both of the two cases using our strategies show much better performance in video processing and several times less finish time for the parameters we use than those under the optimal number of processors of previous methods, such as PI and PR. In terms of the number of scalable processors, our proposed method, SD, reaches

up more than twice the optimal number of processors of PI or PR .

Of practical interest is that we propose a multi-port star topology among the root (control) processor and children worker processors. This means that the control processor has ports to each of the children processors for I/O communication. One of the reasons to select the multi-port star topology is that there is only communication between the root processor and each of children processors without communication among children processors. The other aspect is that the star topology is cost effective model for parallel video processing and relatively simple to implement compared with other complex architectures, such as 2D meshes, or Hypercubes.

We know that when the number of processors is small, the factors that affect the total processing time are the method to distribute and collect load as well as the root processor participation in computation. As the number of processors increases, all of the simultaneous scheduling methods (SD) show better performance than each of the sequential scheduling methods, such as PI or PR, because all of the SD methods have good scalability. However when the number of processors is 30, the performance improvement of the SD-COMP method (SD with computation) is 6 times as much as that of the sequential distribution method, PI. As for the SD-NO (SD with NO computation) method, the improvement of the SD-COMP with respect to SD-NO is just 1.3 times better. This is because the most critical part in efficient load distribution is how to distribute and collect load rather than whether or not the root processor involves load computation, when the number of processors is large enough to process the whole load.

# 2.1 Concurrent Communication In Parallel Video Processing

#### 2.1.1 Interconnect Topology

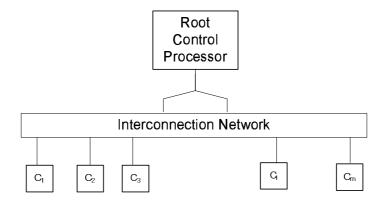

Figure 2-1: Block diagram for multi-port interconnection network.

In this section, a one-to-many interconnect is considered, which consists of one root (control) processor with multiple ports and m children processors. The root (control) processor distributes raw video data (load) and collects the encoded video data (results) to/from each child processor simultaneously via multiple ports. While the children processors encode the video, the root processor waits for the encoded video data from each child processor.

From the perspective of hardware implementation, the above interconnect can be logically modeled on various topologies such as a star, fat tree, hypercube, and mesh/torus topology. For a hypercube topology, the simultaneous use of links was proposed to obtain faster communication and it was found that there is no need to use all the processors to obtain an optimal solution. In this hypercube topology

each processor needs multiple ports, for example, 8 ports in the Intel~iPSC/860, to concurrently communicate each other [18]. For a 3D-mesh topology, we can use multiple links to simultaneously communicate, but its ports are constrained 1 to 6 in commercially available computers, such as the Cray~X3D. Similarly in the Cray~XT3 computer using a 3D-torus topology, each processor has 6 ports [19, 20].

The above hypercube and 3D-mesh, 3D-torus interconnects are not appropriate for parallel video processing using our methods as all of the processors in the networks have multiple ports. Our star topology requires each child processor to have only one port. The root processor in our scheduling methods is the only processor to have multiple ports. Therefore we take into account more suitable solutions for our scheduling method based on a master-slave structure and analyze the complexity, feasibility, and cost-effectiveness in terms of the implementation point of view.

| Topology              | # of Node     | # of Links     | Degree | Network                        | Model         |

|-----------------------|---------------|----------------|--------|--------------------------------|---------------|

|                       |               |                |        | Diameter                       |               |

| Hypercube             | $N=2^n$       | $n\frac{N}{2}$ | n      | n                              | Intel iPSC    |

| 3D-Mesh               | $N = p^{(3)}$ | $3p^2(p-1)$    | 4 6    | 3(p-1)                         | Cray X3D      |

| 3D-Torus              | $N = p^{(3)}$ | $3p^{(3)}$     | 6      | $3\lfloor \frac{p}{3} \rfloor$ | Cray XT3      |

| Binary Fat-           | $N = 2^h - 1$ | N-1            | 3      | $2(\log_2 N - 1)$              | CM5           |

| tree                  |               |                |        |                                |               |

| $\operatorname{Star}$ | N             | N-1            | N-1    | 2                              | $Cray\ XD1$   |

| Multi-port            | N             | N-1            | N-1    | 2                              | $IBM\ RS6000$ |

| Memory                |               |                |        |                                |               |

| Optical               | N             | N              | 1      | 1                              | Cray T90      |

| BUS                   |               |                |        |                                |               |

Table 2.1: The Properties of topologies. 'n': a dimension of Hypercube, 'p': the number of nodes along one edge of Mesh and Torus, 'h': the height of the binary tree.  $(K.Hwang\ et\ al.\ [2],\ Duato\ et\ al.\ [3],\ http://www.netlib.org/benchmark/top500\ [4]).$

In previous work, we proposed a method which has output buffers in the root

processor to be used for output ports as a way to implement simultaneous communication [17]. This can be implemented via multi-port memory as long as each child processor has a different memory partition in the root processor.

In a star topology, the root processor uses multiple ports with a direct interconnect to simultaneously communicate with children processor. For example, there are switching devices which support 12 communication ports per chassis and can be expanded to several hundreds of processors in commercially manufactured system like Cray XD1 [20]. In this star topology the root node only has multiple ports and so it can be suitable for parallel video processing applications in terms of cost-effectiveness. This is because resources like the frame buffer in which raw and encoded image data are stored, are placed at the root node and only accessed through the root processor by all children processors in a star topology. The root node sends and receives data to or from a port of each child and then simply extracts or stores the data from the port to the frame buffer. Extending the star topology means increasing the fan-out of the root node. This makes the growth complexity one, which is better than most of other topologies such as 3D-Mesh, 3D-Torus, and Hypercube. The root node has to be modified in order to cope with an extra node, while all the other nodes can remain unchanged. A disadvantage of this topology lies in the fact that the root processor can become a communication bottleneck. However, since there is little communication among children processors in our proposed scheduling methods, this communication bottleneck does not significantly affect the overall performance.

In a fat tree topology, processors are located at the terminal nodes and switches are at the internal nodes. Transmission bandwidth in a fat-tree is increased by adding more links as nodes moves up the tree close to the root. For example, to alleviate the bottleneck of nodes close to the root node the commercial model CM5 used a four-way interconnect for each node to have four children nodes. If we only consider the performance, a fat-tree topology can be a good alternative to our methods. However, with respect to cost-effectiveness this topology requires more switches and links to connect processors than those of a star topology.

On the other hand, we can consider a optical bus topology to satisfy the simultaneous communication on the bus architecture in implementing our parallel video processing application. For example, the Jitney Optical Bus with 20 channels (500Mb/s/ch) has been designed for high speed parallel computing and successfully demonstrated in IBM AS/400 and RS6000 power parallel systems test-beds [21]. Meanwhile, as system frequencies move into from the MHz range to the GHz range, shared buses are generally migrated into point-to-point switches. Implementing switches within a chip limits the number of ports per chip to 6 or 8 ports. Currently, optical interconnect is generally used in packet-switched point-to-point network topologies, such as 3D Torus and fat-tree. Nevertheless, the models with reconfigurable optical buses are likely to become feasible architectures in the near future [22].

In summary, although there are tradeoffs, star and tree architectures are most feasible for our proposed scheduling methods in video processing from the costeffectiveness point of view.

#### 2.1.2 Scheduling Scenario

We have two scenarios for simultaneous scheduling. The first scenario is for the root processor to only distribute and collect load without computation. This is because we try to compare its performance with the sequential method in previous papers [3, 4]. Here we assume that our multi-port star network is homogeneous, which means all of the children processors are identical in terms of the computing speed. In addition, the communication speed between the root processor and each child processor is also identical. The other case is for the root processor to do both communication, such as load distribution and result collection, and some of the computation (video encoding). Here we assume that all of the children processors are homogeneous in terms of computing speed and communication speed as in the previous scenario, but the root processor speed can be different from the children's speed.

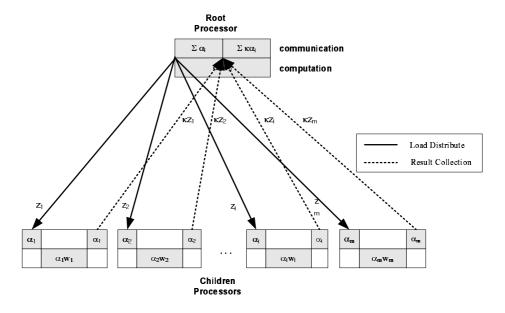

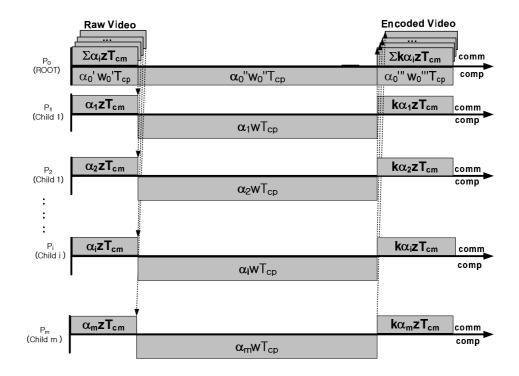

Figure 2-2: The simultaneous load distribution in a tree network.

In Fig. 2-2, the value of k' is defined as the ratio of the amount of result (an

encoded video) obtained from each child processor to the amount of load sent (an original raw video). That is, the fraction of load may or may not be assigned to the root processor. If it is assigned, the root processor not only distributes load and collects results to/from each child processor, but also joins computation itself. Otherwise, the root processor just distributes and collects load. Here 'k' is the ratio of the result received to the original load sent.

$$k = \frac{result\_received}{load\_sent}$$

We have the three cases as follows:

- k = 1, if the amount of load sent is same as the amount of result received.

- k < 1, if the amount of load sent is greater than the amount of result received. This case is typical in digital video processing due to compression.

- k > 1, if the amount of load sent is less than the amount of result received.

#### 2.1.3 Notation

The variables we will use in the following are based on work in the papers [6,7,11].

$\alpha_i$ : The load fraction assigned to the *i*th link-processor pair (where  $i = 0, 1, 2, \dots, m$ ).

$w_i$ : The inverse computing speed at the *i*th processor (where  $i=0,1,2,\ldots,m$ ).

$z_i$ : The inverse communication speed on the *i*th link (where  $i=0,1,2,\ldots,m$ ).

$T_{cp}$ : Computing intensity constant.

$T_{cm}$ : Communication intensity constant.

$\mathcal{T}_{f,m}$  : The finish time. Time at which each processor completes computation.

Then  $\alpha_i w_i T_{cp}$  is the time to process the fraction i of the entire load on the ith processor. Note that the units of  $\alpha_i w_i T_{cp}$  are [load] x [time/load] x [dimensionless quantity] = time. Likewise,  $\alpha_i z_i T_{cm}$  is the time to transmit the fraction i of the entire load over the ith link. Our goal is to propose more efficient scheduling methods and analyze the solution in parallel video processing through concurrent communication.

#### 2.2 Simultaneous Distribution Scheduling (SD)

We assume that the root processor has a faster computing speed than that of the children processors, while all of the children are identical in terms of computing speed and link speed. We consider the case of a homogenous processor network, which means all children processors except the root processor are identical. ; the inverse processor speed is  $w_1 = w_2 = \ldots = w_m = w$  and the inverse network speed is  $z_1 = z_2 = \ldots = z_m = z$ .

#### 2.2.1 No computation on the root processor (SD-NO)

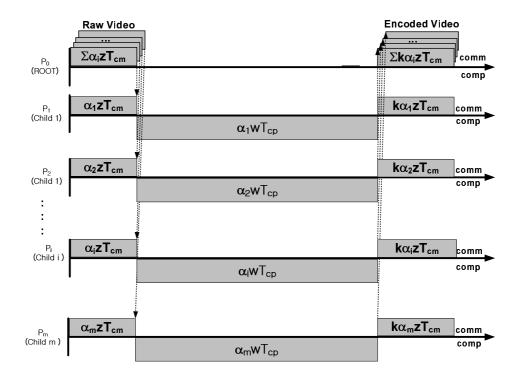

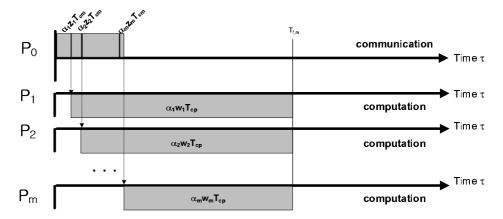

In this strategy the root processor does not join computation by itself, but just distributes load and collects results to/from the children processors. The timing diagram for concurrent scheduling is shown in Fig. 2-3, which distributes load simultaneously to the children processors. Here the root processor does not execute computation in itself, but just distributes and collects load. In all of the scheduling policies to be

considered we force all activities to terminate at the same time instant, as otherwise load could be redistributed for a better solution [12,13]. From the timing diagram for SD-NO, as shown in Fig. 2-3, the equations for SD-NO scheduling are obtained as follows.

$$\alpha_1 z T_{cm} + \alpha_1 w T_{cp} + \alpha_1 k z T_{cm} = \alpha_2 z T_{cm} + \alpha_2 w T_{cp} + \alpha_2 k z T_{cm}$$

(2.1)

$$\alpha_1 = \frac{(z+kz)T_{cm} + wT_{cp}}{(z+kz)T_{cm} + wT_{cp}}\alpha_2 = \alpha_2$$

(2.2)

From equation (2.2), we deduce as follows:

$$\alpha_1 = \alpha_2 = \alpha_3 = \dots = \alpha_m \tag{2.3}$$

The normalization equation that all of the load fractions is summed up 1 is

$$\sum_{i=1}^{m} \alpha_i = 1 \tag{2.4}$$

From equation (2.3) and (2.4), we obtain

$$\alpha_1 \times m = 1, \qquad \alpha_1 = \frac{1}{m} \tag{2.5}$$

Figure 2-3: The timing diagram for the SD-NO method.

$$\alpha_m \times m = 1, \qquad \alpha_m = \frac{1}{m}$$

(2.6)

The total processing time for the entire load,  $T_{f,m}$  is achieved as

$$T_{f,m} = \alpha_1 z T_{cm} + \alpha_1 w T_{cp} + \alpha_1 k z T_{cm} = \alpha_1 (1 + \sigma + k \sigma) w T_{cp}$$

$$where \quad \sigma = \frac{z T_{cm}}{w T_{cp}}$$

(2.7)

From the above equation (2.5), the total processing time,  $T_{f,m}$  can be rewritten as follows:

$$T_{f,m} = \frac{(1+\sigma+k\sigma)}{m} w T_{cp} \tag{2.8}$$

Our finding is that the total processing time decreases in inverse proportion to the number of children processors.

### 2.2.2 Computation on the root processor (SD-COMP)

In the case load is assigned to the root processor and some computation is done on the root processor itself. As for the root processor, the processor speed is greater than those of children processors, which means the inverse value of the root processor,  $w_0$ , is less than w.

Figure 2-4: The timing diagram for the SD-COMP method.

The SD-COMP scheduling method is illustrated in Fig. 2-4, where load is simultaneously distributed to the children processors and the root (control) processor computes load assigned to itself as well as distributes and collects load. From the

timing diagram in Fig. 2-4, the equations for the SD-COMP method, in which the root processor has load assigned, are obtained as follows:

$$\alpha_0 w_0 T_{cp} = \alpha_1 z_1 T_{cm} + \alpha_1 w_1 T_{cp} + \alpha_1 k z_1 T_{cm}$$

(2.9)

$$\alpha_1 z_1 T_{cm} + \alpha_1 w_1 T_{cp} + \alpha_1 k z_1 T_{cm} = \alpha_2 z_2 T_{cm} + \alpha_2 w_2 T_{cp} + \alpha_2 k z_2 T_{cm}$$

(2.10)

. . .

$$\alpha_{m-1}z_{m-1}T_{cm} + \alpha_{m-1}w_{m-1}T_{cp} + \alpha_{m-1}kz_{m-1}T_{cm}$$

$$= \alpha_m z_m T_{cm} + \alpha_m w_m T_{cp} + \alpha_m kz_m T_{cm}$$

(2.11)

The normalization equation is different from the previous one in the SD-NO method, in that the load fraction to the root processor,  $\alpha_0$  is added as follows

$$\alpha_0 + \alpha_1 + \alpha_2 + \ldots + \alpha_m = 1 \tag{2.12}$$

From equation (2.9),

$$\alpha_0 = \frac{[(z_1 + kz_1)T_{cm} + w_1T_{cp}]}{w_0T_{cp}}\alpha_1 = \frac{1}{\gamma_1}\alpha_1$$

$$where \quad \gamma_1 = \frac{w_0T_{cp}}{[(z_1 + kz_1)T_{cm} + w_1T_{cp}]}$$

(2.13)

From equation (2.11),

$$\alpha_{i} = \frac{\left[w_{i-1}T_{cp} + (z_{i-1} + kz_{i-1})T_{cm}\right]}{w_{i}T_{cp} + (z_{i} + kz_{i})T_{cm}} \alpha_{i-1} = q_{i}\alpha_{i-1}$$

$$where q_{i} = \frac{\left[w_{i-1}T_{cp} + (z_{i-1} + kz_{i-1})T_{cm}\right]}{w_{i}T_{cp} + (z_{i} + kz_{i})T_{cm}}, i = 2, 3, \dots m$$

$$(2.14)$$

Equation (2.14) can be represented as

$$\alpha_i = q_i \alpha_{i-1} = (\prod_{l=2}^i q_l) \alpha_1$$

$$i = 2, 3, \dots m$$

(2.15)

From equations (2.9), (2.11), the normalization equation (2.12) becomes

$$\frac{1}{\gamma_1}\alpha_1 + \alpha_1 + \alpha_2 + \dots + \alpha_m = \frac{1}{\gamma_1}\alpha_1 + \alpha_1 + \sum_{i=2}^m \alpha_i = 1$$

(2.16)

$$\left[\frac{1}{\gamma_1} + 1 + \sum_{i=2}^{m} \left(\prod_{l=2}^{i} q_l\right)\right] \alpha_1 = 1$$

(2.17)

$$\alpha_1 = \frac{1}{\left[\frac{1}{\gamma_1} + 1 + \sum_{i=2}^{m} (\prod_{l=2}^{i} q_l)\right]}$$

(2.18)

From the timing diagram, Fig. 2-4, we can obtain the finish time with m+1 processors,

$T_{f,m}$ , as follows:

$$T_{f,m} = \alpha_0 w_0 T_{cp} = \frac{1}{\gamma_1} \alpha_1 w_0 T_{cp}$$

(2.19)

While the finish time with only one processor,  $T_{f,0}$ , is

$$T_{f,0} = \alpha_0 w_0 T_{cp} = w_0 T_{cp} \tag{2.20}$$

The speed-up, which is the ratio of job finish time of one processor to that on m+1 processors, can be obtained as:

$$Speedup = \frac{T_{f,0}}{T_{f,m}} = \gamma_1 \times \frac{1}{\alpha_1} = 1 + \gamma_1 [1 + \sum_{i=2}^{m} (\prod_{l=2}^{i} q_l)]$$

(2.21)

Since  $\prod_{l=2}^{i} q_l$  can be simplified as  $\frac{[w_1T_{cp}+(z_1+kz_1)T_{cm}]}{w_iT_{cp}+(z_i+kz_i)T_{cm}}$ , the speed-up, Speedup in equation (2.21) and the finish time,  $T_{f,m}$  in equation (2.19) can be derived as follows:

$$T_{f,m} = \frac{1}{\gamma_1} \alpha_1 w_0 T_{cp} = \frac{w_0 T_{cp}}{1 + \gamma_1 \left( 1 + \sum_{i=2}^m \frac{[w_1 T_{cp} + (z_1 + kz_1) T_{cm}]}{w_i T_{cp} + (z_i + kz_i) T_{cm}} \right)}$$

(2.22)

$$Speedup = 1 + \gamma_1 \left[ 1 + \sum_{i=2}^{m} \frac{[w_1 T_{cp} + (z_1 + kz_1) T_{cm}]}{w_i T_{cp} + (z_i + kz_i) T_{cm}} \right]$$

(2.23)

For a special case, a homogeneous network, all of children processors have the same processing speed and all of the links have the same transmission speed, the finish time,  $T_{f,m}$  is

$$T_{f,m} = \frac{w_0 T_{cp}}{1 + \gamma_1 [1 + (m - 1)]} = \frac{w_0 T_{cp}}{1 + \gamma_1 \times m}$$

$$= \frac{w_0 T_{cp}}{1 + m \times \left[\frac{(1 + K)z T_{cm} + w T_{cp}}{w_0 T_{cp}}\right]}$$

$$= \frac{w_0 T_{cp}}{1 + m \times [(1 + K)\sigma^* + q^*]}$$

(2.24)

where  $\gamma_1$  is from (2.13),  $\sigma^* = \frac{zT_{cm}}{w_0T_{cp}}$ , and  $q^* = \frac{w}{w_0}$ . From (2.21), speed up for a homogeneous network (all children processing speed and all link speed are identical) is obtained as follows:

$$Speedup = \frac{T_{f,0}}{T_{f,m}} = 1 + \gamma_1 [1 + \sum_{i=2}^{m} 1]$$

$$= 1 + \gamma_1 \times m$$

(2.25)

Since the inverse computing speed, w and the inverse communication speed, z is identical among all processors and links in homogeneous network respectively, the value of  $q_i$  from (2.14) not only becomes one, but the value of  $\prod_{l=2}^{i} q_l$  is also one. It can be seen that the value of speedup is linearly related to the number of processors in a simultaneous distribution and collection method.

Figure 2-5: The finish time versus the number of processors for SD-NO, PI and PR load scheduling methods.

# 2.3 Performance Analysis And Comparison

#### 2.3.1 Speedup of the SD-NO method

In this section, for the SD-NO (Simultaneous Distribution with NO computation) scheduling method, we assume that the root processor is identical to each child processor in terms of computing speed. The root processor does not have load assigned to itself, but just distributes and collects load to/from children processors, We consider the same parameters as those of PI and PR in papers [1,11]. The inverse computing speed of the processor, w, is 1.0, and the inverse communication speed, z, is 0.2. Both  $T_{cp}$  and  $T_{cm}$  are 1.0. Three values of the ratio, k, are considered: 0.2, 1.0, and 1.8.

In Fig. 2-5 (a), our load scheduling mechanism, SD-NO shows a much better performance than PI and PR. When the number of processors is 12, which is the optimal number of the processors in PI, the SD-NO method shows more than 2 times

less processing time as PI and PR. Especially when we consider more processors added in the network, for example, 30, the difference is much larger, which is above 6 times for PI. This means our mechanism, SD-NO, is more scalable and cost effective in terms of the computing speed. When the number of processors increases from 12 to 30, the performance of the system increases almost 6 times, while the number of processors only increases 2.5 times.

In Fig. 2-5 (b), we see that for all three cases of the ratio, k, where k < 1, k = 1, k > 1, our mechanism shows a much better performance than that of PI. In terms of the optimal number of processors, SD-NO shows almost 2 times better performance than that of PI for three 'k' values. When we consider processor scalability, for a number of processors of 30, SD-NO achieves much better performance than that of PI. That is more than 10 times, 8 times, and 6 times improvement for each of k > 1, k = 1, k < 1.

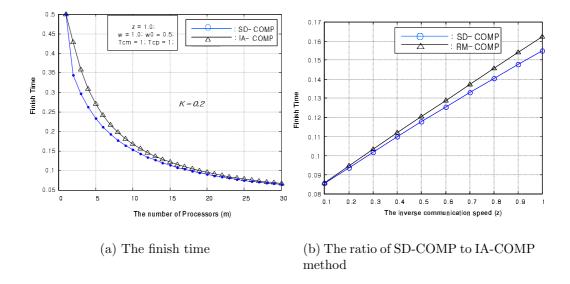

## 2.3.2 Speedup of the SD-COMP method

In this section, for the SD-COMP (Simultaneous Distribution with Computation) scheduling method, we assume that the root processor is different from the children in terms of computing speed and has load to compute itself. So the root processor not only distributes and collects load to/from children processors, but also computes load. The ratio of load received to load sent, k, is chosen as 0.2, since we suppose the case k is less than 1, as is usually the case for compressed results.

In Fig. 2-6 (a), we assume that the computing speed of the root processor for

- (a) The root processor is twice as fast as a child processor

- (b) The root processor is twice, 5 times, and 10 times as fast as a child processor.

Figure 2-6: The finish time versus the number of processors for SD-COMP, SD-NO, PI, and PR load scheduling methods on a homogeneous network.

SD-COMP is twice as much as that of each child processor. That is the inverse computing speed of the root processor,  $w_0$ , is half of that of each child, 'w'. We see that SD-COMP method is continuously faster for SD-NO method, and much faster, for example more than 6 times, for PI and PR method up to the number of processors, 30. In terms of processor scalability, SD-COMP has a more improved result. When the number of processors increases from 12 to 30, the performance of SD-COMP goes up 2.24 times to 6 times as fast as respectively that of PI. However, SD-COMP and SD-NO method shows similar performance and good scalability.

From Fig. 2-6 (b), we consider three cases of computing speed of the root processor for SD-COMP. Those are twice, 5 times, and 10 times as fast as that of each child processor. When the number of processors is small, for example 2 to 5, the performance of the SD-COMP method is much better than the SD-NO, PI, and PR

methods, because the root processor of the SD-COMP method participates in computation itself, involving around 20% to half of the whole load. While the number of processors increases to 12, all of the SD methods show 2.4 times, 3 times, 4 times, 5 times improvement in the processing time irrespective of load assigned to the root processor. As the number of processors increases up to 30, all of the SD methods show still better performance than the PI and PR methods, because all of the SD methods have good scalability in the number of processors. However when the number of processors is 30, the performance improvement of the SD-COMP is small, just 1.3 times, against the SD-NO method as compared to 6 to 8 times against PI and PR. One point to note is that when the number of processors is small, it is the method to distribute load as well as the root processor speed that is important to total processing time. The other point is that when the number of processors increases enough, the most critical part is the method to distribute and collect load simultaneously or sequentially rather than whether load is assigned to the root processor.

This work is meaningful for showing not only a more efficient scheduling method for parallel video encoding, but also good scalability in the number of processors.

### 2.4 Conclusion

This work leads to the following conclusions:

- This work is meaningful for showing not only a more efficient scheduling method for parallel video encoding but also good scalability in the number of processors.

- This work is novel in proposing a method of modeling interference aware com-

putation that leads to more realistic results.

- The extensive discussion here relating various interconnection topologies to this work should be of interest to other researchers.

- We find that the choice of scheduling policy has a greater impact on performance than whether or not the root node does computation for the network considered in this work.

- Finally many factors influence performance results obtained through mathematical (divisible) modeling including scheduling policy, interconnection topology, memory hierarchy, fixed communication delays, and the potential use of front-end processors. Most papers, like this one, consider a small number of these factors for reasons of space, tractability and novelty but the most accurate modeling would take most if not all of these factors into account.

All in all divisible load modeling as it has been developed for parallel video processing by researchers including ourselves, has been shown to be a useful and cost effective tool for system performance prediction.

# Chapter 3

# Interference Aware Scheduling

In a situation in networks and grids that both communication and computation on each processor are executed simultaneously, the computing speed experiences degradation due to the impact of communication on the same processor. Here we propose a scheduling method considering communication interference, so called , interference aware (IA) scheduling, and develop analytically an optimal scheduling policy in the presence of interference of communication on computation for the sequential distribution. This particular load distribution policy is chosen for illustrative purposescertainly other scheduling policies could be modeled in an interference aware context.

When load is distributed to children processors, the computing speeds of the root and children processors are degraded by communication (sending and receiving load). Only during certain phases of load distribution and processing is communication active. It is only during these times that computation is affected by communication. We define the affected inverse computing speed,  $w'_i$ , and the unaffected inverse computing speed,  $w'_i$  separately. The load fraction for each processor,  $\alpha_i$ , is also divided

into two portions,  $\alpha'_i$  for the affected load and  $\alpha''_i$  for the unaffected load. From the relationship among the processors in our model, we find 3m + 3 unknown variables and 3m + 3 equations where m + 1 is the number of processors. We can reduce the number of equations from 3m + 3 to m + 1 by using the equivalent processor concept and techniques, which means that both the affected and unaffected processing capability of each processor can be merged into a single processor which has equivalent processing capability.

## 3.1 Sequential Distribution Model and definition

In this paper sequential distribution and simultaneous start scheduling is investigated under the interference of communication on computation in a heterogeneous single level tree (star) topology.

### 3.1.1 Sequential distribution model for a heterogeneous tree

When the impact of communication in sending or receiving load is considered, the traditional sequential distribution model is slightly changed as in Fig. 3-1. The computing speed of each processor is decreased only when communication and computation overlap. This means that the original inverse computing speed,  $w_i$ , is changed into  $w'_i$  in case computation overlaps sending or receiving load. The load fraction to each processor,  $\alpha_i$ , is divided into  $\alpha'_i$  for the affected computation and  $\alpha''_i$  for unaffected computation.

Figure 3-1: Interference aware sequential load distribution in a tree topology.

#### 3.1.2 Notation

$\alpha_i$ : The load fraction assigned to the *i*th processor (where  $i=0,1,2,\ldots,m$ ).

$\alpha_i'$ : The load fraction assigned to the *i*th processor with communication (where  $i=0,1,2,\ldots,m$ ).

$\alpha_i''$ : The load fraction assigned to the *i*th processor without communication (where  $i=0,1,2,\ldots,m$ ).

$w_i$ : The inverse computing speed at the *i*th processor (where  $i=0,1,2,\ldots,m$ ).

$w_i'$ : The inverse computing speed at the *i*th processor when sending or receiving load (where i = 0, 1, 2, ..., m).

$w_i''$ : The inverse computing speed at the *i*th processor which is not affected by the communication (where  $i=0,1,2,\ldots,m$ ).

$w_i^{eq}$ : The equivalent inverse computing speed at the equivalent node,  $node_{\langle i \rangle}^{eq}$ , collapsed from a single level tree rooted at  $node_{\langle i \rangle}$  (where  $i=0,1,2,\ldots,m$ ).

$z_i$ : The inverse communication speed on the *i*th link (where  $i = 0, 1, 2, \ldots, m$ ).

$T_{cp}$ : Computing intensity constant.

$T_{cm}$ : Communication intensity constant.

$T_{f,m}$ : The finish time (makespan). Time at which the root processor and m children processors complete computation.

$T_{f,0}$ : The finish time. Time at which computation ends for a single root processor.

# 3.2 Interference aware scheduling (IA)

#### 3.2.1 Timing Diagram for Sequential Distribution

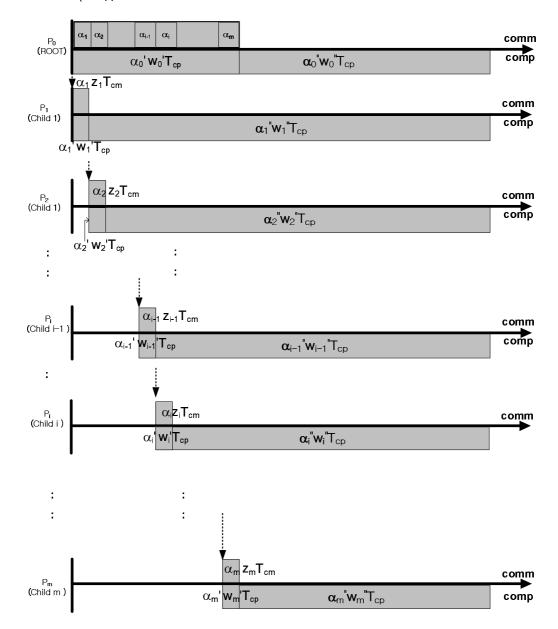

The mechanism of interference aware scheduling via sequential load distribution and simultaneous start is presented in Fig. 3-2. From this timing diagram, we obtain the relationships among the processors. The following equations is used for this sequentially distributed interference aware model. Since there are 3m+3 unknown variables and 3m+3 equations, we can deduce the corresponding closed-form solution. From the seven basic equations we can define all of the relationships between processors.

First, the normalization equation consists of the sum of all load fractions assigned

Communication Interference Aware Scheduling

- Sequential Distribution/Simultaneous Start

- (m+1) processors

Figure 3-2: Timing diagram for IA (Interference Aware) sequential distribution and simultaneous start.

to the root processor and each child processor.

$$\sum_{i=0}^{m} \alpha_i = 1 \tag{3.1}$$

Each load fraction,  $\alpha_i$ , for each processor is fragmented into two load fractions: one is  $\alpha'_i$  for the affected processor and the other  $\alpha''_i$  for the unaffected processor.

$$\alpha_i = \alpha_i' + \alpha_i'' \qquad i = 0, 1, \dots, m \tag{3.2}$$

The following equation comes from the relationship between the root processor and the first child processor. The time to compute one fragmented load  $\alpha'_0$  in the affected part, using  $w'_0$ , and load fragment  $\alpha''_0$  in the unaffected part, using  $w''_0$ , of the root processor should be equal to the time to distribute the load  $\alpha_1$  to the child processor 1 and compute one of the fragmented loads,  $\alpha''_1$ , in the unaffected part, using  $w''_1$  of the child processor 1.

$$\alpha_0' w_0' T_{cp} + \alpha_0'' w_0'' T_{cp} = \alpha_1 z_1 T_{cm} + \alpha_1'' w_1'' T_{cp}$$

(3.3)

The time to compute one of the fragmented loads,  $\alpha_0''$  in the unaffected part, using  $w_0''$  of the root processor should be equal to the time to compute one of fragmented loads,  $\alpha_m''$  in the unaffected part, using  $w_m''$  of the last child processor.

$$\alpha_0'' w_0'' T_{cp} = \alpha_m'' w_m'' T_{cp} \tag{3.4}$$

The time to compute one of the fragmented loads,  $\alpha'_0$  in the affected part, using  $w'_0$  of the root processor should be equal to the time to distribute the whole load to all children processors except the load,  $\alpha_0$ , for the root processor.

$$\alpha_0' w_0' T_{cp} = \left(\sum_{i=1}^m \alpha_i z_i\right) T_{cm} \tag{3.5}$$

The time to distribute the i-th load,  $\alpha_i$  over the i-th link to the i-th processor is equal to the time to compute one of the fragmented loads,  $\alpha'_i$  in the affected part of the i-th processor.

$$\alpha_i z_i T_{cm} = \alpha_i' w_i' T_{cp} \qquad i = 1, 2, \dots, m$$

(3.6)

Equation (3.7) says that the time to compute one of the fragmented loads,  $\alpha''_{i-1}$  in the unaffected part of the i-1-th processor is equal to the time to distribute the i-th load,  $\alpha_i$ , to the i-th processor and compute one of the fragmented loads,  $\alpha''_i$  in the unaffected part of the i-th processor.

$$\alpha_{i-1}^{"}w_{i-1}^{"}T_{cp} = \alpha_i z_i T_{cm} + \alpha_i^{"}w_i^{"}T_{cp} \qquad i = 2, 3, \dots, m$$

(3.7)

## 3.2.2 Analytical solution

From equations (3.2) and (3.6), one obtains

$$\alpha_{i}^{"} = \alpha_{i} - \alpha_{i}^{'} \qquad i = 0, 1, \dots, m \tag{3.8}$$

$$\alpha_{i}' = \left(\frac{z_{i}T_{cm}}{w_{i}'T_{cp}}\right)\alpha_{i}$$

$$= k_{i}\alpha_{i}, \qquad k_{i} = \frac{z_{i}T_{cm}}{w_{i}'T_{cp}} \qquad i = 1, 2, \dots, m$$

(3.9)

Substitute equation (3.9) into (3.8)

$$\alpha_i'' = \alpha_i - k_i \alpha_i = (1 - k_i) \alpha_i, \qquad i = 1, 2, \dots, m$$

(3.10)

From (3.4) and (3.10)

$$\alpha_0'' = \frac{w_m''}{w_0''} \alpha_m'' = \frac{w_m''}{w_0''} (1 - k_m) \alpha_m, \qquad k_m = \frac{z_m T_{cm}}{w_m' T_{cp}}$$

(3.11)

From equation (3.5)

$$\alpha_0' = \frac{T_{cm}}{w_0' T_{cp}} \left( \sum_{i=1}^m \alpha_i z_i \right) \tag{3.12}$$

Substitute equations (3.11) and (3.12) into equation (3.2)

$$\alpha_{0} = \frac{T_{cm}}{w'_{0}T_{cp}} \left( \sum_{i=1}^{m} \alpha_{i}z_{i} \right) + \frac{w''_{m}}{w''_{0}} (1 - k_{m})\alpha_{m}$$

$$= c_{0} \left( \sum_{i=1}^{m} \alpha_{i}z_{i} \right) + r_{0}(1 - k_{m})\alpha_{m}, \quad c_{0} = \frac{T_{cm}}{w'_{0}T_{cp}}, \quad r_{0} = \frac{w''_{m}}{w''_{0}}$$

(3.13)

In equation (3.7) we replace  $\alpha_i''$  with  $\alpha_i$  by using equations (3.10) and (3.11)

$$(1 - k_{i-1})\alpha_{i-1}w_{i-1}^{"}T_{cp} = \alpha_i z_i T_{cm} + (1 - k_i)\alpha_i w_i^{"}T_{cp}$$

$$= [z_i T_{cm} + (1 - k_i)w_i^{"}T_{cp}]\alpha_i \qquad i = 2, 3, \dots, m$$

(3.14)

We can simplify equation (3.14) in terms of  $\alpha_i$

$$\alpha_{i} = \frac{(1 - k_{i-1})w_{i-1}^{"}T_{cp}}{[z_{i}T_{cm} + (1 - k_{i})w_{i}^{"}T_{cp}]}\alpha_{i-1}$$

$$= q_{i}\alpha_{i-1}, \qquad i = 2, 3, \dots, m$$

$$= \left(\prod_{l=2}^{i} q_{l}\right)\alpha_{1}$$

$$q_{i} = \frac{(1 - k_{i-1})w_{i-1}^{"}T_{cp}}{z_{i}T_{cm} + (1 - k_{i})w_{i}^{"}T_{cp}}$$

(3.15)

From equations (3.13) and (3.15) we can obtain  $\alpha_0$  with respect to  $\alpha_1$

$$\alpha_{0} = c_{0} \left( \sum_{i=1}^{m} \alpha_{i} z_{i} \right) + r_{0} (1 - k_{m}) \alpha_{m}$$

$$= c_{0} \left( \alpha_{1} z_{1} + \alpha_{1} q_{2} z_{2} + \alpha_{1} q_{3} q_{2} z_{3} \dots + \alpha_{1} \prod_{l=2}^{m} q_{l} z_{m} \right) + r_{0} (1 - k_{m}) \alpha_{1} \prod_{l=2}^{m} q_{l}$$

$$= \left[ c_{0} \left( z_{1} + \sum_{i=2}^{m} (\prod_{l=2}^{i} q_{l}) z_{i} \right) + r_{0} (1 - k_{m}) \prod_{l=2}^{m} q_{l} \right] \alpha_{1}$$

$$= p_{0} \alpha_{1}$$

$$p_{0} = c_{0} \left( z_{1} + \sum_{i=2}^{m} (\prod_{l=2}^{i} q_{l}) z_{i} \right) + r_{0} (1 - k_{m}) \prod_{l=2}^{m} q_{l}$$

$$(3.16)$$

Above in equation (3.16), we assume all of links speed are identical each other,

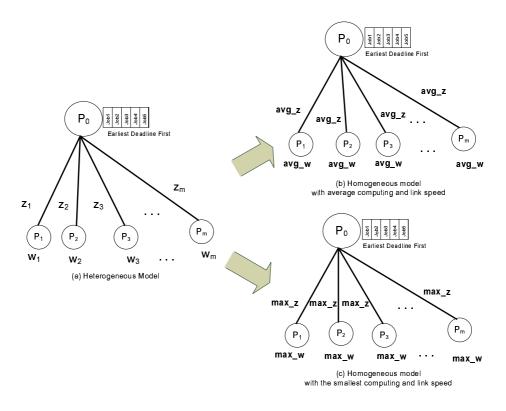

Figure 3-3: The equivalent processor concept for IA (interference aware) scheduling. which means  $z_i = z$ , (i = 1, 2, ..., m). Then  $p_0$  becomes  $p_0 = c_0 \left(1 + \sum_{i=2}^m (\prod_{l=2}^i q_l)\right) z + r_0(1 - k_m) \prod_{l=2}^m q_l$ . The normalization equation also leads to

$$p_0 \alpha_1 + \alpha_1 + \left(\sum_{i=2}^m \prod_{l=2}^i q_l\right) \alpha_1 = 1$$

$$\alpha_1 = \frac{1}{p_0 + 1 + \left(\sum_{i=2}^m \prod_{l=2}^i q_l\right)}$$

(3.17)

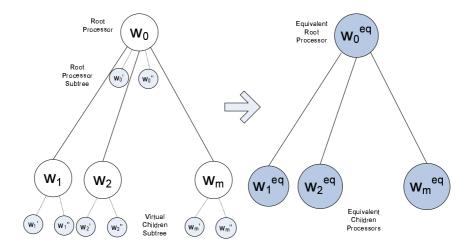

#### • Equivalent processor in a heterogenous tree topology

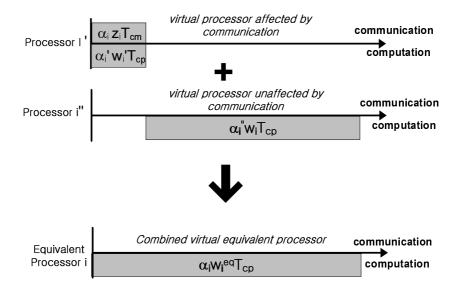

The virtual nodes of each processor are merged into one node which is identical to the combined value of two virtual nodes of each processor with respect to processing capability, as illustrated in Fig. 3-3. From the perspective of processing time, the sum of the affected and unaffected processing capability of each processor is equal to that of each equivalent processor, as the timing diagram in Fig. 3-4 indicates. This means that each virtual processor tree is replaced with the single equivalent processor,  $w_i^{eq}$  so that we can refine the closed-form solution and calculate the speedup for the whole complex network. Here  $w_i'$ , inverse computing speed, is affected by the interference

Figure 3-4: Timing diagram of the equivalent processor for Interference Aware sequential distribution and simultaneous start scheduling.

of communication,  $\boldsymbol{w}_{i}^{''}$  is not affected for the ith processor.

From the timing diagram we can obtain

$$\alpha_{i} w_{i}^{eq} T_{cp} = \alpha_{i}' w_{i}' T_{cp} + \alpha_{i}'' w_{i}'' T_{cp}$$

(3.18)

Substitute equation (3.9) and (3.10) into the above equation (3.18), so that

$$\alpha_{i}w_{i}^{eq} = k_{i}\alpha_{i}w_{i}' + (1 - k_{i})\alpha_{i}w_{i}'',$$

$$w_{i}^{eq} = k_{i}w_{i}' + (1 - k_{i})w_{i}'', \qquad i = 1, 2, \dots, m$$

(3.19)

Finally, we can obtain the closed-form solution for the finish time from the perspective of the equivalent processor by substituting  $\alpha_1$ .

Finish time is

$$T_{f,m} = \alpha_1 w_1^{eq} T_{cp}$$

$$= \alpha_1 [k_1 w_1' + (1 - k_1) w_1''] T_{cp}$$

$$= \frac{[k_1 w_1' + (1 - k_1) w_1'']}{\left[p_0 + 1 + \left(\sum_{i=2}^m \prod_{l=2}^i q_l\right)\right]} T_{cp}$$

(3.20)

The speed-up is

$$Speedup = \frac{T_{f,0}}{T_{f,m}} = \frac{w_0 T_{cp}}{\alpha_1 w_1^{eq} T_{cp}} = \frac{w_0}{w_1^{eq}} \cdot \frac{1}{\alpha_1}$$

$$= \frac{w_0}{w_1^{eq}} \cdot \left[ p_0 + 1 + \left( \sum_{i=2}^m \prod_{l=2}^i q_l \right) \right]$$

(3.21)

Equation (3.21) can be represented in the homogeneous network by the ratio of the communication delay to the computation time of a unit load, that is the parameter  $\sigma = \frac{zT_{cm}}{wT_{cp}}.$

$$\sigma' = \frac{zT_{cm}}{w'T_{cp}}, \quad \sigma'' = \frac{zT_{cm}}{w''T_{cp}}$$

(3.22)

Then  $k_i = \frac{z_i T_{cm}}{w_i' T_{cp}} = \frac{z T_{cm}}{w'' T_{cp}}$  of equation (3.9) becomes  $\sigma'$  and  $r_0 = \frac{w_m''}{w_0''} = \frac{w''}{w''}$  of equation (3.13) is one, because of the homogeneous network.

So an equation for q from  $q_i$  in equation (3.15) is obtained

$$\frac{1}{q_i} = \frac{z_i T_{cm} + (1 - k_i) w_i'' T_{cp}}{(1 - k_{i-1}) w_{i-1}'' T_{cp}} = \frac{z T_{cm} + (1 - k) w'' T_{cp}}{(1 - k) w'' T_{cp}}$$

$$= 1 + \frac{1}{(1 - k)} \frac{z T_{cm}}{w'' T_{cp}} = 1 + \frac{\sigma''}{1 - \sigma'} = \frac{1 - \sigma' + \sigma''}{1 - \sigma'} = \frac{1}{q}$$

$$q = \frac{1 - \sigma'}{1 - \sigma' + \sigma''} \tag{3.23}$$

Equation  $p_0$  of equation (3.16) is

$$p_{0} = \frac{zT_{cm}}{w'T_{cp}} \left( 1 + \sum_{i=2}^{m} (\prod_{l=2}^{i} q_{l}) \right) + 1 \cdot (1 - k_{m}) \prod_{l=2}^{m} q_{l}$$

$$= \sigma' \left( \frac{1 - q^{m}}{1 - q} \right) + (1 - \sigma') q^{m-1}$$

(3.24)

The speedup in terms of  $\sigma^{'}$  and  $\sigma^{''}$  is

$$Speedup = \frac{w_0}{w_1^{eq}} \cdot \left[ \sigma' \left( \frac{1 - q^m}{1 - q} \right) + (1 - \sigma') q^{m-1} + \frac{1 - q^m}{1 - q} \right]$$

$$= \frac{w_0}{w_1^{eq}} \cdot \left[ (\sigma' + 1) \left( \frac{1 - q^m}{1 - q} \right) + (1 - \sigma') q^{m-1} \right]$$

(3.25)

## 3.3 Numerical Solution and comparison

#### 3.3.1 Numerical Solution Parameters

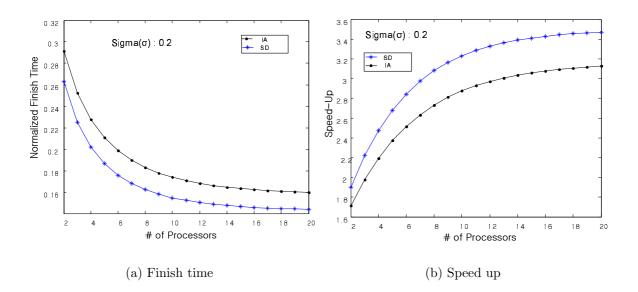

In this section, we assume a homogenous network in which each child processor has the same computing and link speed, and the root processor can have a different speed in order to focus on modeling the interference of communication. The parameters for this experiment, chosen for illustrative purposes, are as follows. In all experiments, the constants for the computation intensity,  $T_{cp}$  and communication intensity,  $T_{cm}$  is set to one. The inverse value of the root processing speed,  $w_0$  is set to one, but the inverse values of the children processors' speeds,  $w_i$  are set to two, which means each child processor has half as much computing speed as the root processor. The degradations of computing speed for sending and receiving load are modeled as two third and half as much as the initial value respectively. The inverse communication speed, z in the network is set to 0.5 in measuring the finish time and speed-up (Fig 3-5) and is varied from 0.1 to 1.0 in investigating the effect of communication speed on computation (Fig 3-6).

#### 3.3.2 Numerical Solution Results

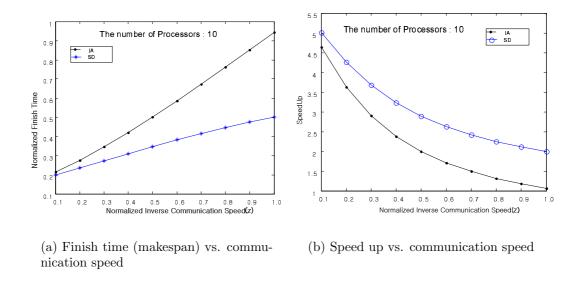

Finish Time: The plot for finish time (makespan) in Fig. 3-5 (a) shows that both IA (Interference Aware) and SD (Sequential Distribution) scheduling have a similar pattern from the point of view of the finish time as the number of processors increases from 2 to 20 in Fig. 3-5 (a). As the number of processors increases 2 to 20, the finish time of the IA method is around 90% of the SD method.

Figure 3-5: The IA (Interference Aware) scheduling versus the SD (Sequential Distribution) Scheduling.