# **Stony Brook University**

# OFFICIAL COPY

The official electronic file of this thesis or dissertation is maintained by the University Libraries on behalf of The Graduate School at Stony Brook University.

© All Rights Reserved by Author.

### HBD HV Control and Monitoring System for the PHENIX Experiment at the Relativistic Heavy Ion Collider

A Thesis Presented

by

### Manuel Proissl

$\operatorname{to}$

The Graduate School

in Partial Fulfillment of the Requirements

for the Degree of

### Master of Science

in

Physics (Scientific Instrumentation)

Stony Brook University

December 2009

#### Stony Brook University

The Graduate School

### Manuel Proissl

We, the thesis committee for the above candidate for the Master of Science degree, hereby recommend acceptance of this thesis.

Axel Drees – Thesis Advisor Professor, Department of Physics and Astronomy

Robert McCarthy Professor, Department of Physics and Astronomy

Michael Marx Professor, Department of Physics and Astronomy

Erle Graf Professor, Department of Physics and Astronomy

### Craig Woody Senior Scientist Brookhaven National Laboratory

This thesis is accepted by the Graduate School.

Lawrence Martin Dean of the Graduate School Abstract of the Thesis

### HBD HV Control and Monitoring System for the PHENIX Experiment at the Relativistic Heavy Ion Collider

by

### Manuel Proissl

### Master of Science

in

### Physics (Scientific Instrumentation)

#### Stony Brook University

2009

As an upgrade solution for measurements of the low-mass dielectron continuum in  $\sqrt{s_{NN}} = 200$  GeV Au+Au collisions at the Relativistic Heavy Ion Collider (RHIC) at Brookhaven National Laboratory, a Hadron Blind Detector (HBD) has been installed in a field free region surrounding the collision vertex in PHENIX. The first operation of the detector in 2007 has shown critical performance deficits due to issues found with the Gas Electron Multiplier (GEM) HV powering scheme, which allowed severe discharges to occur within the GEM stack, most notably between the mesh and uppermost GEM that damaged a considerable fraction of the GEM foils. In response, the damaged GEM foils were replaced and the problem was carefully studied. Based upon these results, a new High Voltage Control and Monitoring System (HVC) was developed to specifically address possible sources of damage, while allowing optimal control over the detector for maximal performance. The overall system comprises several novel hardware components including a new voltage divider board and trip detection/protection boards for each power supply module, while actual control of the HV is maintained by an intelligent software suite which incorporates Modern Optimal Control Theory. The software suite is made up of several concurrently operating subsystems, which process measurements fed back from the HV mainframe and modify the HV when deemed necessary. This software suite represents the first system based on true C/S architecture within the PHENIX HV Control environment and may be extended to other detector technologies requiring precision and stability.

The HVC system has been installed in PHENIX early 2009 and has proven its ability to regulate the HV of the HBD in an optimal way throughout the commissioning p+p Run-9 and is expected to lead the detector through its final and most important operation in the Au+Au Run-10 with the aim of enabling the HBD to acquire a substantial data set of the low-mass dileption spectrum. This data will present an opportunity to obtain significant insights into the characteristics of the Quark Gluon Plasma and to study chiral symmetry restoration and deconfinement. To my parents.

## Contents

|   | List          | of Fig  | gures                              | $\mathbf{i}\mathbf{x}$ |

|---|---------------|---------|------------------------------------|------------------------|

|   | List          | of Ta   | bles                               | xiv                    |

|   | Ack           | nowlee  | dgements                           | $\mathbf{x}\mathbf{v}$ |

| 1 | Intr          | roducti | ion                                | 1                      |

|   | 1.1           | Quark   | Gluon Plasma and RHIC              | 1                      |

|   | 1.2           | The P   | HENIX Experiment                   | 3                      |

|   |               | 1.2.1   | Global and Central Arm Detectors   | 6                      |

|   |               | 1.2.2   | Low-Mass Dileptons and $S/B$       | 9                      |

| 2 | The           | e HBD   | Detector                           | 10                     |

|   | 2.1           | Detect  | tor Concept                        | 10                     |

|   |               | 2.1.1   | Design and Implementation          | 11                     |

|   |               | 2.1.2   | Photocathode and Gas               | 13                     |

|   |               | 2.1.3   | Gas Electron Multipliers           | 14                     |

|   |               | 2.1.4   | Electron Identification Principle  | 17                     |

|   |               | 2.1.5   | Correlation of P/T and Module Gain | 20                     |

|   | 2.2           | Comm    | nissioning in Run-7                | 23                     |

|   |               | 2.2.1   | Detector Operation                 | 23                     |

|   |               | 2.2.2   | Performance Issues                 | 25                     |

|   | 2.3           | Upgra   | de Strategy for Run-9              | 26                     |

|   |               | 2.3.1   | HV Upgrade Requirements            | 26                     |

|   |               | 2.3.2   | System Design Overview             | 27                     |

| 3 | $\mathbf{HV}$ | Contr   | ol and Monitoring                  | <b>28</b>              |

|   | 3.1           | The C   | Control Philosophy                 | 28                     |

|   |               | 3.1.1   | Global Response Time Constant      | 32                     |

|   |               | 3.1.2   | System Development Approach        | 34                     |

|   | 3.2           | Fast-R  | Response GEM Protection            | 36                     |

|   |     | 3.2.1 Advanced Resistor Chain                                                              |

|---|-----|--------------------------------------------------------------------------------------------|

|   |     | 3.2.2 LeCroy 1471N Power Supply                                                            |

|   |     | 3.2.3 Trip Detection for LeCroy Systems                                                    |

|   |     | 3.2.4 Relay HV Protection                                                                  |

|   | 3.3 | Software System Design                                                                     |

|   |     | 3.3.1 PHENIX Control Infrastructure                                                        |

|   |     | 3.3.2 Modern C/S Architecture                                                              |

|   |     | 3.3.3 Dynamic Negative Feedback                                                            |

|   |     | 3.3.4 PHENIX HV Client/Server                                                              |

|   |     | 3.3.5 HBD HV Client/Server                                                                 |

|   | 3.4 | Control Subsystems                                                                         |

|   |     | 3.4.1 Mainframe Backup Thread                                                              |

|   |     | 3.4.2 Global Detector Status Module                                                        |

|   |     | 3.4.3 ParaConfig Exchange Module                                                           |

|   |     | 3.4.4 Detector Power and Bias Master                                                       |

|   |     | 3.4.5 Module Control Master                                                                |

|   |     | 3.4.6 Ramp Control Algorithm                                                               |

|   |     | 3.4.7 GEM Module Surveillance                                                              |

|   |     | 3.4.8 P/T Monitor and Control Unit                                                         |

|   |     | 3.4.9 Local and Satellite Alert Communication                                              |

|   |     | 3.4.10 Slow-Response GEM Protection                                                        |

|   | 3.5 | Development and Testing                                                                    |

|   |     | 3.5.1 HBD Simulation Project                                                               |

|   |     | 3.5.2 LeCroy 1471N Calibration                                                             |

|   | 3.6 | Installation in PHENIX 119                                                                 |

|   |     | 3.6.1 IR On-Bridge Channel Testing                                                         |

|   |     | 3.6.2 Implementation to PHENIX Control                                                     |

| 4 | D   |                                                                                            |

| 4 |     | n-9 Commissioning 122                                                                      |

|   | 4.1 | Noise Reduction in Pad Readout       123         W Supervised Model In Processor       124 |

|   | 4.2 | dV Scans and Module Bias                                                                   |

|   | 4.3 | Resistor Modifications and Bertan Tests                                                    |

|   | 4.4 | HV Module Calibrations                                                                     |

| 5 | Res | ults and Discussion 134                                                                    |

|   | 5.1 | Online Performance and Stability 135                                                       |

|   | 5.2 | Module Trip – Magnetic Field Correlation                                                   |

|   | 5.3 | Gain Stability                                                                             |

|   |     | 5.3.1 HV and Module Gain Behavior over Runtime 136                                         |

|   |     | 5.3.2 Gain Fluctuations in Respect to P/T Variations 141                                   |

|   |     |                                                                                            |

| 6 | Summary and Outlook                                                              | 143 |

|---|----------------------------------------------------------------------------------|-----|

|   | Bibliography                                                                     | 145 |

| A | HVC Theory of Dynamic Control                                                    | 148 |

| в | P/T Control Tables of Run-9                                                      | 154 |

| С | Miscellaneous ImagesC.1HBD Simulation ProjectC.2HBD Operation with HVC in PHENIX |     |

# List of Figures

| 1.1 | The energy density/ $T^4$ as a function of $T/T_c$ in QCD [1]      | 1   |

|-----|--------------------------------------------------------------------|-----|

| 1.2 | Schematic phase diagram of nuclear matter for 2 massless quarks    |     |

|     | and 1 heavy quark [2]. $\ldots$                                    | 2   |

| 1.3 | Schematic of the PHENIX Detector configuration as of 2009.         |     |

|     | The cross section of the two central arms perpendicular to the     |     |

|     | beam pipe (top) and a view from the east with the beam axis        |     |

|     | along the horizontal direction.                                    | 4   |

| 1.4 | The basic components of the BBC. (a) 64 PMTs are mounted           |     |

|     | to one BBC unit; (b) each single photomultiplier tube (PMT)        |     |

|     | with a timing resolution of 50ps is of 25.4mm in diameter and      |     |

|     | has a 30mm thick Quartz radiator.                                  | 6   |

| 1.5 | Schematic top view of the interaction region (bottom); Projec-     |     |

|     | tion of proton/neutron deflection in ZDC plane [3]                 | 7   |

| 1.6 | Important PHENIX Central Arm detectors. (a) The cross sec-         |     |

|     | tion of the PHENIX Central and Muon Magnets are shown              |     |

|     | with their field lines in $(++)$ configuration; (b) A Drift Cham-  |     |

|     | ber Frame; (c) Illustration of the PHENIX Pad Chambers; (d)        |     |

|     | A cut-away view of the PHENIX RICH detector                        | 8   |

| 2.1 | Location of the HBD and inner/outer coils in PHENIX                | 11  |

| 2.2 | HBD Design Overview. In (a) an exploded view of one HBD            |     |

|     | arm with one side panel for clarity removed is shown with its      |     |

|     | installation around the beam pipe in (b)                           | 12  |

| 2.3 | Absolute CsI Quantum Efficiency measurement in vacuum and          |     |

|     | $CF_4$ (a; [4]), and a model of the $CF_4$ molecule in (b)         | 14  |

| 2.4 | A Microscopic view of a GEM is shown in (a) and electric field     |     |

|     | lines of increased density within holes is illustrated in (b) when |     |

|     | a voltage to the electrodes is applied.                            | 15  |

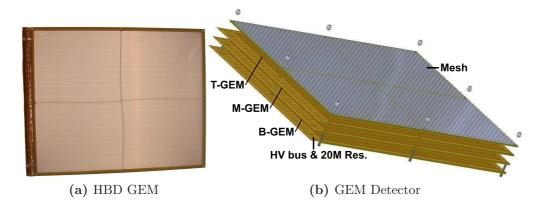

| 2.5 | A photograph of an HBD-sized GEM foil is shown in (a) and in       | 10  |

|     | (b) a Triple-GEM stack with Mesh is illustrated                    | 17  |

|     |                                                                    | - • |

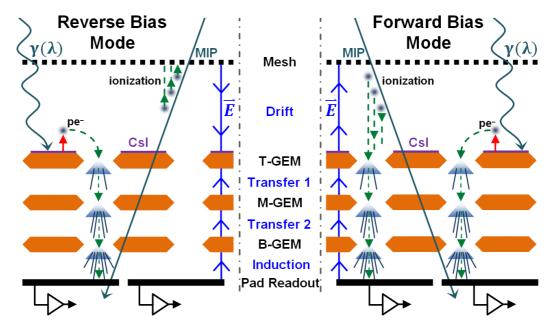

| 2.6        | The basic principle of Reverse and Forward Bias operation of                                                                                        |                 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|            | the HBD; the response to Cerenkov photons and MIPs to ei-                                                                                           |                 |

|            | ther mode is illustrated. The dashed arrows in red represent                                                                                        |                 |

|            | the photoelectron extraction from the CsI cathode, while ar-                                                                                        |                 |

|            | rows in green represent the transport of photoelectrons or/and                                                                                      |                 |

|            | ionization charge. The direction of the electric field lines within                                                                                 |                 |

|            | the gaps is displayed with blue arrows.                                                                                                             | 18              |

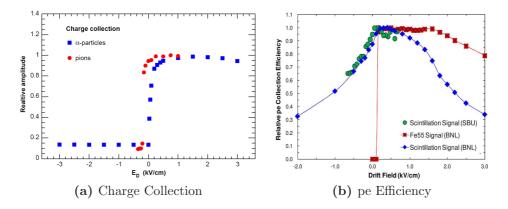

| 2.7        | Collection of ionization charge (a; [4]) and relative photoelec-                                                                                    |                 |

|            | tron collection efficiency (b; [5]) vs. the drift field.                                                                                            | 19              |

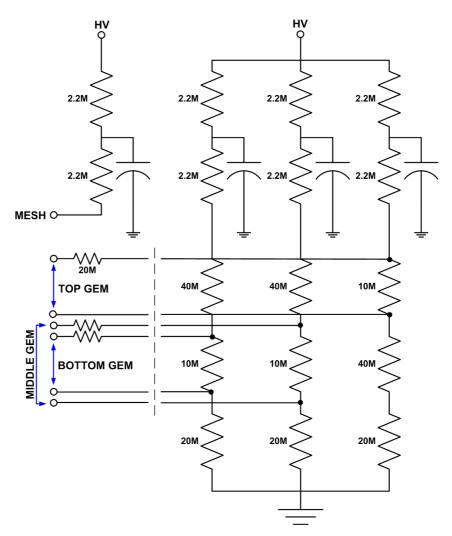

| 2.8        | Run-7 HBD Resistor Chain                                                                                                                            | 23              |

| 2.9        | Schematic of Run-7 HBD Resistor Chain                                                                                                               | 24              |

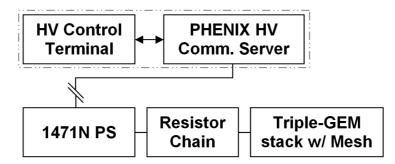

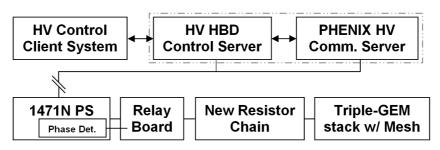

|            | Run-7 HV Control and powering scheme                                                                                                                | $\overline{25}$ |

|            | Damaged Top GEM foil from Run-7. The burned grid pattern                                                                                            | _0              |

|            | is clearly visible.                                                                                                                                 | 25              |

| 2 1 2      | Run-9 HV Control and powering scheme                                                                                                                | 27              |

| 2.12       | ital 5 if Control and powering science                                                                                                              | 21              |

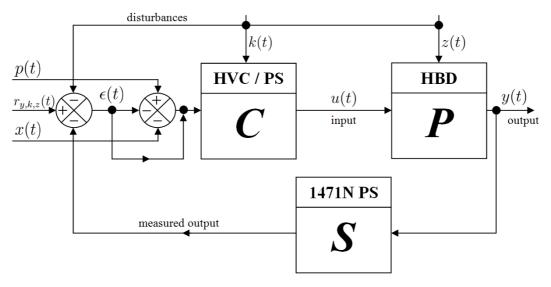

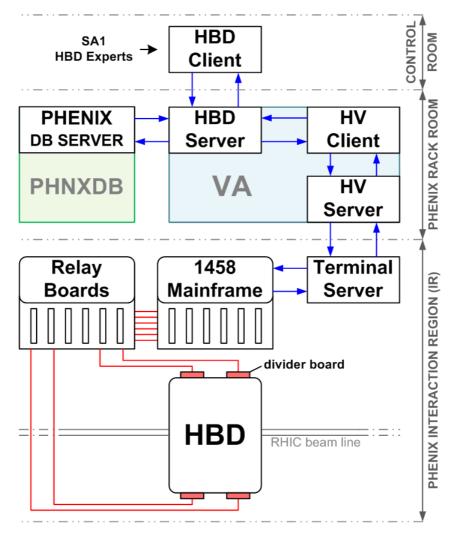

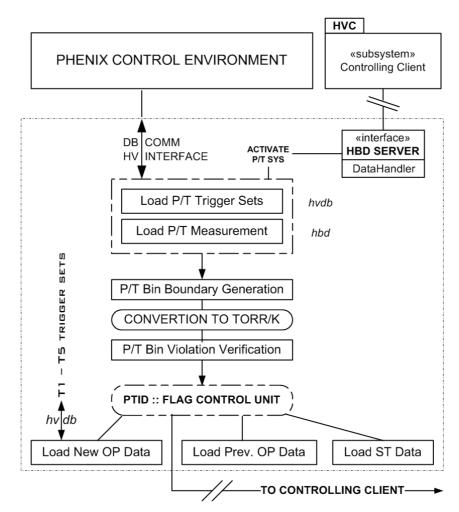

| 3.1        | HBD HVC Control Diagram.                                                                                                                            | 31              |

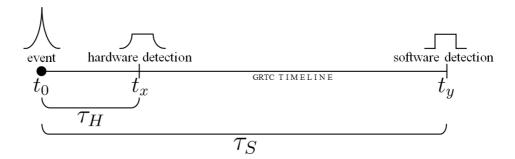

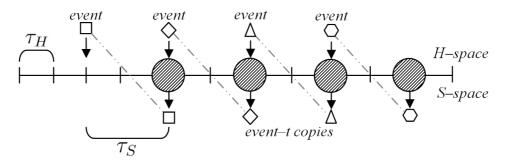

| 3.2        | Observer-based event detection principle in respect to hardware                                                                                     |                 |

|            | and software limitations.                                                                                                                           | 32              |

| 3.3        | HVC-governed event sampling and successive transport                                                                                                | 33              |

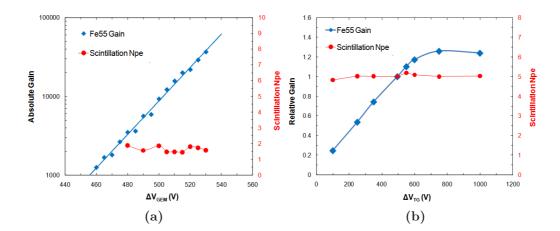

| 3.4        | GEM gain and scintillation signal as a function of the voltage<br>across the GEM is shown in (a), and in (b) the GEM voltage is                     |                 |

|            | kept constant while the voltage across the transfer gap is raised [5].                                                                              | 39              |

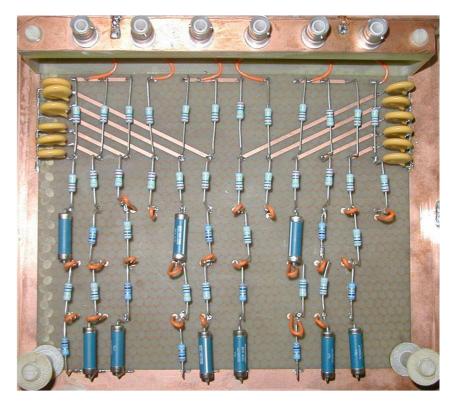

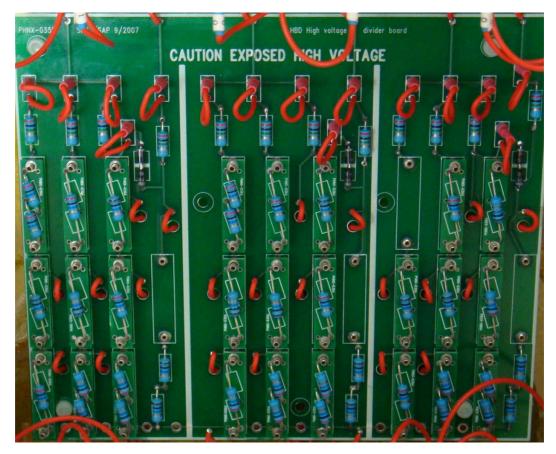

| 3.5        | PCB board with all resistors and zeners installed for Run-9.                                                                                        | 00              |

| 0.0        | One board hosts three resistor chains, each powering one GEM                                                                                        |                 |

|            | detector module.                                                                                                                                    | 40              |

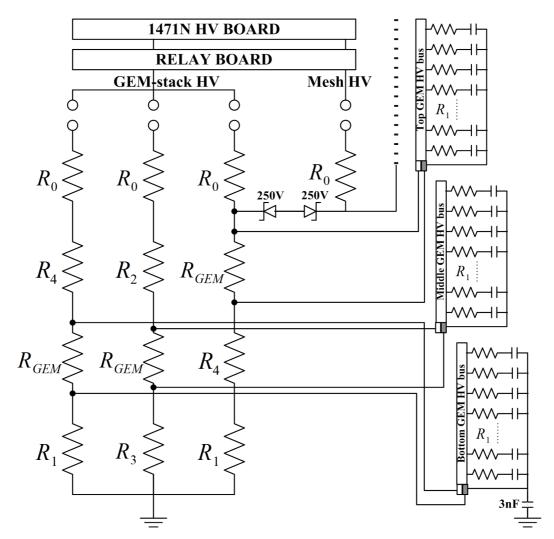

| 3.6        | Schematic of resistor chain for Run-9. The resistor values are                                                                                      | 10              |

| 0.0        | as follows: $R_0 = 2M\Omega$ , $R_1 = 20M\Omega$ , $R_2 = 26M\Omega$ , $R_3 = 46M\Omega$                                                            |                 |

|            | and $R_4 = 52M\Omega$ . A clear overview is shown in Tab. 3.1                                                                                       | 41              |

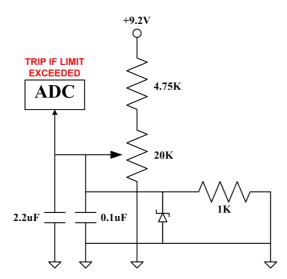

| 3.7        | Schematic of HV hardware limit. $\dots \dots \dots$ | 42              |

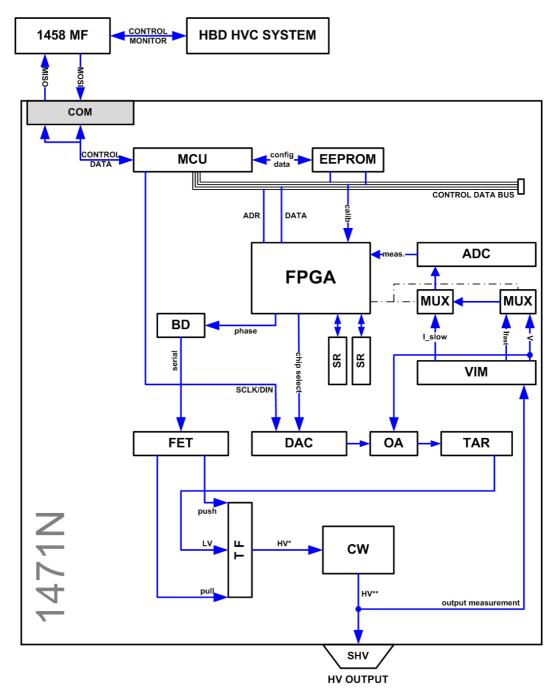

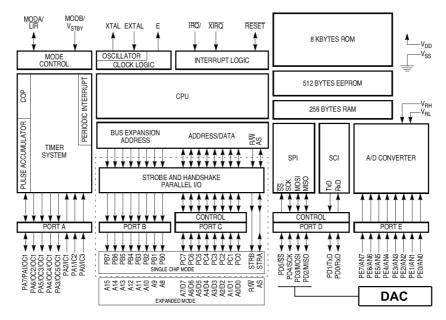

| 3.8        | Functional Diagram of the 1471N HV module.                                                                                                          | 44              |

| 3.0<br>3.9 | Ŭ                                                                                                                                                   | 44              |

|            |                                                                                                                                                     | 49              |

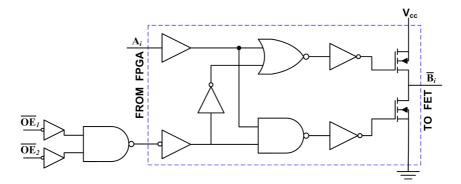

|            | Logic diagram of one of the eight Buffer/Line Drivers                                                                                               | 49              |

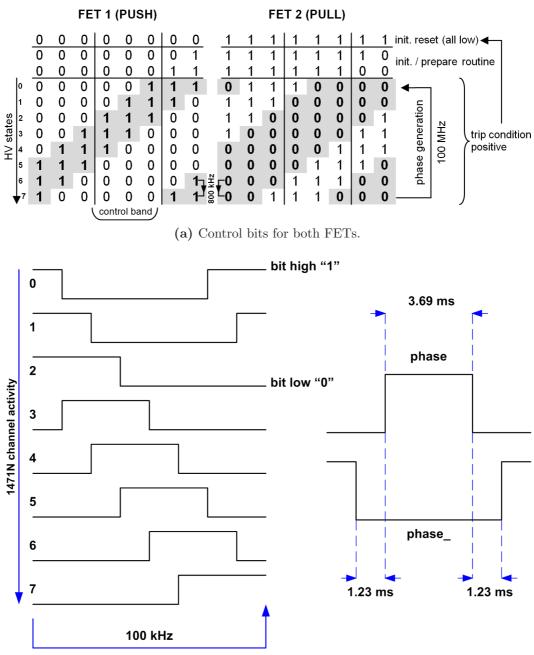

| 5.11       | Push-Pull Signals for HV Generation of the 1471N. (a) Control bits for FETs of <i>phase</i> and <i>phase_</i> , (b) Phases for one FET for          |                 |

|            | each of the 8 output channels (left) and the difference between                                                                                     |                 |

|            | $phase and phase_signals (right) $                                                                                                                  | 50              |

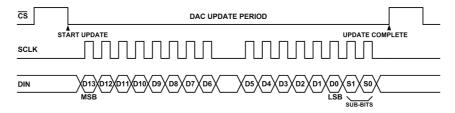

|            | DAC timing diagram; update execution in-between CS low bits.                                                                                        | 51              |

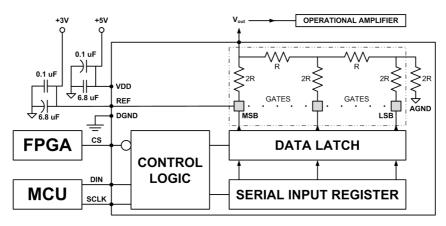

| 3.13       | DAC functional diagram with internal schematics                                                                                                     | 52              |

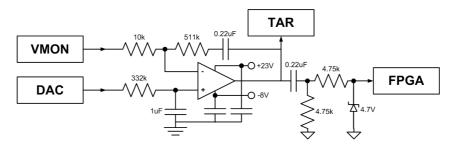

| 3.14 | Operational Amplifier with voltage monitor (from VIM) and                            |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | DAC inputs. The OP output represents the TAR input and is                            |     |

|      | checked against AC contamination riding on the pure LV DC                            |     |

|      | signal with the FPGA                                                                 | 53  |

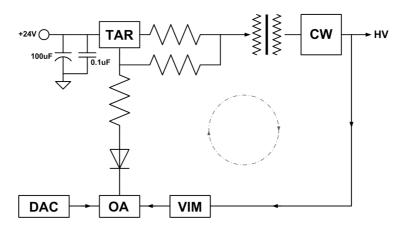

| 3.15 | Closed-loop Control Supply using an Adjustable Regulator (TAR)                       | 53  |

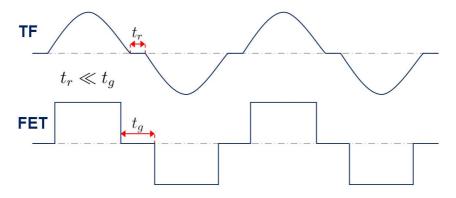

| 3.16 | Illustrative comparison of FET signal with final output by the                       |     |

|      | transformer                                                                          | 54  |

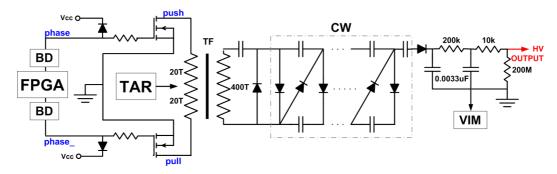

| 3.17 | Overview of HV Generation with the FPGA, TAR, TF and CW                              |     |

|      | as the main components                                                               | 55  |

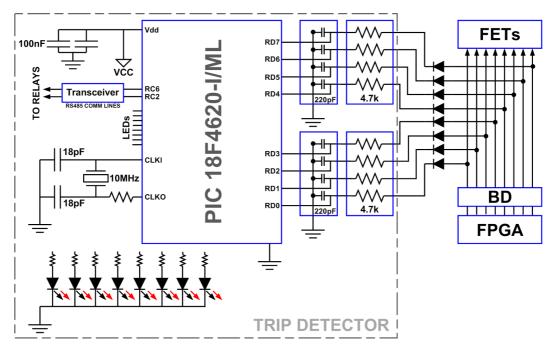

| 3.18 | Illustration of the Trip Detector Board implemented in the                           |     |

|      | 1471N. The phase for each channel is probed between the Buffer/Li                    | ne  |

|      | Driver (BD) and FET.                                                                 | 57  |

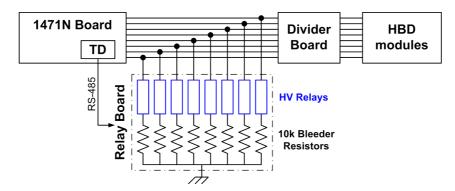

| 3.19 | Overview of Trip Detector and Relay Board implementation in                          |     |

|      | the HV System                                                                        | 58  |

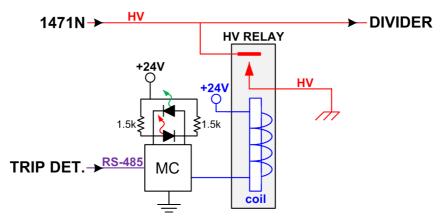

| 3.20 | HV Relay operation for one 1471N channel with an interior view                       |     |

|      | of the relay. A Dual Color LED indicates the status of the relay.                    | 59  |

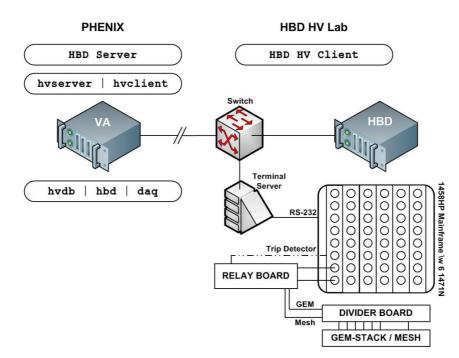

| 3.21 | Control Overview with the HVC Client/Server model                                    | 62  |

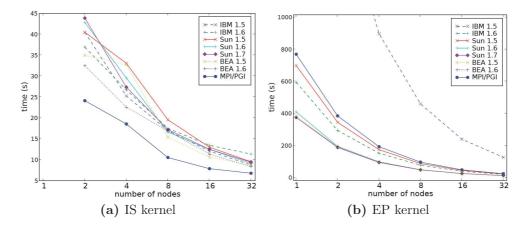

|      | Computational performance of Java vs. Fortran                                        | 64  |

|      | C/S communicational performance of Java vs. Fortran for CG                           |     |

|      | kernels                                                                              | 64  |

| 3.24 | Concept of communicating processes – a computational conver-                         |     |

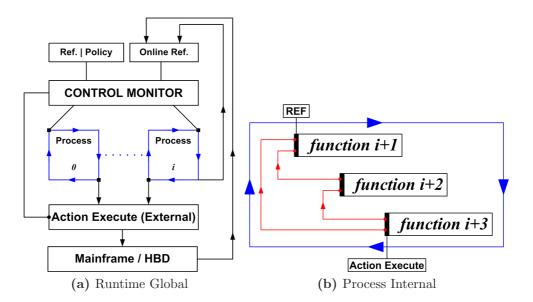

|      | sion of TDC                                                                          | 70  |

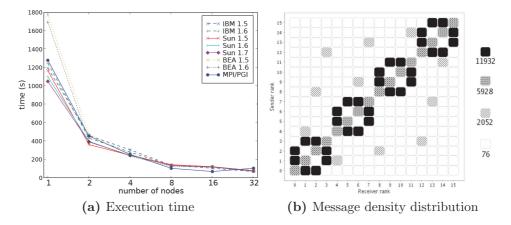

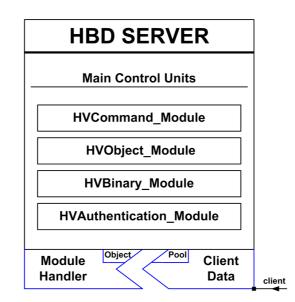

| 3.25 | HBD Server Design Structure                                                          | 72  |

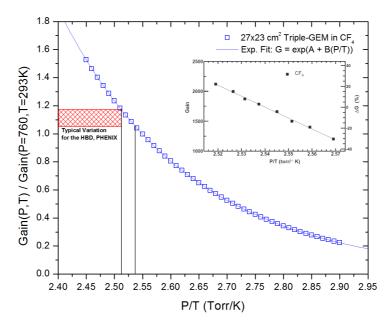

|      | Gain in respect to a standard pressure $P = 760$ Torr and tem-                       |     |

|      | perature $T=293K$ as a function of measured P/T. The shown                           |     |

|      | data is taken with a triple-stack $27 \times 23 \text{ cm}^2 \text{ GEM}$ and fitted |     |

|      | with an exponential.                                                                 | 94  |

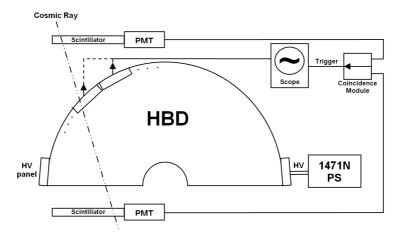

| 3.27 | Cosmic Ray measurement in laboratory to obtain a relative gain                       |     |

|      | for each module.                                                                     | 95  |

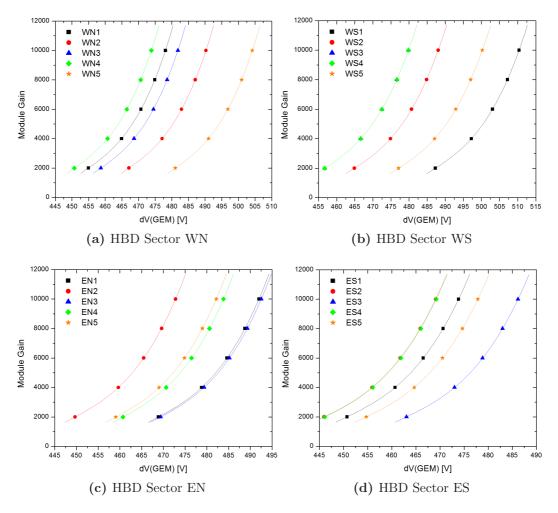

| 3.28 | Gain Calibration Curves for P/T Control & Monitor                                    | 97  |

|      | Simplified Illustration of HVC's P/T Control and Monitor Unit.                       | 98  |

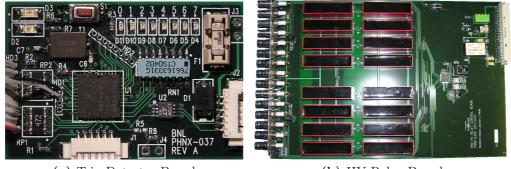

|      | Trip Protection boards, where (a) senses the disappearance of                        |     |

|      | phase on the 1471N, notifies (b), which then takes the cor-                          |     |

|      | responding GEM/Mesh pair channel with a $10k\Omega$ resistor to                      |     |

|      | ground. The boards are part of HVC's Fast-Response GEM                               |     |

|      | · · ·                                                                                | 110 |

| 3.31 |                                                                                      | 111 |

|      |                                                                                      | 112 |

|      |                                                                                      |     |

|      |                                                                                      | 114 |

| 3.34                                    | Measurement of a 1471N trip at 1500V with a Relay Board implemented. The discharge corresponds to the 10k bleeder         |            |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------|

| 0.05                                    | resistor to ground.                                                                                                       | 115        |

| 3.35                                    | Demand Voltage in comparison with actual Measured Voltage<br>over the runtime of the calibration routine                  | 117        |

| 3.36                                    | The Delta of Demand and Measured Voltage as a function of                                                                 | 110        |

| 3.37                                    | Demand Voltage                                                                                                            | 118<br>119 |

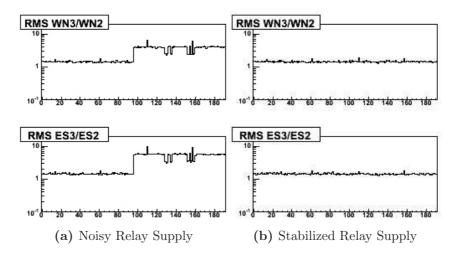

| 4.1                                     | HBD Pad Readout. In (a), a noisy power supply for the Relay                                                               |            |

|                                         | Board has been used and replaced in (b) with a stabilized supply.                                                         | 123        |

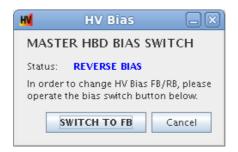

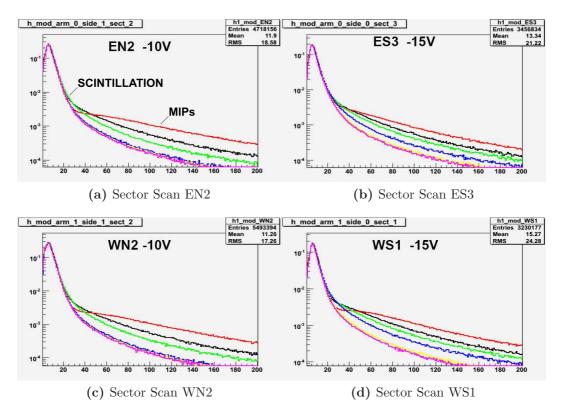

| 4.2                                     | 1                                                                                                                         | 124        |

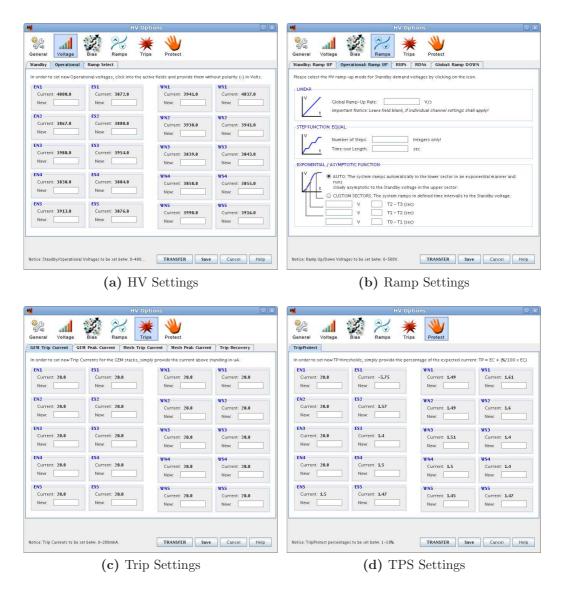

| $\begin{array}{c} 4.3\\ 4.4\end{array}$ | Options Tool and Bias Configuration of the HBD                                                                            | 125        |

|                                         |                                                                                                                           | 126        |

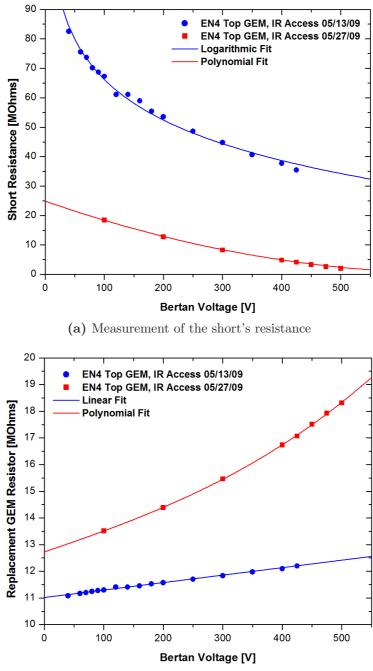

| 4.5                                     | Bertan Test Results of module EN4. The comparison of two<br>IR access days shows the development of a partial (blue line) |            |

|                                         | towards a dead short (red line).                                                                                          | 129        |

| 4.6                                     |                                                                                                                           | 131        |

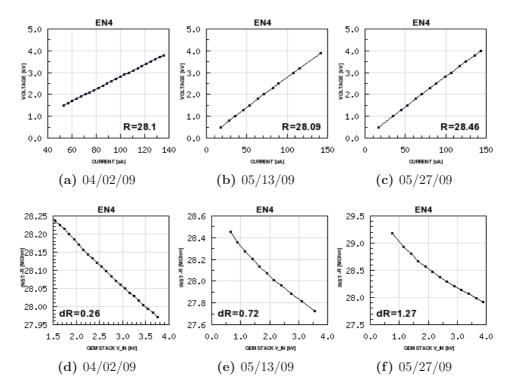

| 4.7                                     | Run-9 TPS Calibration Runs for module EN4. The voltage vs.                                                                |            |

|                                         | current relation in (a-c) remains linear, while the progression of                                                        |            |

|                                         | parallel resistance vs. voltage in (d-f) proofs the short develop-                                                        |            |

|                                         | ment                                                                                                                      | 133        |

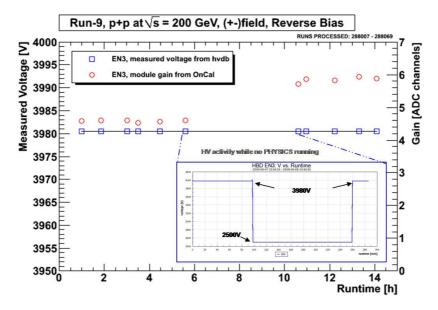

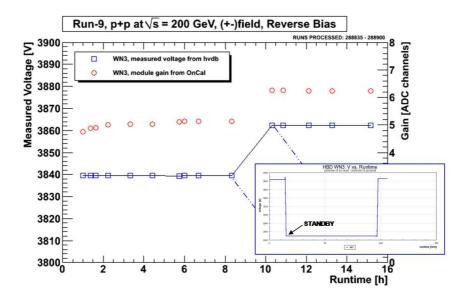

| 5.1                                     | Measured voltage and Module Gain vs. Runtime for sector EN3                                                               | 137        |

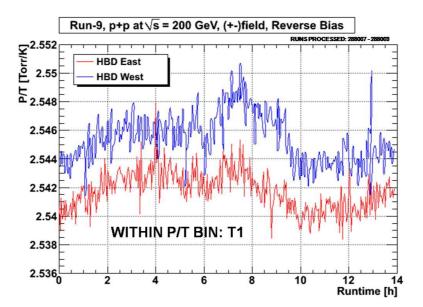

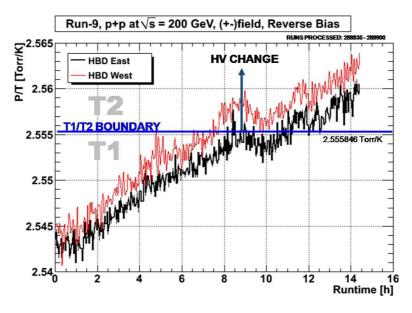

| 5.2                                     | Measured $P/T$ vs. runtime of 5.1.                                                                                        | 138        |

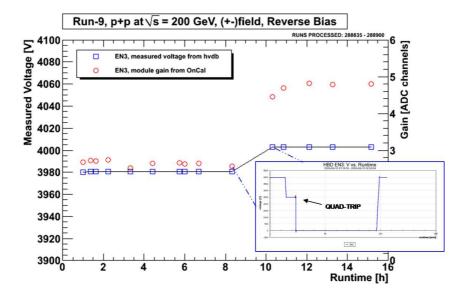

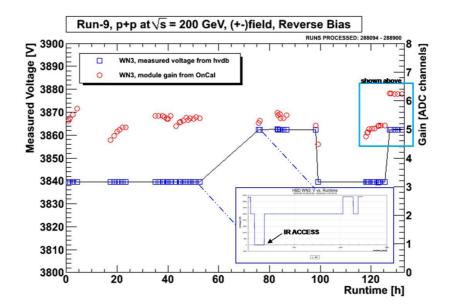

| 5.3                                     | Measured voltage and Module Gain vs. Runtime for sector EN3.                                                              | 138        |

| 5.4                                     | Measured voltage and Module Gain vs. Runtime (as 5.3) for                                                                 |            |

|                                         | sector WN3.                                                                                                               | 139        |

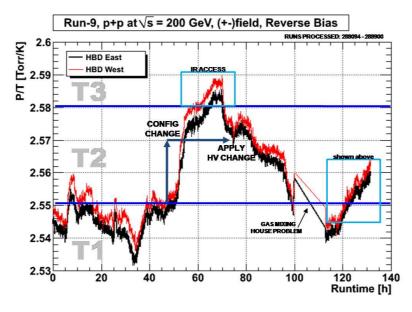

| 5.5                                     |                                                                                                                           | 139        |

| 5.6                                     | Measured voltage and Module Gain vs. Runtime for sector WN3.                                                              |            |

| 5.7                                     |                                                                                                                           | 140        |

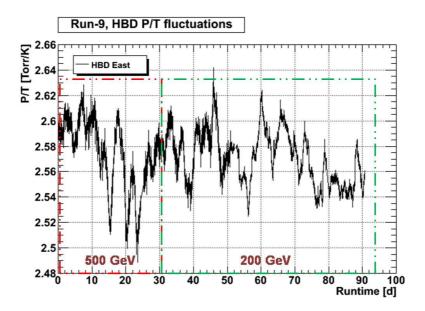

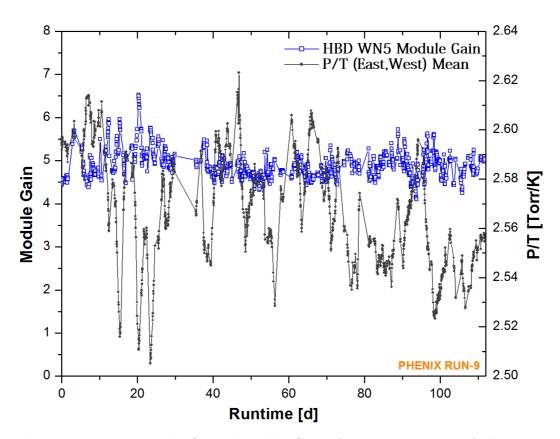

| 5.8                                     | Measured P/T vs. runtime of all runs in Run-9.                                                                            | 141        |

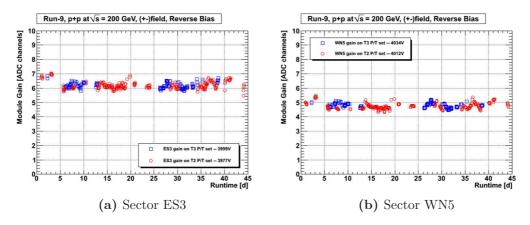

| 5.9                                     | Module Gain for P/T sets T2 and T3.                                                                                       | 141        |

| 5.10                                    | Measured P/T and Module Gain of WN5 vs. runtime of all runs in Run-9                                                      | 142        |

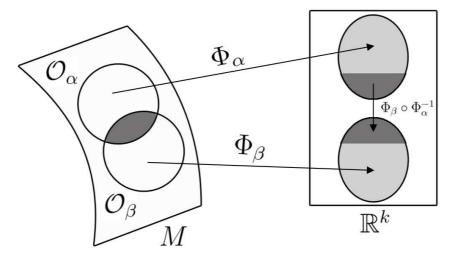

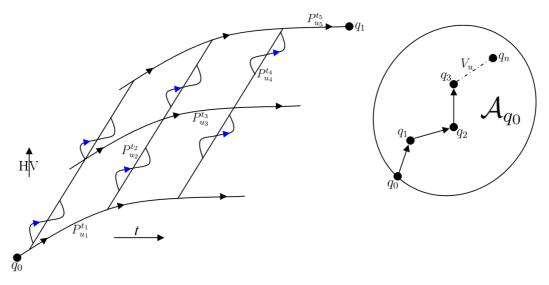

| A.1                                     | Coordinate System for HBD HVC system, defined on a smooth manifold $M$                                                    | 151        |

| A.2                                     | 2D surface of control trajectories (left) and the attainable set                                                          | 101        |

|                                         | (right) for voltage modifications by HVC                                                                                  | 152        |

|                                         |                                                                                                                           |            |

| C.1 | Overview of the hardware components of the HBD Simulation       |     |

|-----|-----------------------------------------------------------------|-----|

|     | Project.                                                        | 160 |

| C.2 | The main units of the HBD Simulation Project.                   | 161 |

| C.3 | The HVC's basic control tools used by the Shift Crew at PHENIX. | 162 |

| C.4 | The HV Options Tool for HBD Experts to configure the funda-     |     |

|     | mental HVC control parameters                                   | 163 |

| C.5 | The HV Surveillance Panel provides an overview of the current   |     |

|     | HV parameters and measurements for each channel                 | 165 |

|     |                                                                 |     |

# List of Tables

| 1.1 | Summary of PHENIX detector subsystems [7]                                                                                     | 5   |

|-----|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Divider Resistors (nominal; in $M\Omega$ ) used in Run-9                                                                      | 41  |

| 3.2 | High Voltage Control Parameters returned from the hvserver.                                                                   | 68  |

| 3.3 | Global Identifiers in hvdb for measured 1471N HV data                                                                         | 76  |

| B.1 | P/T trigger bin thresholds in Torr/K for Run-9. [center of bins (ID = CB), lower bin threshold (ID = LT), upper bin threshold |     |

|     | (ID = UT)]                                                                                                                    | 154 |

| B.2 | HV Settings for Trigger Bin T1.                                                                                               | 155 |

| B.3 | HV Settings for Trigger Bin T2.                                                                                               | 156 |

| B.4 | HV Settings for Trigger Bin T3.                                                                                               | 157 |

| B.5 | HV Settings for Trigger Bin T4.                                                                                               | 158 |

| B.6 | HV Settings for Trigger Bin T5.                                                                                               | 159 |

### Acknowledgements

I would like to thank my thesis advisor Axel Drees for giving me the unique opportunity to work within the HBD research group. The group's accomplishments are due to the united effort of many people from the Weizmann Institute of Science, Brookhaven National Laboratory, Columbia University and the Relativistic Heavy Ion Group at Stony Brook.

It has been a wonderful experience to be part of the PHENIX collaboration, which comprises some of the world's greatest minds. In particular, I am very grateful to my project advisor and mentor Craig Woody for his support of my work and thorough guidance over the past years. It was his wealth of knowledge about particle detectors that has inspired my work most. I would like to gratefully acknowledge Babak Azmoun with whom I had the pleasure to work closely throughout my time at BNL. He has been always encouraging, inspirational and fun to work with.

I extend my gratitude to Stephen Boose and Salvatore Polizzo, who have introduced me to the world of HV and its controllability. I also like to thank Alexander Milov, Tom Hemmick, Martin Purschke, Takao Sakaguchi, Ed Desmond, John Haggerty and everybody else from the PHENIX control room for their inspiring discussions and support.

I am especially thankful to my good friend Dake Feng. He taught me to overcome the boundaries from complex concepts in Theoretical Physics to their application and realization with modern computing techniques. Without his perspicacity and devotion, I would have not been able to bring my vision of this control system to life.

Lastly, I dedicate this thesis to my parents, who always believed in me and supported all my endeavors throughout my life. It is their unconditional love, encouragement, support and trust who have made me the person I am. To them, I owe more than I can put into words.

# Chapter 1

### Introduction

### 1.1 Quark Gluon Plasma and RHIC

Relativistic heavy ion collisions have proven to be an excellent method to explore nuclear matter under extreme conditions.

According to Quantum Chromodynamics (QCD), quarks are confined to hadrons in pairs of two/three and bound by gluons. At very small distances, their coupling constant  $\alpha_s$  is small and quarks begin to act as quasi-free particles (asymptotic freedom, [8, 9]). At large distances,  $\alpha_s$  increases and quarks are confined.

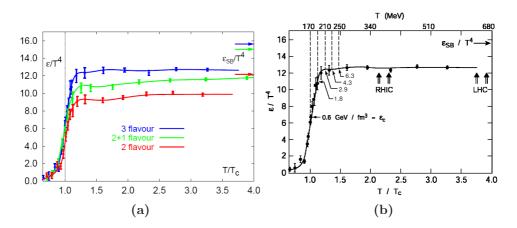

A phase transition from a color-neutral hadronic state to a state in which the degrees of freedom are the colored partons, meaning deconfined quarks and gluons, is predicted [10] to occur at energy densities of  $\varepsilon \approx 1 \text{ GeV/fm}^3$ and according to lattice QCD (see Fig. 1.1 for  $\varepsilon$  increase), can be achieved

Figure 1.1: The energy density/ $T^4$  as a function of  $T/T_c$  in QCD [1].

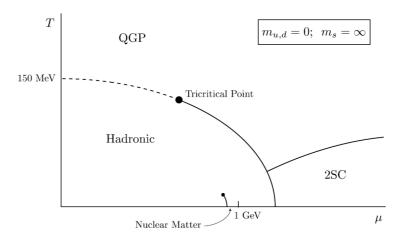

at a temperature of  $T \approx 170 MeV \approx 10^{12} K$  [11] – the so-called Quark Gluon Plasma (QGP). It is assumed that such state may have existed microseconds after the big-bang and even still exists in neutron stars at densities of 0.6 fm<sup>-3</sup>. Furthermore, calculations have shown that with disappearing baryon density and the transition to the QGP, chiral symmetry is restored after being spontaneously broken in vacuum due to non-vanishing effective quark masses [11]. In Fig. 1.2, a schematic version of the phase diagram is shown.

Figure 1.2: Schematic phase diagram of nuclear matter for 2 massless quarks and 1 heavy quark [2].

The Relativistic Heavy Ion Collider (RHIC), which started its operation in 2000, at Brookhaven National Laboratory is the world's first hadron collider consisting of two independent, intersecting rings that can accelerate heavy ions such as from gold to one hundred GeV/c order of the beam momentum with a designed luminosity of about  $2 \times 10^{26}$  cm<sup>-2</sup>s<sup>-1</sup>. The ions are accelerated in one ring clockwise, in the other counter-clockwise, and brought to collisions at six ring intersections, hosting the four experiments BRAHMS, PHOBOS, STAR and PHENIX, which have been specifically built to study a QGP with low baryon densities produced in d + Au, Cu + Cu or Au + Au collisions at center of mass energies of up to  $\sqrt{s_{NN}} = 200$  GeV. As experimental results have shown, this new state of matter with high energy densities of  $\langle \varepsilon \rangle \approx 15$  GeV/fm<sup>3</sup> has been achieved [12–15], as reported by each experiment in 2005.

Besides the study of the QGP, RHIC is also capable of colliding polarized p + p at  $\sqrt{s_{NN}} = 500$  GeV, which allow studies of the proton spin structure and the contribution of the gluon to the proton spin, and at these high energies allows to produce W bosons and therefore the opportunity to independently probe the  $\bar{u}$  and  $\bar{d}$  quarks. Nevertheless, throughout this paper we may only concentrate on collisions of gold ions, as these are of primary importance for

QGP studies at RHIC and our related discussions of the detector system we'll be introducing in chapter 2.

### **1.2** The PHENIX Experiment

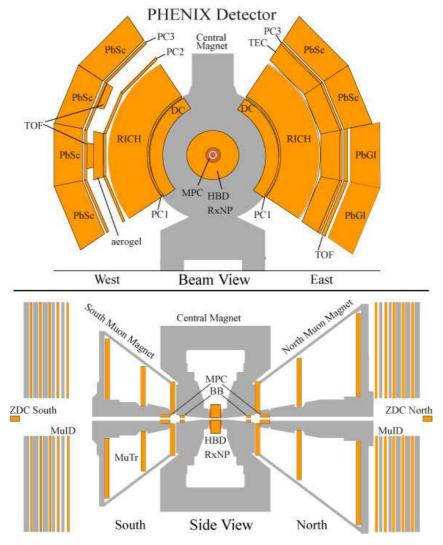

As one of the four experiments at RHIC, PHENIX (Pioneering High Energy Nuclear Interaction eXperiment) allows high precision measurements of hadrons, leptons and photons with an excellent mass resolution and represents an advanced detector system, classifiable into three categories:

- Global Detectors. The Beam-Beam Counters (BBC), covering 3.1 < ||η|| < 3.9, and Zero-Degree Calorimeters (ZDC) at η ≈ ±6.9, provide global parameters as collision vertex position and time, a centrality measurement and serve as event triggers.</li>

- Central Arms. The detector systems provide momentum, energy, and particle identification for charged tracks over a large  $p_T$  range from 0.2 GeV/c to 20 GeV/c, as well as an energy measurement of photons. The two arms are located at mid-rapidity covering each  $\eta < 0.35$  in pseudorapidity and  $\pi/2$  in azimuth. – Electron identification is realized by the Ring Imaging Čerenkov Counter (RICH) and the energy measured by the Electromagnetic Calorimeter (EMCal) in a match with the momentum determined by the Drift Chambers (DC). Hadrons are tagged via their time of flight and photons via their electromagnetic showers in the EMCal.

- Muon Arms.<sup>1</sup> Measurement of muons and decay hadrons. The two arms are at forward rapidity and cover both  $2\pi$  in azimuth.

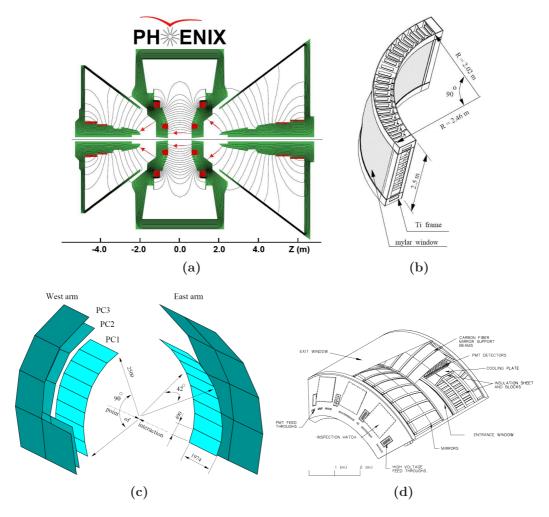

The PHENIX experimental setup is shown schematically in Fig. 1.3; the top shows the cross section of the central arms perpendicular to the beam pipe; the bottom also shows the two Muon Arms. A quick summary of rapidity and azimuthal coverage for each subsystem is summarized in Table 1.1.

<sup>&</sup>lt;sup>1</sup>Since our primary focus is on the HBD as part of the Central Arm detectors, the Muon Arms will not be explained in more detail; the reader is referred to additional literature [3].

Figure 1.3: Schematic of the PHENIX Detector configuration as of 2009. The cross section of the two central arms perpendicular to the beam pipe (top) and a view from the east with the beam axis along the horizontal direction.

| Component                                    | $\Delta \eta$        | $\Delta \phi$    | Purpose & Features                               |

|----------------------------------------------|----------------------|------------------|--------------------------------------------------|

| GLOBAL DETECTORS<br>Beam-Beam Counters (BBC) | $\pm (3.1 - 3.9)$    | $2\pi$           | Start timing, fast vertex                        |

| Zero-deg. Cal. (ZDC)                         | $\pm 2 \text{ mrad}$ | $2\pi$           | Minimum bias trigger                             |

| CENTRAL ARMS                                 |                      |                  |                                                  |

| Central Magnet (CM)                          | $\pm 0.35$           | $2\pi$           | Up to $1.15 \text{ Tm}$                          |

| Muon Magnet South (MMS)                      | -1.1 to -2.2         | $2\pi$           | $0.72 \text{ Tm for } \eta = 2$                  |

| Muon Magnet North (MMN)                      | 1.1  to  2.4         | $2\pi$           | $0.72 \text{ Tm for } \eta = 2$                  |

| Muon Magnet South (MMS)                      | -1.1 to -2.2         | $2\pi$           | $0.72 \text{ Tm for } \eta = 2$                  |

| Drift Chambers (DC)                          | $\pm 0.35$           | $2 \times \pi/2$ | $\sigma_m/m = 1\%$ at $m = 1 { m GeV}$           |

| Pad Chambers (PC)                            | $\pm 0.35$           | $2 \times \pi/2$ | Pattern recognition, tracking                    |

| Time Expansion Chambers (TEC)                | $\pm 0.35$           | $2\pi 2$         | Pattern recognition, $dE/dx$                     |

| Ring Imaging Čerenkov Counter (RICH)         | $\pm 0.35$           | $2 \times \pi/2$ | Electron ID                                      |

| Time of Flight (ToF)                         | $\pm 0.35$           | $\pi/4$          | Hadron identification, $\sigma < 100 \text{ ps}$ |

| Lead-Scintillator (PbSc)                     | $\pm 0.35$           | $\pi/2+\pi/4$    | Electron & photon ID, energy meas.               |

| Lead-Glass (PbGl)                            | $\pm 0.35$           | $\pi/4$          | Good $e^{\pm}/\pi^{\pm}$ separation              |

| MUON ARMS                                    |                      |                  |                                                  |

| Muon Tracker South                           | -1.15 to -2.25       | $2\pi$           | Tracking for muons                               |

| Muon Tracker North                           | 1.15 to 2.44         | $2\pi$           | I                                                |

| Muon Identifier South                        | -1.15 to -2.25       | $2\pi$           | Steel absorber & Iarocci tubes                   |

| Muon Identifier North                        | 1.15 to 2.44         | $2\pi$           | for $\mu$ /hadron separation                     |

Table 1.1: Summary of PHENIX detector subsystems [7].

### 1.2.1 Global and Central Arm Detectors

Let us have a closer look on a few of the most fundamental detector subsystems presently in PHENIX installed.

**Beam-Beam Counters.** The Beam-Beam Counters (BBC) provide the crucial information of collision time and vertex position, a signal one can trigger data collection on and in collaboration with the ZDC allows to determine the centrality of the collision. There are two BBCs placed  $\pm 144$  cm North and South of the center of PHENIX, whereby each consists of 64 hexagonal shaped Quartz Čerenkov counters (see Fig. 1.4, measuring charged particles produced around the beam axis and based on the detection time differences of both, allow to determine collision time/vertex.

**Figure 1.4:** The basic components of the BBC. (a) 64 PMTs are mounted to one BBC unit; (b) each single photomultiplier tube (PMT) with a timing resolution of 50ps is of 25.4mm in diameter and has a 30mm thick Quartz radiator.

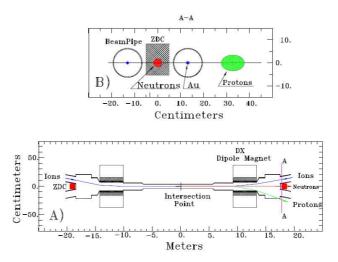

**Zero Degree Calorimeter.** Two Zero Degree Calorimeters<sup>2</sup> (ZDC) are installed 18 m from the center of PHENIX on either side in the direction of the beam pipe and have the purpose to measure spectator neutrons from nucleusnucleus collisions, which is made possible by utilizing the DX magnet in front to deflect charged particles as spectator protons (see Fig. 1.5). Each ZDC contains tungsten alloy plates of three separate modules, which are read out via one PMT. One can then determine the centrality of the collision by the anticorrelation between energy deposited in the ZDC and total charge deposited in the BBC.

<sup>&</sup>lt;sup>2</sup>Each experiment at RHIC has a pair of ZDCs installed.

Figure 1.5: Schematic top view of the interaction region (bottom); Projection of proton/neutron deflection in ZDC plane [3].

**Central Magnet** Due to the bending of charged particles in the magnetic field provided by the Central Magnet (CM), their transverse momentum can be determined. The CM consists of inner and outer Helmholtz coils inside a steel yoke, generating an axially-symmetric magnetic field around the interaction. The two coils can be run either in the same polarity (++), resulting in a total field integral of  $\int B dl = 1.5$  Tm in the first 2 m from the vertex, or can be run in opposite polarity (+-) and achieve a field free region in the first 50 cm from the vertex, which may allow a detector system in this region to assume straight tracks. The cross-section of the CM together with the Muon magnets and their fields lines in (++) configuration are shown in Fig. 1.6a.

**Drift Chambers** The main tracking detectors in PHENIX are the Drift Chambers (DC), which are multiwire gaseous chambers and based on the concept that electrons from primary ionization drift towards a wire after a time that is proportional to the distance of the track to the wire. This allows to measure trajectories of charged particles in the  $r - \phi$  plane for determination of the particle's momentum and invariant mass of pairs. Each DC arm consists of a cylindrical titanium frame, which support a large net of wires with 42 cm in radial width and 180 cm in length. A basic illustration is shown in Fig. 1.6b.

**Pad Chambers** The Pad Chambers (PC) measure points in space along straight trajectories of particles, which have left the field-active region, and allow to reconstruct the z-component of the momentum vector. The PC (see

**Figure 1.6:** Important PHENIX Central Arm detectors. (a) The cross section of the PHENIX Central and Muon Magnets are shown with their field lines in (++) configuration; (b) A Drift Chamber Frame; (c) Illustration of the PHENIX Pad Chambers; (d) A cut-away view of the PHENIX RICH detector.

Fig. 1.6c) contains of three layers of multiwire proportional chambers and are positioned behind the DC (both arms), behind the RICH (west arm) and in front of the EMCal (both arms).

**Ring Imaging Čerenkov Counter** A Ring Imaging Čerenkov Counter (RICH) is installed in each Central Arm and has the purpose to separate electrons from the large background of charged pions. It contains 48 mirrors, which focus Čerenkov radiation onto two arrays of photomultiplier tubes and uses  $CO_2$  as the radiator gas with an average of 12 photons per ring. A

schematic of the detector is shown in Fig. 1.6d.

Acceptance of Charged Particles Due to the CM field, charged particles are deflected in the azimuthal direction and so making their acceptance depended on the particle's transverse momentum  $p_T$ , charge q and effective azimuthal bent to DC,  $k_{\rm DC}$  and RICH  $k_{\rm RICH}$ , and can be described by:

$$\phi_{\min} \le \phi_0 + q \frac{k_{\text{DC,RICH}}}{p_T} \le \phi_{\max},\tag{1.1}$$

where  $\phi_0$  represents the particle's emission angle, where  $k_{\rm DC} = 0.206$  rad GeV/c and  $k_{\rm RICH} = 0.309$  rad GeV/c [16].

### **1.2.2** Low-Mass Dileptons and S/B

Electron-positron pairs or dileptons, have proven to be valuable probes to discover the hot/dense matter formed in relativistic heavy ion collisions at ulta-high energies, and allow to study QGP characteristics as chiral symmetry restoration. As results from the ChErenkov Ring Electron Spectrometer (CERES) at the Super Proton Synchrotron (SPS) at CERN have shown, a large enhancement of the dilepton yield below the  $\phi$  meson mass can be seen. This enhancement may be derived from in-medium modifications of the light vector mesons  $\rho$ ,  $\omega$  and  $\phi$ . Since these vector mesons carry the very same quantum numbers as a photon, a coupling to an electron-positron pair can be seen:

$$\pi^+\pi^- \to \rho \to \gamma^* \to e^+e^-. \tag{1.2}$$

Even though collision energies at RHIC are sufficient to study the dielectron continuum, the multiplicity from collisions is so high, hence  $dN/dy \sim 650$ , that an enormous combinatorial background is produced and in a mass range of 0.3 - 0.5 GeV/c<sup>2</sup> a signal to backround ration  $S/B \sim 1/300$  making it impossible for PHENIX to measure the low-mass pair continuum. This combinatorial background results primarily from uncorrelated pairs formed by tracks from  $\pi^0$  Dalitz decays and  $\gamma$  conversions:

$$\pi^0 \to e^+ e^- \gamma; \qquad \gamma \to e^+ e^-.$$

(1.3)

In order to reduce this background, an upgrade solution had been developed for PHENIX and already installed in 2007 – the *Hadron Blind Detector*. In the following chapter, we shall discuss the principles this new detector system is based on.

# Chapter 2 The HBD Detector

The PHENIX detector in its original design has only limited capabilities to measure  $e^+e^-$  pairs in the low-mass region due to the overwhelming yield of combinatorial background pairs, as we have already pointed out in Section 1.2.2. The recognition and rejection of these pairs is especially exacerbated by the incomplete azimuthal acceptance of PHENIX, which allows a low momentum electron from a dielectron pair and its spiraling track in the magnetic field to become unrecognized by the Central Arm detectors, while its counterpart contributes to the background through an erroneous or random combination of a detected positron from a separate pair.

A new detector system was developed to overcome this limitation of the PHENIX experiment and serve as an upgrade to the Central Arm detectors right about the collision vertex: the **Hadron Blind Detector** or hereafter referred as the **HBD**.

In this chapter, we introduce the fundamentals of the HBD and its first trial of operation in Run-7 at RHIC. The critical issues of the detector's high voltage (HV) supply as found during this run as well as their subsequential studies are presented. In summary of this initial HBD commissioning, the baseline problem preventing a successful operation is defined to motivate the development of a new *High Voltage Control and Monitoring System* for the HBD, which we outline in conclusion and preparation of its thorough discussion in this thesis.

### 2.1 Detector Concept

The fundamental idea of the HBD to address the combinatorial background issue in PHENIX is to take advantage of the fact that the opening angle of pairs derived from  $\gamma$  conversions/ $\pi^0$ -Dalitz decays is considerably smaller than of pairs originating from light vector meson decays. Based upon this important fact, an HBD was designed and shall be discussed in the following.

### 2.1.1 Design and Implementation

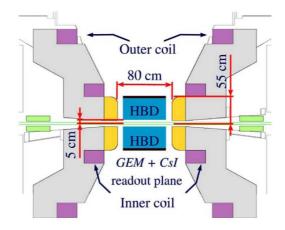

By operating the PHENIX Central Magnets in (+ -) configuration, an almost field-free cylindrical volume<sup>1</sup> is established, extending radially out to ~ 50-60 cm from the beam axis. This permits the preservation of straight particle trajectories and the corresponding opening angles of pairs within this region. Therefore, the HBD has been designed to fit into this beneficial environment surrounding the collision vertex. The detector consists of two identical semicircular arms, referred to as *East* and *West* arm, with an active spacial coverage of radially ~ 5cm (outside walls of beam pipe) to ~ 55cm (before inner coil) with respect to the beam axis. The layout for the HBD installation in PHENIX with the location of the coils is illustrated in Fig. 2.1.

Figure 2.1: Location of the HBD and inner/outer coils in PHENIX.

Herewith, the baseline conditions are given to identify electrons from  $\pi^0$ -Dalitz decays and photon conversions by exploiting their small opening angle. The question of how to achieve this goal has been extensively studied in Monte Carlo simulations in [17] with different detector configurations and the aim of achieving a S/B = 10/1 or higher at the  $\phi$  mass, which would represent a reduction of the combinatorial background of about two orders of magnitude. The results show an electron identification with an efficiency of > 90%, a double hit recognition of background pairs on a single pad at a similar level

<sup>&</sup>lt;sup>1</sup>The compensation of the existent field allows only the integral of the magnetic field to be almost completely zero, but does not eliminate field components of non-zero value.

and a reasonable  $\pi$  rejection factor of ~ 100. Such a detector cannot be realized by only applying an opening angle cut to the collected data (e.g. 200 mrad), since many different particles are present. Therefore, the HBD needs to be capable of measuring Čerenkov photons produced in the gas volume of the detector.

Several potential key elements of this new detector system were considered and analyzed. The following final design has been adopted: a proximityfocused windowless Čerenkov detector with pure CF<sub>4</sub> as radiator and detector gas, utilizing triple-stacks of Gas Electron Multiplier (GEM) foils with a photocathode coated on the uppermost GEM as well as ~ 6.5 cm<sup>2</sup> hexagonal readout pads for charge collection.

As illustrated in Fig. 2.2, each arm consists of 2 large front and 8 small back panels made of layers of FR4/Honeycomb/FR4 ( $250\mu$ m/19mm/ $250\mu$ m), glued to a rigid FR4 frame, while the two side panels are mounted with plastic screws. The outer panels serve the detector with gas and high voltage (HV). There are two HV dividers mounted on either side with the capability of supplying voltage to 3 GEM detectors through corresponding HV terminals on the inside. The 5 inner panels are each equipped with 2 Triple-GEM detectors with an underlying readout plane consisting of 96 pads, which are connected to Front End Electronics (FEE) boards on the outer surface of the

**Figure 2.2:** HBD Design Overview. In (a) an exploded view of one HBD arm with one side panel for clarity removed is shown with its installation around the beam pipe in (b).

detector. Each FEE consists of differential pre-amplifiers for each pad and Flash Analog-Digital Converters (ADC), which are accessed by the PHENIX Data Acquisition (DAQ) system during a so-called run of data taking<sup>2</sup>.

For a more detailled understanding of the HBD principles, the key elements, such as the photocathode, radiator/detector gas, and GEM foils as well as the detailled method of identifying electrons with this detector scheme are discussed in the following sections.

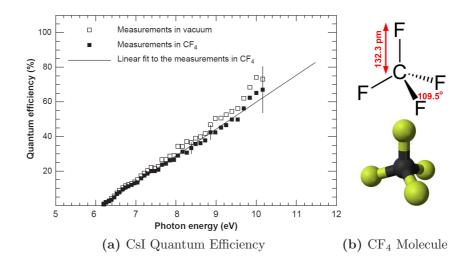

### 2.1.2 Photocathode and Gas

Instead of focusing mirrors as in a RICH detector, which due to geometrical constraints in PHENIX would be impossible to implement within the field-free region, a UV light sensitive detector shall be placed in the path of particles produced in collisions. Therefore, the Čerenkov photons screening the detector form a circular blob image ( $r_{\rm blob} \sim 1.15$  cm) rather than a ring when using a mirror. Extensive studies in [4, 18] have shown, utilizing *CsI* as a film photocathode permits an absolute quantum efficiency of about 80% in the extreme ultra-violet (see Fig. 2.3a).

In order to allow the HBD a radiation budget < 3% of the radiation length, a separation of radiator and amplification media is unfavorable, since the window in between would serve as an auxiliary source of Čerenkov light and increase the radiation length. Therefore, in addition to the benefit of being sensitive to the full Čerenkov spectrum, a windowless configuration was adopted.

The choice of radiator and detector gas for the HBD has been one of the primary focuses of evaluation in the very early days of the HBD's conceptional design. Attention was focused on industrially produced *carbon tetrafluoride* (CF<sub>4</sub>; see Fig. 2.3b). Due to fluorine  $(1s^2, 2s^2, 1p^5)$ , having the smallest atomic radius of the period 2 elements and being the most electronegative element in the periodic table, its bound with carbon (C-F bond) is extremely strong, 105.4 kcal mol<sup>-1</sup>, and highly polarized, with the electron density substantially on the fluorine atom. This statement arises from the significant electrostatic attraction between  $F^{\delta-}$  and  $C^{\delta+}$ , instead of the classical covalent bond-sharing of electrons. Important for our study, however, is that the 2p electrons are held more closely by the nuclear charge (endothermic, -401.2 kcal mol<sup>-1</sup>) than for example for oxygen (-312.9 kcal mol<sup>-1</sup>), making it extremely difficult and

$<sup>^{2}</sup>$ A "DAQ run" or the mode of "data taking" in this paper, shall be referred to the readout process of the HBD pads and storage of event data during ongoing collisions at RHIC.

**Figure 2.3:** Absolute CsI Quantum Efficiency measurement in vacuum and  $CF_4$  (a; [4]), and a model of the  $CF_4$  molecule in (b).

very much E-field dependent to generate an electron- $F^+$  pair; [19]. Thus one can benefit from the unique opportunity with  $CF_4$  as radiator and detector gas to take control over the detector's gain stability through the appropriate application of high voltage.

Another crucial factor is the transparency to Cerenkov photons of wavelengths < 108nm that allows the detector to exploit the high quantum efficiency of the CsI cathode in the deep VUV wavelength region. One can estimate the refractive index of CF<sub>4</sub> by either using each individual atomic index or measure the Gladstone-Dale constant with, for example, a Twyman-Green interferometer and He-Ne laser of known 633nm wavelength, and finds an excellent high refraction index<sup>3</sup> of  $(n-1) = 620 \times 10^{-6}$ , making pure CF<sub>4</sub> suitable for a high level of Čerenkov light production and considerable for the HBD. As a consequence of the very large bandwith from ~ 6eV (CsI threshold) to ~ 11.5eV (CF<sub>4</sub> cut-off), single electrons transversing ~ 50cm of the CF<sub>4</sub> in the HBD, radiate Čerenkov photons, which produce ~ 35 primary photoelectrons through the Photo-electric Effect on the CsI, and therefore yield a large figure of merit  $N_0 \approx 822$  cm<sup>-1</sup>.

### 2.1.3 Gas Electron Multipliers

The fundamental challenge one faces is to design the HBD such that it can be sensitive to a very small amount of extracted photoelectrons from the CsI

<sup>&</sup>lt;sup>3</sup>The refraction index depends on the photon energy.

cathode, but be insensitive to electrons originating from ionization trails of charged hadron tracks. The difference between the two sources is that photoelectrons only appear close to the surface of the CsI film, while ionization electrons are spread throughout the gas medium. As originally proposed in [20], one can amplify localized primary charge from the photocathode by employing a parallel plate detector; Čerenkov light passes through a transparent Anode grid, creates photoelectrons on a photocathode beneath, which are then extracted, amplified and collected by the Anode. Such a detector has only one major issue: photons emitted during the amplification of photoelectrons shine back to the photocathode and therefore distort the measurement. This difficulty has been overcome by utilizing the *Gas Electron Multiplier*, hereafter referred as a **GEM** foil [21], since a strong suppression of photon-feedback is automatically given by its geometry, as discussed below.

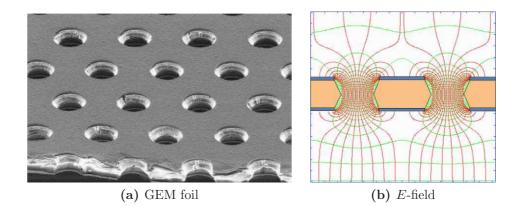

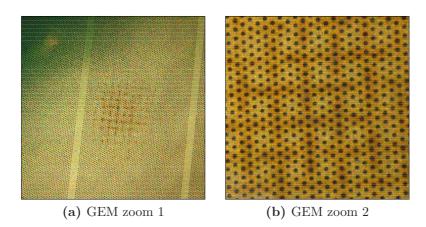

A GEM consists of a thin, metal-clad polymer foil with a high density of chemically etched equidistant narrow holes. Commonly, Kapton and Cu are used as insulator and top/bottom metal layers, respectively. As manufactured at CERN, the hole pattern is first engraved on both sides applying photolithography, before the polymer is dissolved with a solvent equally. This procedure causes a slight double-conical shape of the holes as shown in a microscopic view of a GEM foil in Fig. 2.4a. Each foil has an equilateral triangular hole pattern at a pitch of  $140\mu m$  (center-to-center) and an inner hole diameter of ~  $50\mu m$  in the Kapton and an outer hole diameter of ~  $70\mu m$  in the Cu.

The principle of a GEM is based on *electron avalanche multiplication* in strong electric fields produced by application of a potential difference between

Figure 2.4: A Microscopic view of a GEM is shown in (a) and electric field lines of increased density within holes is illustrated in (b) when a voltage to the electrodes is applied.

the two conducting sides inside the holes. Each individual hole represents a proportional amplifier: electrons close to the GEM surface drift into the holes, multiply in avalanche and transfer into the next region. Since the electrodes are electrically separated from the charge collection pads, the pattern design for the readout unit can be chosen very flexible. One may also cascade several foils to achieve *higher gains* and a more *stable operation* as studied in [22, 23].

With the objectives of the HBD, the above principle has been customized and extended. All GEM foils cover an active area of  $27 \times 23 \text{cm}^2$  and are segmented into so-called 28 strips with each 27cm in length, 8.1mm in width and separated by a 1 mm thin Kapton line from its neighboring strip. Every top electrode of a strip is soldered to a current-limiting 20M $\Omega$  segmentation resistor to a foil-wide top electrode or Top HV bus. This segmentation reduces the stored energy during a discharge, meaning a spark from top to bottom electrode, and this way prevents severe damages to the GEM. The bottom electrode of each strip, on the other hand, is directly connected to a foil-wide bottom electrode. An image of an HBD GEM foil is shown in Fig. 2.5a.

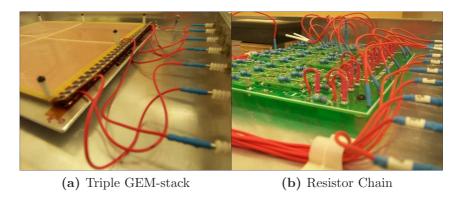

Furthermore, one GEM foil is converted into a semi-reflective photocathode by evaporating a  $\sim 300$  nm layer of CsI onto its top surface. In order to prevent a chemical reaction with the Cu, a thin layer of Au with another layer of Ni for a good gold-adhesion is coated on the surface. As demonstrated in [4], photoelectrons extracted from the CsI cathode are pulled into the nearest hole by a strong electric field (see Fig. 2.4b), which is to the order of 100 kV/cm at the center of the hole, and responsible for the avalanche process. Two uncoated GEM foils are cascaded below to build a so-called triple-GEM stack with equidistant 1.5 mm gaps in-between, before the total charge is collected by hexagonal pads. In order to allow the construction of a stack with Mesh and prevent any warping of GEM surfaces, a FR4 frame stretches each GEM foil and with a 0.3 mm wide support across, maintains a constant gap between the GEMs. The primary elements of the stack shall be called **Top GEM** or T-GEM, Middle GEM or M-GEM and Bottom GEM or B-GEM. The entire GEM detector module is illustrated in Fig. 2.5b. The connection of every HV bus from GEMs in triple-stack configuration to a divider is discussed in Section 2.2.1.

Facing the detector's gas volume, meaning towards the collision vertex, a stainless steel **Mesh** of  $\sim 90\%$  transparency is placed 1.5 mm above the photocathode and helps to establish a drift field, which drifts ionization electrons from hadrons or in general **minimum ionizing particles** (MIP) towards the Mesh, meaning away from the GEM holes, when biased by a slightly positive

**Figure 2.5:** A photograph of an HBD-sized GEM foil is shown in (a) and in (b) a Triple-GEM stack with Mesh is illustrated.

voltage with respect to the top electrode of the GEM beneath. Such configuration finally empowers the HBD to be mostly insensitive to signals from charged hadrons / MIPs or to be *hadron-blind*!

### 2.1.4 Electron Identification Principle

In summary of the previous sections, we may now define the basics of HBD operation through high voltage (HV) application and introduce some of the conventional expressions we will be using throughout this thesis.

As originally proposed in [23], the gap between the Mesh and T-GEM is called "drift" with field  $E_{\rm D}$ ; the gap between GEMs are called "transfer" with fields  $E_{\rm T}$ ; and the gap between B-GEM and the pad readout (ground) is called "induction" with field  $E_{\rm I}$ . The height of all gaps is fixed to 1.5 mm by the GEM foil's frame. The potential difference between the Mesh and the top electrode of the T-GEM (coated with CsI), is commonly referred to as the delta of their applied voltage and abbreviated with **dV**. In other words, one can express the dV by subtracting the magnitude of the Mesh potential with the magnitude of the T-GEM potential. A detailled calculation of fields and the dV is given in Section 3.2.1.

The HBD can be operated in two modes, which are defined by the configuration of  $E_{\rm D}$ : the **Reverse Bias** (RB) or **Forward Bias** (FB) mode. In Fig. 2.6, the principle of each is illustrated. In Forward Bias mode, the Mesh electrode is biased with a *positive dV* such that charge produced by a traversing MIP within the drift gap is collected towards the GEM and amplified in

Figure 2.6: The basic principle of Reverse and Forward Bias operation of the HBD; the response to Čerenkov photons and MIPs to either mode is illustrated. The dashed arrows in red represent the photoelectron extraction from the CsI cathode, while arrows in green represent the transport of photoelectrons or/and ionization charge. The direction of the electric field lines within the gaps is displayed with blue arrows.

avalanche of the three gain stages of the triple-GEM stack. A Cerenkov photon produces a photoelectron (pe<sup>-</sup>) in the CsI surface of the T-GEM and is extracted and transferred into a nearby hole, where it undergoes the amplification process. The total charge is then collected on the readout plane. The overall signal one can plot in a pulse-height spectra thus represents a combination of amplified photoelectron and MIP charge, where the latter signal contribution is overwhelming and generates a background preventing the identification of Čerenkov blobs due to electrons. The novelty of the HBD is found by running it in its characteristic mode of reversed  $E_{\rm D}$ , the Reverse Bias mode. It is defined by the Mesh electrode biased with a slight *negative dV* such that most of the MIP produced charge in the drift gap is collected by the Mesh, while the strong GEM field close to the CsI surface still allows photoelectrons to be collected and amplified.

As recent simulations in [5] have shown, electrons within a volume defined approx.  $150\mu$ m above the T-GEM surface – meaning photoelectrons and ionization charge – are transferred into the GEM holes and therefore contribute to the final signal. This also means that about 90% of the ionization charge

**Figure 2.7:** Collection of ionization charge (a; [4]) and relative photoelectron collection efficiency (b; [5]) vs. the drift field.

deposited by hadrons in the drift gap is swept away towards the Mesh.

Early experiments with  $\alpha$ -particles and 1 GeV/c pions at KEK (High Energy Accelerator Research Organization, Japan) have proven a significant decrease of collected ionization charge when switching from FB to RB mode within an  $E_{\rm D}$  of ~ 0.1 kV/cm (see Fig. 2.7a). One can find an optimal *photoelectron (pe) collection efficiency* as a function of the field in the drift gap, which is defined as the ratio of the number of photoelectrons collected and amplified by the GEM to the number of photoelectrons produced for a given quantum efficiency of the CsI photocathode. Experimental results of this characteristic property, as shown in Fig. 2.7b, shall emphasize the importance of setting the drift field with respect to its defining sensitivity to photons and insensitivity to MIPs. This however also means that the HV System powering this GEM detector needs to be capable of precisely generating such  $E_{\rm D}$ -field in order to allow a maximal suppression of the MIP signals, or simply speaking, allowing the Hadron Blind Detector to be hadron blind.

In the analysis of data taken in RB mode, one can use the RICH and EM-Cal to identify electrons in an event, reconstruct their track with the Drift Chamber, and find pads of single and double hits by studying the measured amplitudes for each pad. Simulations have shown that a MIP of high momentum may produce ~ 1 Čerenkov photoelectron<sup>4</sup> and a single primary electron produces ~ 36 photoelectrons. Thus dilepton pairs from  $\gamma$  conversions and  $\pi^0$  Dalitz decays can be distinguished due to their small opening angle from

<sup>&</sup>lt;sup>4</sup>The threshold for photon production by hadrons  $m/\sqrt{2(n-1)}$  depends on their mass m and refractive index n of CF<sub>4</sub>. Due to a Čerenkov  $\gamma$ -threshold of ~ 28.3 in CF<sub>4</sub>, pions with a momentum below 4 GeV will not contribute with photons illuminating the CsI cathode.

twice the number of photoelectrons produced by the single hits from light vector mesons.

### 2.1.5 Correlation of P/T and Module Gain

The quantities of pressure and temperature are known to have significant impact on the operational characteristics of any gaseous detector, especially for the HBD. Let us quickly review the governing fundamentals of this fact.

One can utilize the basic principles of classical kinetic theory of gases to estimate drift and diffusion properties of electrons in a gaseous medium at temperature T. Assuming the absence of any external force, electron motion can be expressed with a Maxwellian energy distribution, as shown by Boltzmann and Langevin, where an average thermal energy of  $\varepsilon_{\rm T} = 3_2^{\prime} kT \simeq 0.04 \text{ eV}$ at room temperature. Under the application of an electric field E, however, we know that, except for very low fields, the mobility of electrons is not constant and their energy can increase substantially between collisions with the gas molecules; due to Townsend, one can find the electron mobility  $\mu$  to be

$$\mu = \underbrace{\frac{3\sqrt{3\pi}}{8\sqrt{2}}\sqrt{\frac{m+M}{M}}}_{X} \frac{e\lambda M^{1/2}}{m\sqrt{3kT}} = X\frac{e}{m}\left\langle\frac{\lambda}{c}\right\rangle \simeq \frac{e}{m}\tau, \qquad (2.1)$$

where e denotes the electron charge, m its mass, M the mass of a molecule, k the Boltzmann constant,  $\lambda$  and c are the electron's mean free path and RMS velocity, respectively, and  $\tau$  the mean time between collisions. The factor X, as originally found by Langevin, can be approximated to its multiplying constant of 0.815, when one accounts for the fact that m is very small compared with M. As found by Boltzmann,  $c = 1.086 \ \bar{v}$ , which by substitution of  $\bar{v}$  for c changes X to 0.75 and  $\mu \simeq e\lambda/m\bar{v}$ . Since  $\lambda$  varies inversely as the gas pressure P and the electron energy, and therefore v, is a function of the reduced field E/P, the electron mobility is thus a function of P as 2.1 indicates.

Although all the above obtained relations hold, one needs to be careful when neglecting the factor X and building a theoretical model on a 'purely' Maxwellian distribution. When transforming Boltzmann's equation by a method of Hilbert, and deducing a series of coupled transport and energy conservation equations by expanding in Legendre polynomials,

$$f(\varepsilon,\phi) = \sum_{j=0}^{\infty} f_j(\varepsilon) P_j(\eta), \qquad (2.2)$$

with  $\varepsilon = \|\mathbf{p}^2/2m\|$  and  $\eta = \cos \phi$  representing the angle  $\phi$  between v and  $\mathbf{a} = e\mathbf{E}/m$ , one can find for  $f_0$ , considering  $m/M \ll 1$  for electrons:

$$(x+z)f_0'' + (2+x+b/x)f_0' + 2f_0 = 0, (2.3)$$

where

$$x = \varepsilon/kT, \ z = \frac{1}{3} (eE\lambda)^2 (2m/M)(kT)^2.$$

(2.4)

The solution for the first term  $f_0 = (x + z)^z e^{-x}$ , which has been solved by Pidduck (1916), shows that electrons do not acquire exactly a Maxwellian distribution of velocities, and in fact leads to a 11% increase of the numerical factor X in 2.1. Additionally, already at this stage, many assumptions were made: (i) the frequency  $\nu$  of an electron-molecule collision depends linearly on the thermal velocity  $v_{\rm T}$  of an electron; (ii)  $\nu \approx \nu_e$ , meaning the elastic collision frequency  $\nu_e$  is expected to be much larger than the inelastic  $\nu_{in}$ ; (iii) the concentration of free electrons in the gas medium is assumed to be very small; (iv) only a constant and uniform electric field E is considered; the distribution function is neither (v) spatial nor (vi) time dependent; and since  $m/M \ll 1$ , (vii) only the first two terms are calculated. Unfortunately, Pidduck's solution remained unseen for a very long time, until independently rediscovered by Druyvesteyn, which then induced the development of electron transport theory by Compton, Davydov, Morse *el al.* (1935), Frost and Phelps (1962), and many others. However, even today, more than a century since Boltzmann's equilibrium, and various solutions for (i - vi), the limitation of (vii) remains only partially solved with a truncation after i = 3. Nevertheless, for our experimental study, the boundaries of measurable precision given by the current state of technological progress, and final understanding and reasoning for the related P/T subsystem of HVC, we may reduce our discussion to the combination of achievements by Pidduck  $(T \neq 0)$ , Davydov and Morse ( $\nu =$  $\nu(v)$ :

$$f_{0}(v) = C \exp\left(-m \int_{0}^{v} dv \frac{v}{kt + Ma^{2}/3 (\nu_{0} - \nu_{1})^{2}}\right), \qquad (2.5)$$

$$f_{1}(v) = -\frac{a}{\nu_{0} - \nu_{1}} \frac{df_{0}}{dv},$$

where a normalizing constant  $C \ll 1$  is introduced, and energy transfers in processes as rotational and vibrational excitations with molecules accommodated. What one shall for our purposes only deduce from 2.5 is that the number of free electrons capable of ionizing and exciting increases with the strength of the applied *E*-field, which one can for simplicity see when allowing  $\lambda$  to be independent of v:

$$f \propto C \exp\left(-\frac{\varepsilon^2}{e^2 E^2 \lambda^2}\right),$$

(2.6)

where  $\varepsilon$  is the energy of the excitation/ionization. The mean free path  $\lambda$  can then be obtained from the first Townsend coefficient  $\alpha$ , meaning the number of electron-ion pair created per unit length of drift:

$$\alpha = \lambda^{-1} = \frac{\sigma(\varepsilon)}{k} \frac{P}{T} \simeq 2.69 \times 10^{19} \frac{P}{760} \frac{273}{T} \sigma(\varepsilon) \text{ cm}^{-3}, \qquad (2.7)$$

where the mobility of electrons standardized to 760 Torr and 0°C. The numerical term has been retrieved from a drift chamber performance study at CERN and is given to the reader for dimensional interest. Based on different molecular cross-sections at higher electron energies, in some gases, the collision cross-section  $\sigma(\varepsilon)$  and so  $\tau$  varies significantly along with E (Ramsauer). As a consequence, drift velocities and diffusion behavior can significantly differ for various gases at certain values of field and P/T. This means that depending on the chosen detector gas, for which one can use the corresponding Ramsauer curve to deduce  $\sigma(\varepsilon)$ , the detector performance may vary tremendously and affect the gain: The number of secondary electrons produced due to ionization by a primary electron transversing the gas over a total average distance of  $s = \mu E/\alpha \bar{v}$ , before neutralizing with a positive ion of the medium, is proportional to the gain G, and can be found as

$$G = A \exp\left(B \int \alpha(s) ds\right) \propto \exp\left(\frac{P}{T}\right),$$

(2.8)

where A and B are free variables. Since a change in P/T results in a corresponding exponential variation in gain, this has an even more significant impact for the HBD performance, as a triple-GEM configuration has to be taken into account:

$$G_{\rm HBD} \propto \exp\left(\frac{P}{T}\right)^3.$$

(2.9)

This concludes a systematic introduction of the problem we are facing. A detailled approach to this issue is presented in Section 3.4.8.

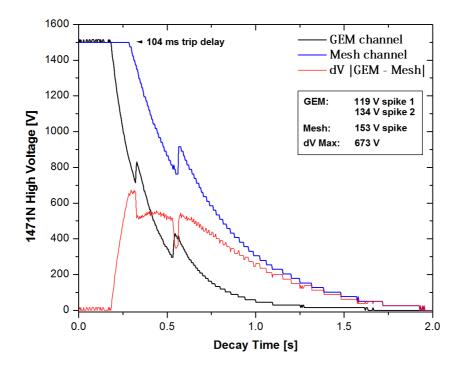

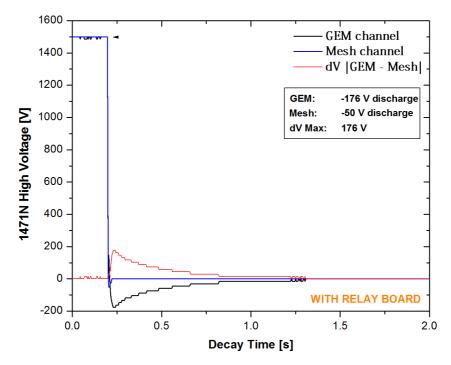

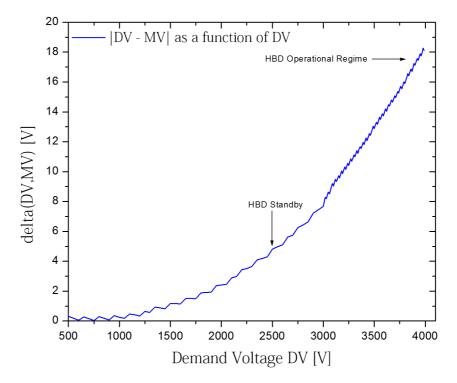

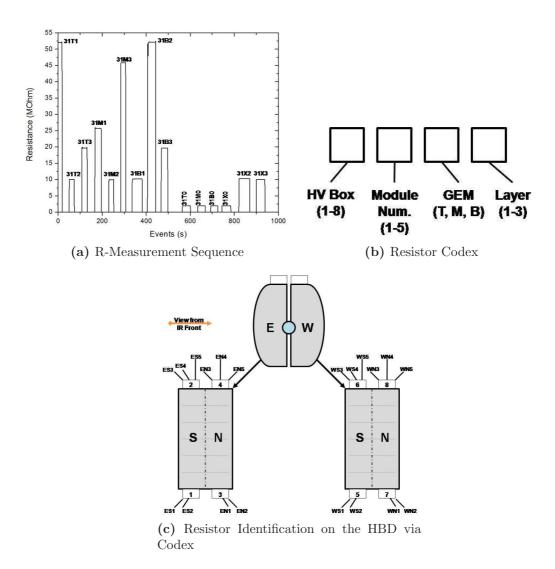

## 2.2 Commissioning in Run-7