# **Stony Brook University**

# OFFICIAL COPY

The official electronic file of this thesis or dissertation is maintained by the University Libraries on behalf of The Graduate School at Stony Brook University.

© All Rights Reserved by Author.

### Scalable End-to-End Data I/O over Enterprise and Data-Center Networks

A Dissertation presented

by

Yufei Ren

to

The Graduate School

in Partial Fulfillment of the

Requirements

for the Degree of

**Doctor of Philosophy**

in

**Computer Engineering**

Stony Brook University

**August 2015**

#### **Stony Brook University**

The Graduate School

#### Yufei Ren

We, the dissertation committee for the above candidate for the Doctor of Philosophy degree, hereby recommend acceptance of this dissertation

Dantong Yu - Dissertation Advisor Adjunct Professor, Department of Electrical and Computer Engineering

Yuanyuan Yang - Chairperson of Defense Professor, Department of Electrical and Computer Engineering

Shudong Jin

Adjunct Professor, Department of Electrical and Computer Engineering

Michael A. Bender Associate Professor, Department of Computer Science

Fan Ye Assistant Professor, Department of Electrical and Computer Engineering

This dissertation is accepted by the Graduate School

Charles Taber

Dean of the Graduate School

#### Abstract of the Dissertation

### Scalable End-to-End Data I/O over Enterprise and Data-Center Networks

by

#### Yufei Ren

#### **Doctor of Philosophy**

in

#### **Computer Engineering**

Stony Brook University

#### 2015

Data-intensive applications in commercial cloud and scientific computing demand ultra-high-speed end-to-end data access capability between data storage and computing locations. Meanwhile, advancements in hardware systems continuously change the landscape of data centers core capabilities, i.e., computing, networking, and storage. The two trends expose new research and development challenges and opportunities to bring the bare-metal capacity and performance of state-of-the-art hardware to the rising needs for high performance by applications.

Simply deploying and tuning existing software and services on state-of-theart platforms does not necessarily ensure expected performance due to the overhead on data-copy in OS kernel functions and conservative network protocol. We adopt holistic approach, from the ground up, to reconsider network protocol, storage management, and software architecture, and align them with the new hardware characteristics to better orchestrate system resources. This is extremely challenging in several aspects. First, we can not rely on existing data-copy based OS libraries and network protocols. Secondly, simple synchronous sequential programming paradigm and network protocol becomes barrier to system performance. Therefore, the new design should follow more complex asynchronous parallel model and carefully investigate the tradeoff between the programming overheads and performance improvement.

Two major objectives are the focus of this work: designing user-level endto-end protocol and software to coordinate data movements and to bypass OS kernels, and scaling storage caching system performance in multi-core environments with large scale asymmetric memory layout (NUMA). We design and build real systems to achieve these objectives. First, to fully utilize hardware capabilities, we propose an asynchronous memory-centric software framework for high throughput data-intensive applications. We implement a zerocopy data movement protocol using asynchronous Remote Direct Memory Access (RDMA) to maximize the parallelism of data transmission. The design achieves 97% network hardware bandwidth. Our software achieves more than 2× speedup over the existing solutions (for example, GridFTP) in replicating data across the entire storage-to-storage path. Secondly, we design and implement a NUMA-aware caching system for storage area networks that optimizes in-memory data locality on serving raw storage blocks. We further improve its performance with our decentralized and parallel event processing framework. The data locality awareness provides up to 80% throughput improvement on large scale memory caching system; The decentralized event processing shows its linear scalability with the number of threads on multi-core systems.

The unprecedented data volume and the continuing trend of adopting cloud

computing and storage by industry and consumers give rise to the pressing need for efficient software design and network protocol to distribute and replicate data over high performance networks. Our research focuses on the need and proposes a scalable framework to manage and coordinate multi-/many-core computing, deep hierarchy storage and high speed network in a coherent way. Therefore, this framework enables in-situ data retrieval, checksum calculation, encryption, and transmission to address the growing concerns of data privacy, security, integrity and on-demand delivery in the cloud era. It paves the path to harness multi-core/many-core architecture, i.e., GPGPU and Intel Coprocessor, by accelerating data I/O, to replace out-dated software that was designed for traditional rotary magnetic disks, and to enhance the IOPS throughput of storage system to incorporate newly-emerging Solid State Drives (SSD) and Non-volatile random-access memory (NVRAM).

To Qi and Kaylee

# **Contents**

| Li | List of Figures xii  List of Tables xv  Acknowledgements xvi |         |                                                |    |  |

|----|--------------------------------------------------------------|---------|------------------------------------------------|----|--|

| Li |                                                              |         |                                                |    |  |

| A  |                                                              |         |                                                |    |  |

| Pι | Publications xvii                                            |         |                                                |    |  |

| 1  | Intr                                                         | oductio | n                                              | 1  |  |

|    | 1.1                                                          | Resear  | rch Motivation                                 | 2  |  |

|    |                                                              | 1.1.1   | Big Data Needs Efficient Movement              | 2  |  |

|    |                                                              | 1.1.2   | Hardware Exposes Opportunities and Challenges  | 4  |  |

|    |                                                              | 1.1.3   | Limitations in Existing Solutions              | 5  |  |

|    | 1.2                                                          | Resear  | rch Challenges and Research Goals              | 7  |  |

|    |                                                              | 1.2.1   | Achieve Zero-Copy In An End-to-End Data Path   | 7  |  |

|    |                                                              | 1.2.2   | Scale Zero-Copy Based Network Protocol In WANs | 8  |  |

|    |                                                              | 1.2.3   | Caching Locality in Large-Scale NUMA Systems   | 9  |  |

|    |                                                              | 1.2.4   | Towards Scalable End-to-End Data I/O Systems   | 9  |  |

|    | 1.3                                                          | Disser  | tation Contributions                           | 10 |  |

|    | 1.4                                                          | Disser  | tation Overview                                | 12 |  |

| 2  | Bacl                                                         | kgroun  | d                                              | 14 |  |

|    | 2.1                                                          | RDM     | A and Zero-Copy Techniques                     | 14 |  |

|    |                                                              | 2.1.1   | RDMA Semantics and Performance Analysis        | 17 |  |

|    |                                                              | 2.1.2   | OS Kernel Zero-Copy Techniques                 | 19 |  |

|   | 2.2 Asynchronous High Throughput Computing and Thread-based |          |                                                      |    |

|---|-------------------------------------------------------------|----------|------------------------------------------------------|----|

|   |                                                             | Concu    | rrency                                               | 20 |

|   |                                                             | 2.2.1    | RDMA Asynchronous Programming Model                  | 22 |

|   |                                                             | 2.2.2    | Asynchronous Storage I/O                             | 23 |

|   | 2.3                                                         | NUMA     | A Architecture                                       | 23 |

|   |                                                             | 2.3.1    | SMP and NUMA Architecture                            | 24 |

|   |                                                             | 2.3.2    | Asymmetric Memory Layout                             | 24 |

|   | 2.4                                                         | iSCSI/   | iSER and Storage Caching System                      | 25 |

|   |                                                             | 2.4.1    | iSCSI and iSER                                       | 25 |

|   |                                                             | 2.4.2    | Caching Layer in iSCSI/iSER                          | 25 |

|   | 2.5                                                         | Summ     | ary                                                  | 26 |

| 3 | ACE                                                         | ES Softv | vare Architecture                                    | 27 |

|   | 3.1                                                         | Introdu  | action                                               | 27 |

|   | 3.2                                                         | Existin  | ng High Throughput Solutions                         | 30 |

|   | 3.3                                                         | Memo     | ry-Centric Asynchronous Design                       | 32 |

|   |                                                             | 3.3.1    | Design Goals                                         | 32 |

|   |                                                             | 3.3.2    | End-to-end Staged Asynchronous Software Architecture | 34 |

|   |                                                             | 3.3.3    | Stage Implementation                                 | 36 |

|   |                                                             | 3.3.4    | Uncertainty and Determinism                          | 38 |

|   |                                                             | 3.3.5    | Memory Centric Design and Memory State Transition .  | 38 |

|   | 3.4                                                         | Evalua   | tion                                                 | 40 |

|   |                                                             | 3.4.1    | Experimental Setup                                   | 40 |

|   |                                                             | 3.4.2    | RDMA Asynchronous I/O Evaluation                     | 41 |

|   |                                                             | 3.4.3    | ACES-FTP End-to-End Evaluation                       | 42 |

|   | 3.5                                                         | Conclu   | asion                                                | 43 |

| 4 | Scal                                                        | able RI  | OMA-based Data Transfer Protocol                     | 45 |

|   | 4.1                                                         | Protoc   | ol Overview                                          | 46 |

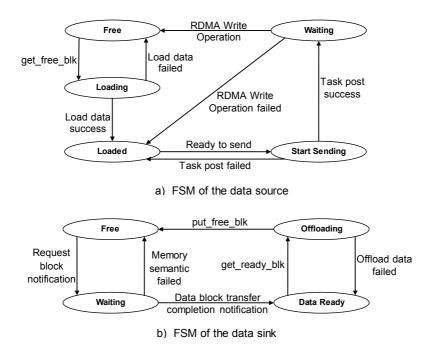

|   | 12                                                          | Finite   | State Machines Modeling                              | 18 |

|   | 4.3 | Conne  | ction Management and Message Format                      | 49 |

|---|-----|--------|----------------------------------------------------------|----|

|   | 4.4 | Discus | ssion on Scalability                                     | 52 |

|   |     | 4.4.1  | Scalability to Next Generation High Speed Networks       | 52 |

|   |     | 4.4.2  | Scalability to Wide Area Networks                        | 52 |

|   | 4.5 | Evalua | ntion                                                    | 53 |

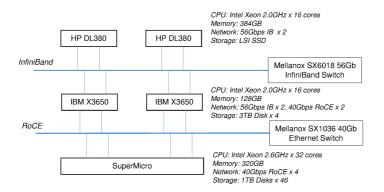

|   |     | 4.5.1  | Testbed Setup                                            | 53 |

|   |     | 4.5.2  | Parameter Configuration and Tuning                       | 55 |

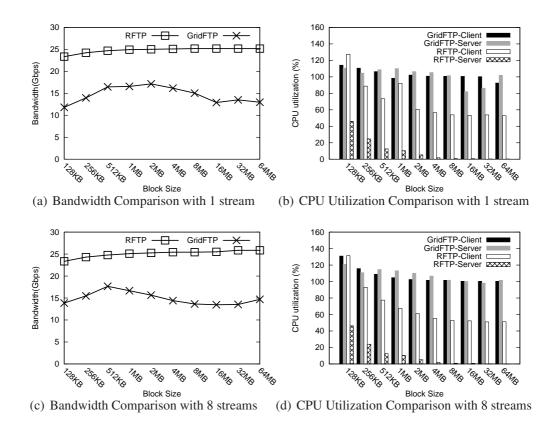

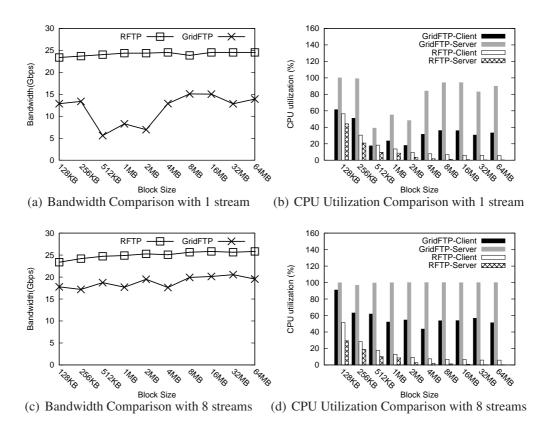

|   |     | 4.5.3  | Experimental Results over LAN                            | 55 |

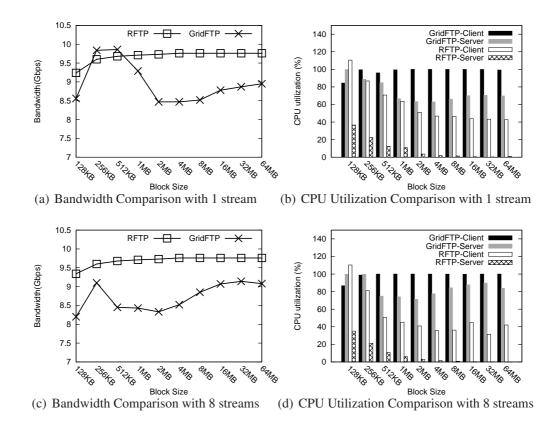

|   |     | 4.5.4  | Experimental Results over WAN                            | 59 |

|   | 4.6 | Summ   | ary                                                      | 60 |

| 5 | NUN | MA-Awa | are Cache for Storage Area Networks                      | 62 |

|   | 5.1 | I/O Co | ost Analysis with iSCSI                                  | 63 |

|   |     | 5.1.1  | Processing Time and Throughput Modeling                  | 63 |

|   |     | 5.1.2  | The Impact of Queuing Delay                              | 64 |

|   |     | 5.1.3  | Cost Analysis with Our Testbed System                    | 65 |

|   | 5.2 | NUM    | A-aware Cache Design and Implementation                  | 66 |

|   |     | 5.2.1  | Software Overview                                        | 67 |

|   |     | 5.2.2  | Cache Organization                                       | 69 |

|   |     | 5.2.3  | Routing I/O Tasks to NUMA Nodes                          | 71 |

|   |     | 5.2.4  | Placement of the I/O Interpreting Function               | 73 |

|   |     | 5.2.5  | Discussions on Overhead and Scalability                  | 74 |

|   | 5.3 | Decen  | tralized Event Processing                                | 75 |

|   |     | 5.3.1  | Scalability Limitations in Standard iSCSI/iSER Servers . | 76 |

|   |     | 5.3.2  | Events Categories in iSCSI/iSER Servers                  | 77 |

|   |     | 5.3.3  | Decentralized Event Processing Model                     | 78 |

|   |     | 5.3.4  | RDMA Network Events Processing                           | 81 |

|   | 5.4 | Evalua | ation with Synthetic Workloads                           | 82 |

|   |     | 5.4.1  | System Setup                                             | 83 |

|   |     | 542    | Evaluation of Request Processing Time                    | 84 |

|   |             | 5.4.3   | Random Access on Fully Cached Data                      | . 86      |

|---|-------------|---------|---------------------------------------------------------|-----------|

|   |             | 5.4.4   | Decentralized Event Processing Evaluation               | . 89      |

|   |             | 5.4.5   | Queuing Delay Analysis                                  | . 90      |

|   | 5.5         | Evalua  | ation with Real-life Workloads                          | . 95      |

|   |             | 5.5.1   | The PostMark Workload                                   | . 95      |

|   |             | 5.5.2   | The YCSB Workload                                       | . 96      |

|   |             | 5.5.3   | Decentralized Event Processing Evaluation with YCSB     | . 97      |

|   | 5.6         | Summ    | ary                                                     | . 99      |

| 6 | RDN<br>tion | MA-Bas  | sed NUMA-Aware End-to-End Performance Optimiza          | a-<br>101 |

|   | 6.1         | Introd  | uction                                                  | . 101     |

|   | 6.2         | Backg   | round                                                   | . 105     |

|   |             | 6.2.1   | Memory Access in NUMA Multi-core Systems                | . 105     |

|   |             | 6.2.2   | Protocol Offloading                                     | . 106     |

|   |             | 6.2.3   | A Motivating Experiment                                 | . 107     |

|   | 6.3         | Charac  | cterization of System Design and Network Application    | . 109     |

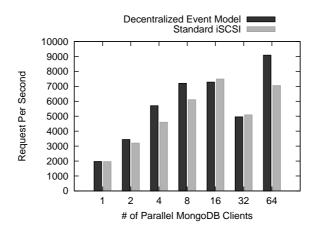

|   |             | 6.3.1   | Back-End Storage Area Network Design                    | . 109     |

|   |             | 6.3.2   | RDMA Application Protocol: Cost Analysis and Imple-     |           |

|   |             |         | mentation                                               | . 111     |

|   | 6.4         | Experi  | imental Results                                         | . 113     |

|   |             | 6.4.1   | Testbed Setup                                           | . 113     |

|   |             | 6.4.2   | Evaluation of Memory-Based Storage System Perfor-       |           |

|   |             |         | mance                                                   | . 116     |

|   |             | 6.4.3   | End-to-End Data Transfer Performance                    | . 118     |

|   |             | 6.4.4   | Experimental Results over 40 Gbps WAN RoCE Link         | . 122     |

|   | 6.5         | Conclu  | usions                                                  | . 124     |

| 7 | Rela        | ited Wo | ork                                                     | 125       |

|   | 7.1         | Softwa  | are Architecture for Highly Concurrent and Asynchronous |           |

|   |             | Data F  | Processing                                              | . 125     |

|   | 7.2 | High F   | Performance Data Transfer Protocol and Software 127   |

|---|-----|----------|-------------------------------------------------------|

|   | 7.3 | Hardw    | are and Software Accelerated Key Value Stores 130     |

|   | 7.4 | Storag   | e Cache Performance Optimization                      |

| 8 | Con | clusions | s and Future Work 133                                 |

|   | 8.1 | Conclu   | asions                                                |

|   | 8.2 | Future   | Work                                                  |

|   |     | 8.2.1    | Efficient I/O for High Speed Parallel Hardware Accel- |

|   |     |          | erator                                                |

|   |     | 8.2.2    | Asynchronous I/O Event Scheduling                     |

|   |     | 8.2.3    | Memory-based Data Backup over SAN 136                 |

|   | 8.3 | Summ     | ary                                                   |

# **List of Figures**

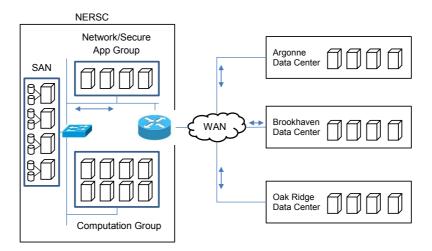

| 1-1 | Data transfer and synchronization between data centers   | 3  |

|-----|----------------------------------------------------------|----|

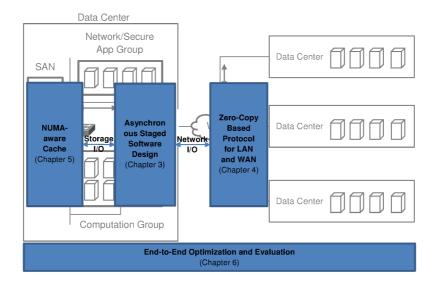

| 1-2 | Dissertation overview                                    | 13 |

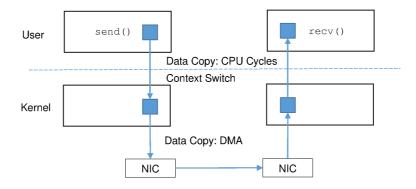

| 2-1 | Data path of TCP/IP applications                         | 15 |

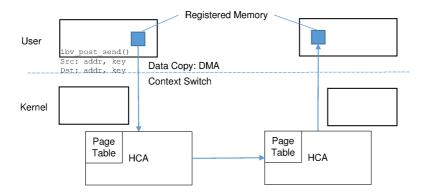

| 2-2 | Data path of RDMA applications                           | 16 |

| 2-3 | Mellanox ConnectX supports both RDMA over InfiniBand and |    |

|     | RDMA over Converged Ethernet (RoCE) devices              | 16 |

| 2-4 | One-sided vs. Two-sided in RoCE                          | 18 |

| 2-5 | One-sided vs. Two-sided in InfiniBand.                   | 18 |

| 3-1 | Data transfer workflow with OpenSSH scp and sftp         | 31 |

| 3-2 | End-to-end asynchronous software architecture            | 34 |

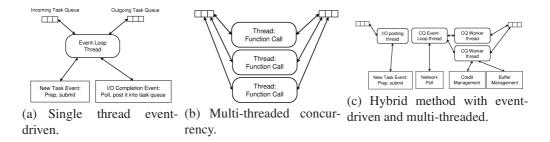

| 3-3 | Stage implementation methods                             | 36 |

| 3-4 | End-to-End memory status transition                      | 39 |

| 3-5 | Testbed connectivity                                     | 40 |

| 3-6 | RDMA asynchronous performance in 40 Gbps Ethernet        | 41 |

| 3-7 | Performance comparison among OpenSSH-SCP, HPN-SSH, and   |    |

|     | ACES-FTP                                                 | 42 |

| 4-1 | Data transfer protocol overview.                         | 46 |

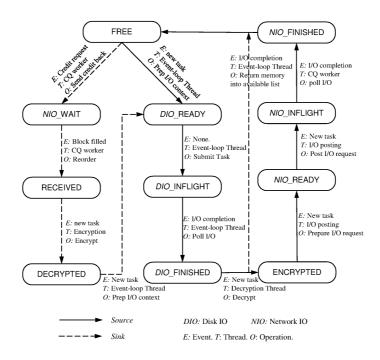

| 4-2 | Finite state machine modeling                            | 47 |

| 4-3 | Message format description                               | 49 |

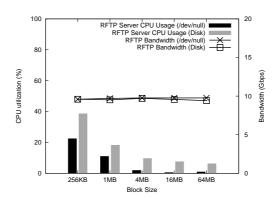

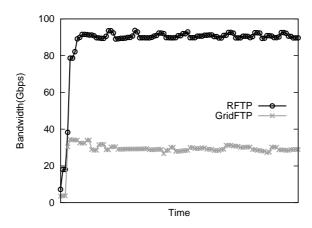

| 4-4 | GridFTP vs. RFTP over RoCE in LAN                        | 56 |

| 4-5 | GridFTP vs. RFTP over InfiniBand in LAN                  | 58 |

| 4-6  | GrifFTP vs. RFTP over RoCE in WAN                                | 59 |

|------|------------------------------------------------------------------|----|

| 4-7  | RFTP scalability with disk access                                | 60 |

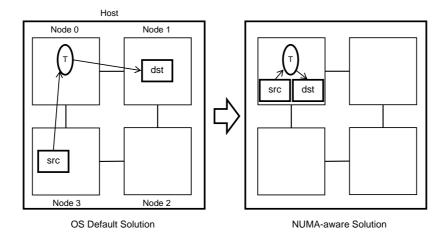

| 5-1  | Memory copy routine on a four-node NUMA host                     | 63 |

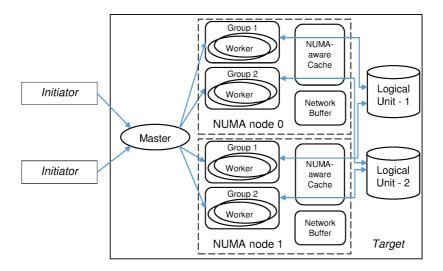

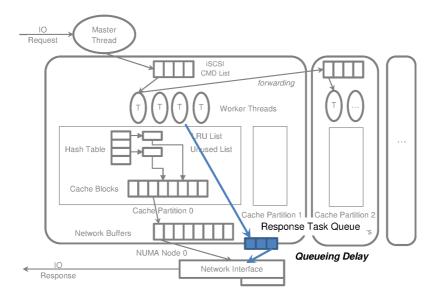

| 5-2  | NUMA-aware cache for tgtd                                        | 67 |

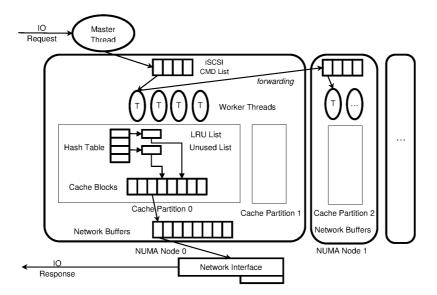

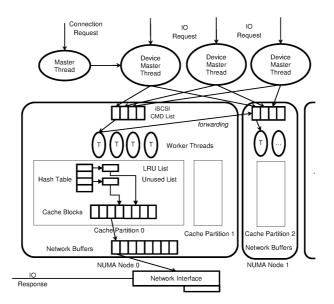

| 5-3  | Software architecture of NUMA-aware cache                        | 69 |

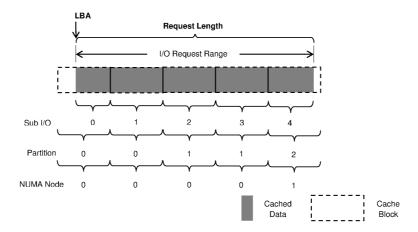

| 5-4  | I/O request decomposition                                        | 71 |

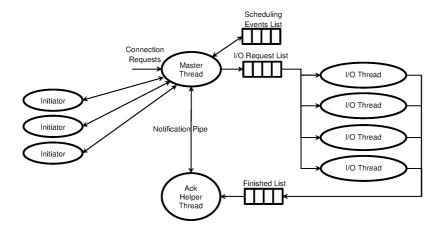

| 5-5  | Event processing model in the standard software                  | 76 |

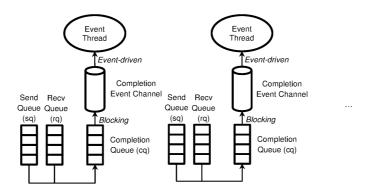

| 5-6  | Decentralized event processing Model for the iSCSI/iSER servers. | 79 |

| 5-7  | Centralized processing for RDMA network events                   | 80 |

| 5-8  | Decentralized processing for RDMA network events                 | 81 |

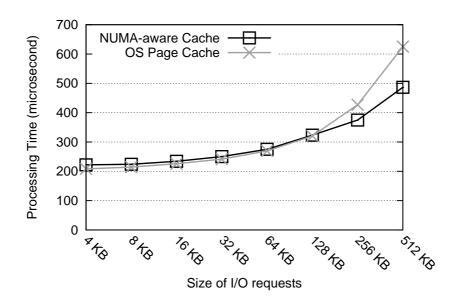

| 5-9  | Processing time of I/O requests with different sizes             | 84 |

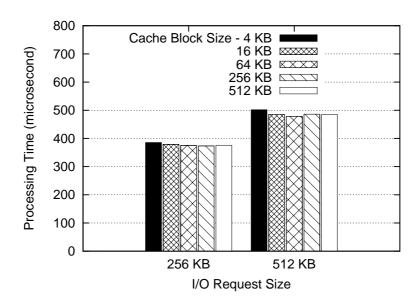

| 5-10 | Processing time with various cache block sizes                   | 85 |

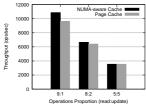

| 5-11 | NUMA-aware cache vs. page cache with random access               | 86 |

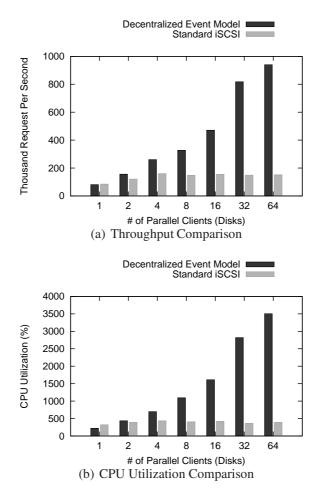

| 5-12 | Decentralized event processing vs. standard centralized one      | 88 |

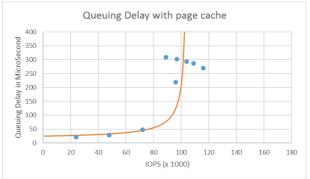

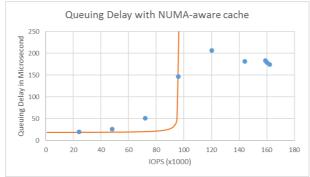

| 5-13 | Queuing delay in iSCSI target system                             | 90 |

| 5-14 | Queuing delay with small I/O requests                            | 91 |

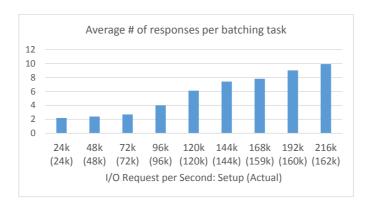

| 5-15 | Average number of responses within a batching task in NUMA-      |    |

|      | aware cache solution                                             | 94 |

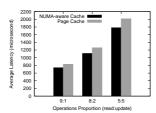

| 5-16 | The results of YCSB over MongoDB                                 | 96 |

| 5-17 | Throughput of YCSB workloads over MongoDB which in turn          |    |

|      | retrieve data from iSER target in decentralized optimization     | 98 |

| 6-1  | iSER tuning in NUMA architecture with multiple adapters 1        | 10 |

| 6-2  | Data block transfer delay breakdown                              | 11 |

| 6-3  | The breakdown of data transfer cost at 40 Gbps rate              | 12 |

| 6-4  | RDMA-based end-to-end system connectivity in LAN                 | 13 |

| 6-5  | The DOE's ANI 40 Gbps RoCE WAN between NERSC and ANL. 1          | 14 |

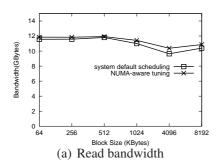

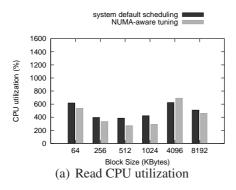

| 6-6  | iSER bandwidth comparison between default scheduling and         |    |

|      | NIIM A-tuning                                                    | 17 |

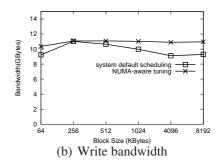

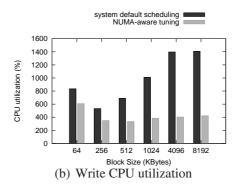

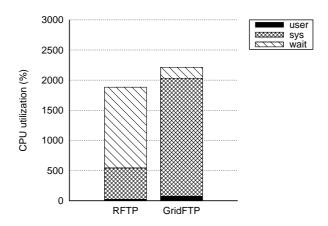

| 6-7  | iSER CPU utilization comparison between default scheduling         |    |

|------|--------------------------------------------------------------------|----|

|      | and NUMA-tuning                                                    | 8  |

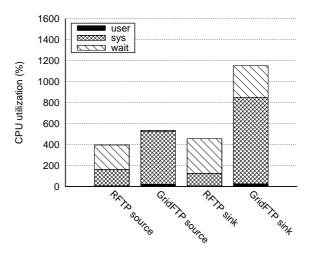

| 6-8  | Throughput of end-to-end data transfer over 25 minutes 11          | 9  |

| 6-9  | CPU utilization breakdown for RFTP and GridFTP                     | 9  |

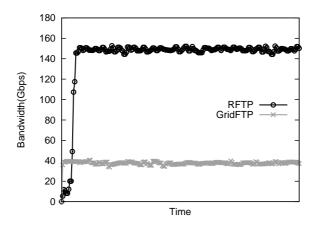

| 6-10 | Throughput of bi-directional end-to-end data transfer over 50      |    |

|      | minutes                                                            | 20 |

| 6-11 | CPU utilization breakdown for RFTP and GridFTP bi-directional      |    |

|      | test                                                               | 21 |

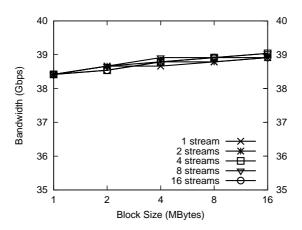

| 6-12 | RFTP bandwidth with various block sizes and numbers of streams. 12 | 22 |

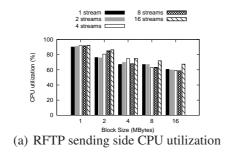

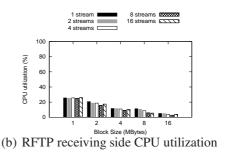

| 6-13 | RFTP CPU utilization with various block sizes and numbers of       |    |

|      | streams 12                                                         | )3 |

# **List of Tables**

| 3.1 | Software policies for each part of hardware advances | 28  |

|-----|------------------------------------------------------|-----|

| 4.1 | RFTP testbed description                             | 54  |

| 5.1 | Testbed configuration for NUMA-aware cache           | 82  |

| 5.2 | IOPS comparison under different workloads            | 92  |

| 5.3 | PostMark performance                                 | 95  |

| 6.1 | End-to-end testbed configuration                     | 115 |

# Acknowledgements

First and foremost, I would like to express my deep gratitude to my advisor, Prof. Dantong Yu. Throughout my Ph.D. studies, Prof. Yu has given me numerous pieces of priceless advice. He patiently listened my thoughts in every meeting discussion through over five years, and provided insightful feedback to motivate my research forward. He also gave me substantial research freedom to explore and broaden my research interests. I am extremely thankful for his support and encouragement to complete this exceptional Ph.D. journey.

My thanks also go to Prof. Shudong Jin, for his guidance to my research exploration and technical writing. I have benefited from numerous discussions during these years.

I would also like to thank my dissertation committee members, Prof. Yuanyuan Yang, Prof. Michael Bender, and Prof. Fan Ye, for their insights and suggestions on my research. Prof. Yang was instrumental to several key steps in my graduate studies and exemplary in her passion and rigorous attention toward research. I would especially like to thank Prof. Bender and Prof. Ye for their invaluable advice to my future research.

Thanks to Dr. Li Zhang and Dr. Yandong Wang, who helped to start my career at IBM T.J. Watson Research Center. Thanks to Dr. Zhikui Wang, Dr. Dejan Milojicic, and Dr. Harumi Kuno, for providing me the rewarding internship opportunity at HP Labs.

As an international student at Stony Brook University, I would also like to express my gratitude to many individuals, including my international advisor,

Jasmina Gradistanac, and ECE department staff members, Susan Hayden and Rachel Ingrassia. They made my life easier and more comfortable.

I am fortunate to have the opportunities to work with stellar and hardworking colleagues: Tan Li, Cheng Chang, Shun Yao, Zhenzhou Peng, Jin Xu, Hao Huang, Li Shi, and Shuchu Han.

Finally, not the least, great thanks to my wife, my parents, and my maternal grandparents, for their love, strong encouragement, and unconditional supports. Kaylee, my dear daughter, your little feet made the biggest footprints in this Ph.D. journey.

# **Publications**

# **Journal Publications**

- Yufei Ren, Tan Li, Dantong Yu, Shudong Jin, Thomas Robertazzi, "Design, Implementation, and Evaluation of a NUMA-Aware Cache for iSCSI Storage Servers", *IEEE Transactions on Parallel and Distributed Systems* (TPDS), vol.26, no. 2, pp. 413-422, Feb. 2015, doi:10.1109/TPDS.2014.2311817.

- Yufei Ren, Tan Li, Dantong Yu, Shudong Jin, Thomas Robertazzi, "Design and Testbed Evaluation of RDMA-Based Middleware for High-Performance Data Transfer Applications", *Journal of Systems and Software*, Volume 86, Issue 7, July 2013, Pages 1850-1863, ISSN 0164-1212, 10.1016/j.jss.2013.01.070.

### **Conference Publications**

- Tan Li, Yufei Ren, Dantong Yu, Shudong Jin, "Resources-conscious Asynchronous High-speed Data Transfer in Multicore Systems: Design, Optimizations, and Evaluation", In *Proceedings of Parallel and Distributed Processing Symposium (IPDPS)*, 2015 IEEE International, vol., no., pp.1097,1106, 25-29 May 2015 28th International, (IPDPS '15), May, 2015.

- Yufei Ren, Tan Li, Dantong Yu, Shudong Jin, Thomas Robertazzi, "Design and Performance Evaluation of NUMA-Aware RDMA-Based Endto-End Data Transfer Systems", In *Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis, (SC '13)*, Denver, Colorado, November 2013.

- Tan Li, Yufei Ren, Dantong Yu, Shudong Jin, Thomas Robertazzi, "Characterization of Input/Output Bandwidth Performance Models in NUMA Architecture for Data Intensive Applications", In *Proceedings of the International Conference on Parallel Processing*, (ICPP '13), Lyon, France, October 2013.

- Yufei Ren, Tan Li, Dantong Yu, Shudong Jin, Thomas Robertazzi, Brian L. Tierney, Eric Pouyoul, "Protocols for Wide-Area Data-intensive Applications: Design and Performance Issues", In *Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis, (SC '12)*, Salt Lake City, Utah, November 2012.

# **Workshop Publications**

Yufei Ren, Tan Li, Dantong Yu, Shudong Jin, Thomas Robertazzi, "Middleware Support for RDMA-based Data Transfer in Cloud Computing", In *Proceedings of the High-Performance Grid and Cloud Computing Work*shop, Shanghai, China, May 2012.

# Chapter 1

# Introduction

The fast growing data volume in data centers demands scalable data I/O systems to transfer data efficiently and to cache data effectively for supporting big data processing, analysis, visualization and archiving. The existing and upcoming applications, such as social networks, scientific computing, online storage and inter data center backup, have been generating high volume data traffic in tera-/peta-byte scale [1]. At the same time, data services become more centrally managed among distributed physical storage systems that aggregates data from billions of users. Cloud computing and cloud storage are the example of this paradigm [2]. On the other hand, network capacity in storage area network (SAN), virtual host area network in hypervisor and its Ethernet adaptors (VAN), local area network (LAN), wide area network (WAN), have been exponentially growing in last ten years, largely driven by rapid improvements in opto-electronics technologies. This growth trend which closely reassembles Moore's law, coupled with the fast-evolving software-defined network technologies (SDN), offers necessary bandwidth on demand to upper layer data applications and presents challenges of bridging the widening gap between the software layer and hardware in the network application stack. Therefore, the data I/O systems is one of the cornerstone in accelerating data centers' big data processing capability.

Hardware advancements have been changing the performance of I/O systems and the capacity of memory significantly. The design of existing software I/O systems, however, mostly relies on the general purpose OS abstractions (i.e., system calls) and services, which in turn hide the control plane, i.e., TCP flow control and transmission, from the upper layer application and expose data plane based on data copy, i.e., copy data between application user space and OS kernel space. On one hand, data copies among OS layers and modules consume a large portion of system resources [3] and undermines the software scalability in high performance networks. On the other hand, advanced hardware characteristics motivate researchers to re-think data placement and locality in such environment to efficiently utilize state-of-the-art hardware characteristics.

This dissertation tackles research challenges in the field of high performance data I/O by decoupling software functions, and integrate appropriate components into control plane and data plane. It defines a scalable software framework to cope with hardware advances in enterprise and data centers networks. It achieves the bare-metal performance of high-speed networks for end-to-end data movement and betters data locality in serving cached data of storage systems.

### 1.1 Research Motivation

### 1.1.1 Big Data Needs Efficient Movement

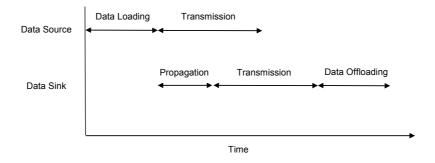

Various data-intensive applications require ultra high-speed data transfer capability, such as those in data centers, cloud-computing environments [2], and distributed scientific computing. They frequently need data transfer software to support true end-to-end data and file delivery, i.e., between the storage systems that are attached to the source and the destination hosts. Figure 1-1 shows an intuitive example from the Department of Energy's (DOE's) Magellan cloud

Figure 1-1: Data transfer and synchronization between data centers. This is an example from the Department of Energy's (DOE's) Magellan cloud data centers that are interconnected by multiple 100 Gbps links of the DOE's Advanced Network Initiative.

data centers [4] that are interconnected by multiple 100 Gbps links provided by the DOE's Advanced Network Initiative (ANI). The architectural layout in Figure 1-1 can often be found in the DOE's National Laboratories, for example, three leadership computing facilities hosted at Argonne National Laboratory, Oak Ridge National Laboratory, and the National Energy Research Scientific Computing Center, respectively, and the tier-1 Large Hadron Collider computing facilities at Brookhaven National Laboratory and Fermilab that play a vital role in searching and analyzing exascale experimental data for scientific insights and discoveries [5]. The science programs (climate simulation, astrophysics, high-energy physics, material science, and system biology) at these DOE Laboratories frequently rely on high-performance supercomputers and server clusters, along with back-end storage systems encompassing hundreds of petabyte disk and tape storage, to run computing and data intensive applications, and to move data from experiments and simulations between computing and storage infrastructures and frequently across high-speed wide area networks. It becomes a necessity to design and deliver efficient high-performance data I/O and data transfer systems for these computing facilities. To scale up data transfer to

100Gbps and higher, we must overcome various bottlenecks along the end-toend paths that consist of hosts, networks, and storage systems.

### 1.1.2 Hardware Exposes Opportunities and Challenges

Recent hardware advances, such as network protocol offloading and large (non-volatile) memory (RAM) integration in deep memory hierarchy, have been improving bare-metal systems performance and capability significantly. It's a predictable trend that data center servers become more compact (less footprint), more energy efficient (less power consumption), and more powerful (less investment). For example, by 2020, warehouse-scale computers (WSCs) will have up to 100,000 cores and 100Petabyte Non-Volatile Memory (NVM) which are connected by high-speed radix switches and communication links spreaded across several racks [6,7].

Remote direct memory access (RDMA), non-uniform memory access (NUMA), and multi/many-core are among the mainstream hardware techniques to achieve high efficient architecture and to provide fundamental building blocks for modern supercomputers and data centers. In particular, remote direct memory access (RDMA) [8] is one of these promising technologies that were developed as the supercomputer interconnect technology in the domain of high-performance computing (HPC). By enabling network adapters to transfer bulk application memory blocks to or from remote memory, it eliminates data copies in protocol stacks, reduces software interrupt handling, and achieves low latency and high bandwidth. InfiniBand [9, 10], a ubiquitous RDMA implementation, dominates the technology market of intra-data-center interconnects. Recently RDMA over Converged Ethernet (RoCE) [11] and the Internet wide area RDMA protocol (iWARP) [12] extended the RDMA capabilities to LAN and WAN between geographically distributed data centers. Consequently, RDMA provides an opportunity to facilitate data synchronization and replication within or between data

centers for applications to accomplish their routine tasks in a highly efficient manner. It is necessary to employ these advanced network technologies and protocols to fully utilize the bare-metal bandwidth of high-speed networks (100 Gbps and higher), and to eliminate network performance bottlenecks. One of our main goal in this dissertation is to introduce RDMA into the high throughput cloud computing and confirm its viability in new domains.

In addition, as the numbers of CPU sockets and cores per CPU processor grow in the multi-core architecture of modern computer hosts, it becomes increasingly difficult and inefficient to ensure the same memory access latency across all CPU cores by using a centralized and shared memory bus. A stateof-the-art CPU architecture integrates a memory controller as a core component within the CPU die and discards the external controller hub that would have become a bottleneck in a multi-core architecture [13]. In modern architecture, memory banks at different locations in a motherboard are directly attached to their corresponding CPUs, while multiple CPUs maintain cached data consistency by following cache coherent protocol. The accesses to a remote memory bank active inter-processor communication links and incur extra costs. Therefore, the access latencies from a specific CPU core to different memory banks are no longer same. From another aspect high speed interconnect, for example QuickPath Interconnect [13] and Hyper Transport [14],, helps a system achieve higher resource density and integration [15–17]. Although high-speed connectivity between CPUs greatly speeds up random memory access, an application that maximizes local memory accesses always outperforms than those that does not.

### 1.1.3 Limitations in Existing Solutions

Data-intensive applications often rely on data transfer services and place stringent requirements on the performance of the back-end storage systems and the

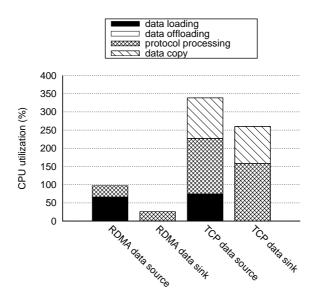

front-end network interfaces in modern multi-core servers. Existing data transfer software design and implementation heavily rely on operating systems abstraction and services [18]. They involve several data copies and trigger frequent interrupt services in processing networks packets. However, for transferring data at 100 Gbps and higher, existing solutions experience multiple bottlenecks along a full end-to-end path. For instance, existing TCP/IP based data transfer protocols and software contribute high CPU consumption due to excessive data copies; existing services of storage area networks are NUMA-agnostic and thus can not fully utilize the aggregate memory bandwidth of NUMA systems. As a result, existing software design and implementations often suffer scalability problems.

In storage systems, many existing applications intuitively achieve the best performance with a coarse-grained control policy by binding all related threads to a single NUMA node and allocating applications' memory to the local NUMA node via the numact1 command tool. However, two types of popular applications require a fine-grained, NUMA-aware design for scheduling threads and organizing memory: the first one are memory intensive applications (i.e., database engines) that require a large memory footprint distributed across different NUMA nodes to speed up aggregated performance; and the second type are storage service applications that rely on kernel cache utilities, i.e., page cache. Because the standard file interface, e.g., read and fread, does not provide any NUMArelated configuration parameter, the applications using the interface cannot explicitly manipulate kernel-level cached data on a designated NUMA node. For example, the existing iSCSI target software that is widely used to manage scalable storage blocks for enterprise databases and distributed file systems, has the property of these two types of applications: it requires a great amount of memory for serving cached data and relies on OS page cache that is agnostic to NUMA. Our research exploits an explicit and fine-grained NUMA-aware design to expedite its cache access.

# 1.2 Research Challenges and Research Goals

In this section, we elaborate challenges and research goals on achieving scalable data transfer systems.

### 1.2.1 Achieve Zero-Copy In An End-to-End Data Path

The stubborn speed disparity between the CPU and memory, named "Memory Wall", which is common in the previous single-core architecture, will continue to exist and even deteriorate with multi-core architecture. As detailed in [3], latency in memory access will be a major bottleneck in computer system. Pursuing high CPU clock rate is not sustainable due to the power wall problem, i.e., severe transistor current leakage under high clock rate leads to uncontrolled power consumption and generates excessive heat that is hard to dissipate. From the system architecture perspective, memory latency might partially negate the high CPU clock rate and the associated computing capacity. As a result, chip designers turn to exploring multi-core architectures and pack more cores into a single CPU die. Consequently, the speed imbalance between fast-growing number of CPU cores and memory will become more severe in the multi-core architecture.

Meanwhile, network performance is significantly improved by zero-copy and protocol offloading technologies such as remote direct memory access (RDMA). It enables network interface to transfer memory blocks in user space to the memory in remote hosts without CPU involvement. This is different from traditional TCP based solutions in which data are copied multiple times: applications copy data to kernel sending buffer, and then OS kernel copies the data again the lower layer of network stacks before reaching network interface cards. Memory bandwidth is not efficiently utilized in this scenario.

It's challenge to build a user-level communication protocols to bypass existing kernel communication support. Different from traditional data transfer

software, an efficient software design has to relies on zero-copy mechanism and restricts data plane from involving kernel space [19, 20]. On the other hand, the control plane of data transfer needs to optimize communication, and fully utilizes network bandwidth with a user-level communication management protocol, including multiple streams, memory credit management, and flow control. We will elaborate on decoupling control plane and data plane by using asynchronous software framework for data transfer software in Chapter 3.

### 1.2.2 Scale Zero-Copy Based Network Protocol In WANs

In addition to scale software performance in local area networks, we study the issues related to designing a scalable high-speed network protocol and improving application performance in wide area networks. When the bandwidth delay product is large, an application inevitably needs to manages a large mount of on-fly network packets and their related memory buffers: a zero-copy based solution can not recycle memory block until the data successfully reaches their destination. We focus on RDMA primitives, and investigate the interaction between application protocols/software and network hardware capabilities. An adaptive network mechanism is critical to improve both memory and network resource utilization.

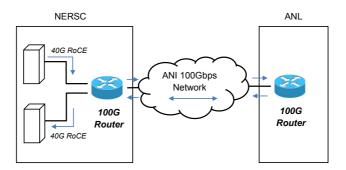

To extend the zero-copy mechanism in WAN, we design an application layer protocol for RDMA networks in Chapter 4, as part of a middleware layer that integrates network access, memory management, and multi-tasking. We address various issues in the RDMA implementation, such as buffer management, memory registration, and the parallelization of RDMA operations, all of which are vital to delivering the benefits of RDMA to applications. Using this protocol, we implemented an RDMA-based FTP software, RFTP [21–24]. This developmental work is funded by a larger project to exploit the full capacity of a 100Gbps network in the U.S. Department of Energy's Energy Sciences Network (ESnet).

### 1.2.3 Caching Locality in Large-Scale NUMA Systems

Storage system is another important aspect for data movement, and caching is widely used to improve the data accessing performance. Asymmetric memory architecture such as NUMA dominates enterprise and data center systems. It scales hardware memory capacity by connecting CPU and memory nodes with multiple lanes of high-speed processor interconnect. The asymmetrical performance on accessing different memory locations becomes notable as a single server integrates more CPU nodes with complicated interconnects [25]. Therefore, it's critical to improve data access locality in such highly integrated systems.

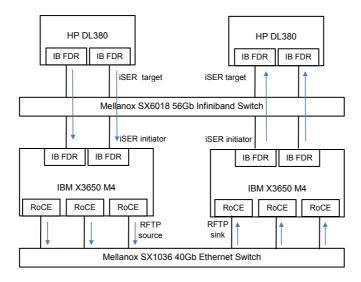

In Chapter 5, we will construct a storage area network (SAN) with the iSCSI and iSER protocols (iSCSI Extensions for RDMA) over InfiniBand based storage fabrics among which we utilize the Remote Direct Memory Access (RDMA) to move data blocks. The existing iSCSI software relies on the OS page cache which is NUMA-agnostic. We design a NUMA-aware cache at the userspace of iSCSI software to achieve better data locality, to eliminate the bottleneck effect of remote memory access and thereby to lead to high efficiency on serving cached data. The software product is tested rigorously and is demonstrated applicable to supporting various data-intensive applications and exascale supercomputers that constantly use powerful NUMA computers to serve iSCSI/iSER based storage.

### 1.2.4 Towards Scalable End-to-End Data I/O Systems

Our research goal is to design the end-to-end data I/O systems that can fully utilize state-of-the-art hardware advancements, and is scalable to the upcoming hardware evolutions. As shown in the previous section, existing solutions are not optimized to harness the new hardware features. Simply deploying existing solution in state-of-the-art hardware environment leads to waste resources and

incur unsatisfied user experience. This dissertation tackles the scalability problems in the network control path, the data transmission pipeline, and the storage caching layer. Particularly, Our research targets overcoming the aforementioned research challenge and implementing a real systems that can efficiently satisfy the end-to-end data I/O requirements in 100Gbps networks and beyond.

### 1.3 Dissertation Contributions

The main contributions of this dissertation are listed as follows:

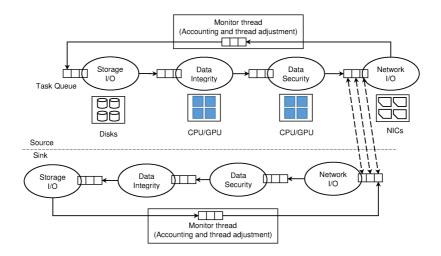

- Proposing asynchronous concurrent event-driven systems. We present a memory-centric software framework for high speed data movement. Based on this framework, we implement an integrated, multi-level, asynchronous processing model to unify the computing, storage, and networking operations and to maximize their performance. By using this processing model, we develop a data-driven, memory-centric, software architecture for data-intensive applications.

- Designing scalable RDMA-based data transfer protocol for wide area networks [21, 22, 24]. We design an application layer protocol [22] for RDMA networks, as a component of a middleware layer [21] that integrates network access, memory management, and multitasking. We address various issues that are related to the efficient implementation and implement a series of optimization methods, such as buffer management and memory registration, and the parallelization of RDMA operations, all of which are vital to delivering the benefits of RDMA to applications. Using this protocol, we implement an RDMA-based FTP software, RFTP. Our developmental work is a part of a large project in Department of Energy (DOE) to exploit the full capacity of a 100Gbps network in DOE's Energy Sciences Network (ESnet) [26]. Third, we also integrate TCP

zero-copy mechanism, sendfile and splice, to accommodate network environment without RDMA capability [24]. In addition, we show the importance of resource awareness, i.e., NUMA multi-core and parallel I/O capacity, in TCP based data transfer systems [27]. Fourth, we present our extensive experiments to evaluate the performance of our protocol, particularly over wide-area networks. We show that our tool has much higher performance compared with those existing widely used data transfer tools, such as GridFTP [28].

- Providing NUMA-aware caching for storage area networks [29]. We characterize the bottleneck of processing I/O requests [30] in the standard iSCSI/iSER software, and show the benefit of a NUMA-aware caching strategy. Second, we design and implement a NUMA-aware cache at the user level for the Linux SCSI target software and its iSCSI/iSER drivers. This cache module reduces remote memory access penalty, and improves throughput and latency of the target process. Its core design principles, including cache partitioning, node-affinity ranking, and request forwarding, are applicable to other memory-intensive applications. Third, to tackle the scalability problem on small I/O request processing, we propose a decentralized I/O event processing model for multi-core and NUMA systems. Fourth, we evaluate our solution on a 4-node NUMA testbed. Compared with the default Linux page cache, our user level NUMA-aware solution shows impressive performance gains with both synthetic and real-life workloads. Finally, this solution, initially developed as a enhancement to the backend block storage devices, ultimately provide performance improvements to front-end bulk data transfer applications (i.e., RFTP) and small I/O intensive applications (i.e., key-value stores).

- Optimizing the end-to-end data I/O performance [23]. We elaborate the design, tuning, and performance evaluation of a novel high-speed data

transfer system for delivering data at 100 Gbps in an end-to-end fashion. The system utilizes a pair of multi-core front-end hosts (sender and receiver). First, our back-end storage systems use the standard iSER protocol that is configured for high-speed data access. The protocol enables InfiniBand based data delivery from the back-end storage systems to the front-end hosts. This design allows us to eliminate the bottleneck in backend storage with scalable InfiniBand fabrics. Second, we integrate our RDMA-based file transfer protocol, RFTP [21,22,24], into the end-to-end data transfer system, to maximize bandwidth throughput and to minimize the host processing overhead. Third, we perform a thorough NUMA tuning to optimize the performance for all hosts along an end-to-end path, and to minimize the impact of host processing overhead. We note in the current implementation of iSER or RFTP, the NUMA factor is not considered. We present the observed performance benefit of simple NUMA tuning in this chapter. Our design is the first one to achieve 100 Gbps endto-end real data file transfers between one pair of commodity hosts. We evaluate our system comprehensively by designing the testbed to closely resemble the production environments that are common in large national laboratories and commercial cloud computing providers. Furthermore, we perform inter-data center data transfer tests along the long-haul high bandwidth paths of over 4000 miles long and confirm our protocol and tool clearly outperform the alternative design and implementations.

### 1.4 Dissertation Overview

Figure 1-2 shows the problems that each chapter tries to tackle and their scopes and locations with respect to a real-world cloud computing environment. The rest of the dissertation is organized as follows. Chapter 2 elaborates the concepts that are related to this dissertation. Chapter 3 proposes asynchronous

Figure 1-2: Dissertation overview.

staged software design, followed by RDMA-based zero-copy network protocol for WAN in Chapter 4. Chapter 5 presents design and implementation of NUMA-aware cache for improving iSCSI servers performance. Chapter 6 elaborates system optimization methods along an end-to-end data movement path. We summarize related research in Chapter 7 and offer our conclusion in Chapter 8.

# Chapter 2

# **Background**

This chapter provides a background of various aspects that are integral components of this dissertation. First, we provide a background on RDMA and high performance networks, e.g. RDMA semantics and memory registration in programming with RDMA networks. We then describe the asynchronous programming models and libraries for network I/O and storage I/O. We also discuss the NUMA architecture and the libraries and utilities of constructing NUMA-aware applications. Finally, we discuss the caching layer in iSCSI system and the necessity to design a NUMA-aware caching system for iSCSI protocol.

# 2.1 RDMA and Zero-Copy Techniques

Traditional TCP/IP applications involve multiple data copies. As shown in Fig. 2-1, sender copies data from user space memory to kernel space. It consumes a large amount of CPU resource and involves multiple context switches. Then, the sender's network card driver fetches data from kernel space by DMA operations and sends data packets into communication links. On the receiver end, NIC driver interrupts kernel service and places the packet into kernel TCP socket buffer. Thereafter, the kernel copies data into user space and interrupts the receiving application for data arrival.

Figure 2-1: Data path of TCP/IP applications.

RDMA, remote direct memory access, is introduced to eliminate data copy overhead in high performance networks. It moves data from source host memory to a remote host memory with kernel-bypass and zero-copy operations. Before a communication party starts RDMA operations, both sides perform memory registration, as shown in Fig. 2-2. Here to register a *memory region* means to pin a designated chunk of memory into physical RAM and prevent it from being swapped out by OS. The application uses <code>ibv\_reg\_mr()</code> to specify the memory space to be pinned, which in turn uses the system API and the corresponding function <code>mlock()</code> to register the memory region in the physical main memory space. In addition, applications can use the interface to setup desired memory protection attributes. The registered memory information is also stored in a page table of the RDMA network interface that manages and controls direct data accesses into/from the registered memory.

RDMA write is one of the zero-copy operation that bypasses kernel space. Once getting an RDMA write *work request* from an application, the RDMA NIC (RNIC), also known as host channel adapter (HCA), uses DMA operations to fetch data from user space memory directly without kernel involvement. The work request contains the information of the local source memory and the remote destination memory. At the remote side, its RNIC contains the page table for the target region. Upon data arrival, the RNIC of the remote side adds the

Figure 2-2: Data path of RDMA applications.

Figure 2-3: Mellanox ConnectX supports both RDMA over InfiniBand and RDMA over Converged Ethernet (RoCE) devices.

target offset, obtains the corresponding physical pages, write data to the user space memory directly without kernel involvement. RDMA read operation is used for retrieve remote memory information bypassing kernel involvement on both local and remote sides' OS kernel, and its data movement path is opposite to the RDMA write's.

RDMA is designed to be scalable to bundle multiple links (channels) to increase the communication bandwidth. The last three generations of RDMA device support either InfiniBand, Internet, or RDMA over converged Ethernet (RoCE), and achieve 40 Gbps (QDR: quad data rate), 56 Gbps (FDR: fourteen data rate), and 100 Gbps (EDR: enhanced data rate). Figure 2-3 shows a family of InfiniBand and RoCE devices from Mellanox Technology.

In summary, RDMA coordinates hardware and applications to eliminate data copies and to accelerate network processing with hardware support. It achieves

low latency and high throughput comparing to the traditional TCP/IP network stack. We explore the RDMA semantics, remote memory operations and programming interfaces in the following section.

#### 2.1.1 RDMA Semantics and Performance Analysis

RDMA offers two types of message transfer semantics: Channel and Memory. The former, "send/receive", that is also referred as two-sided operation, involves the OS network kernel for the completion event notification at both the source and sink hosts of data transfer once a network connection is established [31]. The communication channel between source and sink is modeled as queue pair (QP). Each QP consists of a sender queue and a receiver queue, whilst each queue represents one end of the channel. Before an application uses RDMA to transfer data, the receiver posts a work request to the receiver queue. Thereafter the sender posts a work request to the sender queue. Both the sender and receiver will get a completion event after the data transfer completes. On the other hand, the memory semantics of RDMA, "read/write mode", is often termed "one-sided operation". With this type of RDMA, the receiver advertises its available registered memory to the sender, including the address and other information about the memory region, so that the sender can directly use RDMA write to write a chunk of data into the specified memory location at the receiver host.

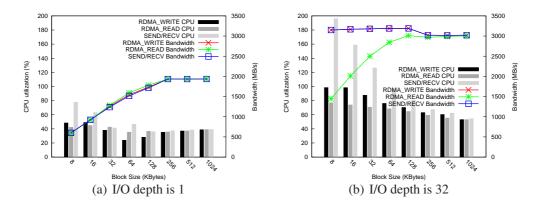

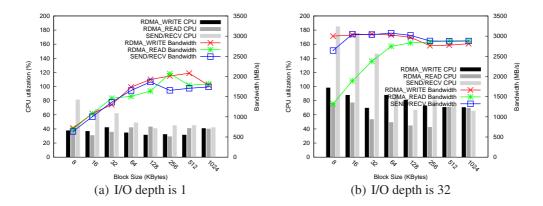

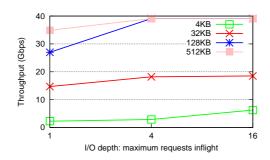

To decide which type of RDMA semantics to choose to move bulk data, we consider various performance factors. We design an RDMA I/O engine for the fio benchmark and stress test tool [32] that offers flexible parameter settings and excellent capabilities to report the performance statistics of both synchronous and asynchronous I/Os. Compared with the standard OFED (OpenFabrics Enterprise Distribution) benchmark tools, our approach is easier to collect comprehensive performance statistics from the I/O module, including CPU usage, I/O latency, bandwidth, and I/O performance distribution. The RDMA engine

Figure 2-4: RDMA semantics performance evaluation in the RoCE Environment.

Figure 2-5: RDMA semantics performance evaluation in the InfiniBand Environment.

uses asynchronous I/O and allows our test program to simultaneously post multiple I/O requests. We conducted a comprehensive set of test cases with varying block sizes and maximum number of concurrent blocks in flight (also called I/O depths) for the two types of RDMA semantics.

Figure 2-4(a) and Figure 2-5(a) show that with a small I/O depth, RDMA WRITE, RDMA READ and SEND/RECEIVE exhibit similar performance, while the CPU consumption of SEND/RECEIVE is much higher than that of the others. The high CPU consumption reflects the fact that SEND/RECEIVE involves both the data source and sink during transfer, and the sink must process the same number of RDMA events as the source. However, RDMA READ/WRITE only

handles RDMA events at one end. A high I/O depth improves bandwidth performance as depicted in Figure 2-4(b) and Figure 2-5(b). To improve RDMA performance, an application must post multiple I/O tasks in flight to fully take advantage of OFED's asynchronous programming interface. We made several observations from these experiments: 1) RDMA WRITE and SEND/RECEIVE perform better than RDMA READ; 2) all test cases set block size in the range from 16KB to 128KB to achieve the best bandwidth; 3) performance saturates when the block size is bigger than 128KB; 4) CPU usage decreases when the block size increases because of fewer interrupts; and 5) during their peak performance, the CPU usage of SEND/RECEIVE is higher than that of RDMA WRITE.

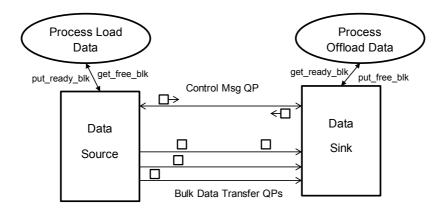

Since the arrival rate of incoming data is unpredictable, the data sink must post sufficient registered buffers at the receive queue in advance before the data source sends data. Otherwise, the data source may encounter the error of Receiver Not Ready (RNR). The error will pause the source, and lead to low performance and under-utilized network resource. Tian et. al. proposed to introduce a control message mechanism to avoid the RNR error in their protocol implementation [33], where the source must wait for credits to be piggybacked with the message from the data sink before the source further posts more tasks into the send queue. In summary, RDMA WRITE performs the best with the least CPU consumption in all test cases, and I/O depth should be set to a relatively large number, as identified in the previous testing results. Therefore, we designed a hybrid data transfer protocol that exchanges control messages via SEND/RECEIVE, and transfers bulk data via RDMA WRITE.

#### 2.1.2 OS Kernel Zero-Copy Techniques

In addition to the RDMA hardware-based zero-copy acceleration, software based optimization is another approach to reduce data copies and the associated pro-

cessing overheads, for example the system calls sendfile() and splice(), newly supported by modern operating system kernels. In contrasting to TCP/IP stack that involves multiple data copies and incurs high CPU load in the high speed data transfer environment, the sendfile() primitive in Linux performs pass-by-reference to copy data between one file descriptor and another, e.g., between a disk file descriptor and a socket descriptor. Because this type of copying occurs within the kernel and merely exchanges data reference pointers, sendfile() is more efficient than the combination of the standard POSIX read and write functions which require physical data copies to and from the user space.

splice further extends the functionality of sendfile(). It is a Linux-specific system call that moves data between a file descriptor and a pipe without a detour to user space. splice() requires to setup a pipe buffer prior to the function call. A pipe buffer is an in-kernel memory buffer and transparent to user space processes. A user process can splice the content of a source file, e.g., a socket, into this pipe buffer, then splice the pipe buffer into the destination file descriptor, e.g., a file in the disk systems.

# 2.2 Asynchronous High Throughput Computing and Thread-based Concurrency

General asynchronous I/O model separates I/O issuing and I/O status checking to avoid blocking operations. It can be utilized to overlap computing and I/O resources efficiently. Inspired by the RDMA based asynchronous communication model, we extend it to be a generalized asynchronous computing model and apply it to many other aspects of an end-to-end high throughput data path. A typical OS interacts with heterogeneous devices and handles various system calls via hardware/software interrupts (events) asynchronously, while providing

a simple uniform POSIX interface to applications. Thus, the manner the software handles asynchrony is fundamental to the performance of applications and their hosting server in high throughput computing.

Newly developed multi-core processor technology is capable of packing dozens of CPU cores in a single server, and therefore it is cost-effective to fully utilize these resources first within the server before reaching out to other servers for high-throughput computing. A simple approach is to maximize the concurrency of a server via a multi-threaded parallel programming model, wherein a master program is responsible for partitioning a large task into smaller ones and assigning each one of them to a different, dynamically created thread to parallelize and expedite processing. Here, the master program often relies on complex inter-thread synchronization schemes to synchronize thread status and ensure task completion. For example, OpenMP [34] uses the lock and barrier primitives. The slowest thread always dominates the overall execution pace and performance of an application that is implemented with this model. Given the uncertainty of server system status, non-uniform memory access, and processing loads, it is possible that several threads may hold CPU cores and wait idle for the slowest thread to complete. Thereby, this parallel model does not guarantee the optimal server performance.

On the other hand, asynchronous computation proceeds via triggering events and acting upon them instead of being directly orchestrated by a central master program. Within the asynchronous computing paradigm, a set of threads that entail a sequence of data processing instructions are created apriori and bound to all available cores to reduce context switches and to minimize overheads. A thread, along with its associated instructions and one allocated CPU core, forms a unit of computing resource, and is made available to the main application via event exchanges.

Even when an application involves multiple threads, some of them engage in the synchronous parallel paradigm (for example, wait for and respond to user requests) and some of them perform asynchronous computing, an asynchronous computing thread executes at its own rate without affecting the aggregate performance, and remains in a background mode with regard to the master program running in the foreground. No explicit join step is required once an asynchronous thread completes its current data processing assignment. Instead, it will proactively check for the next event to get more task assignments.

In the context of our work, a high throughput computing program often loads initial input data from internal and/or external storage and high speed network adapters, applies a series of transformations to data, and writes output back to storage media and/or network stacks. There is less inter-dependency between two threads assigned to different datasets or segments of memory. To avoid excessive data copies and relocations, we adopt a data-and-memory-centric computing paradigm: an end-to-end high throughput program is regarded as a series of operations that are applied to memory-resident data: storage I/O to populate and evacuate memory space, data transformations (for example, compression/decompression, encryption/decryption, Fourier Transformation and its inverse), and network I/O to import and export memory space. These operations interact with a main program asynchronously and apply changes to shared memory space even though their nature, duration, and internal implementation are heterogeneous.

#### 2.2.1 RDMA Asynchronous Programming Model

The RDMA architecture permits an application to access hardware directly in the user mode. RDMA provides a set of verbs (function calls) that customizes and optimizes the RDMA-aware network interface cards. All I/O operations involved in RDMA programming are asynchronous: an application posts an I/O request into hardware, and then polls a corresponding completion event to confirm the outcome of the I/O, either success or failure with a particular cause.

To perform RDMA operations, an application must establish connections between local and remote host. The Queue Pair (QP) in the RDMA programming plays an equivalent role as the socket interface to TCP/IP stack. The QP needs to be setup and initialized on both sides of connection. An application uses Verbs to interact with Communication Manager (CM) which subsequently exchanges the information about the QP and sets up the QP. Once a QP is established, application calls the verbs API to perform one-sided RDMA reads, RDMA writes, and other atomic operations. Applications can also perform serialized two-sided send/receive operations which are similar to the socket send()/recv().

#### 2.2.2 Asynchronous Storage I/O

Asynchronous I/O functions enables applications to saturate the storage I/O performance with a single thread by submitting a batch of concurrent I/O requests to the disk queues. There are two types of asynchronous I/O interfaces: *POSIX AIO* and *Linux native AIO - libaio* [35]. These two implementations are fundamentally different: the POSIX AIO creates multiple threads within OS, each of which performs normal synchronous and blocking I/O. Essentially it wraps synchronous I/O functions with multiple threads to emulate the behavior of asynchronous I/Os. On the other side, libaio is truly asynchronous, and directly supported by the OS kernel which internally queues I/O requests and submits to devices in an optimized manner. We choose libaio for our implementation method in the following chapters.

#### 2.3 NUMA Architecture

In a state-of-the-art NUMA system, A CPU die, along with its memory controller and local memory banks, comprises a *NUMA node*. A NUMA node references its directly attached memory banks as *local memory* and those at-

tached to other CPU dies as *remote memory*. Multiple NUMA nodes in a host are connected by high-bandwidth and low-latency interconnects, such as Intel QuickPath [13] and AMD HyperTransport [14]. Due to the traffic contention on memory controllers and interconnects, remote memory accesses cause longer access latency and lower throughput compared to local accesses [36].

#### 2.3.1 SMP and NUMA Architecture

In multi-core era, symmetric multiprocessing (SMP) was first introduces to increase a single server's processing capacity. It connects two or more identical processors to a single, shared main memory by using a shared system bus. However, connecting processors with a shared system bus suffers the scalability problem when the number of processors increases because of the contention for the shared bus resource. Modern servers typically adopt the NUMA architecture and use dedicated CPU interconnects instead to scale memory system performance.

#### 2.3.2 Asymmetric Memory Layout

Because interconnect topologies in NUMA system can be 2-D torus or even 3-D torus, the distance or the number of "hops" in NUMA system between the CPU which runs an application and the memory location where the application's data resides varies and leads to different performance behavior in terms of latency and bandwidth. On one hand, this asymmetric memory layout further enlarges the performance disparity among the memory accesses by different CPU cores. On the other hand, because of the shared memory architecture, all processors enforce the cache coherence policy to simplify application-level development. NUMA-agnostic applications incur remote memory access penalty and unstable performance. Therefore, applications has to be tuned accordingly to gain better performance in NUMA systems.

## 2.4 iSCSI/iSER and Storage Caching System

This section presents the research problems and efforts on cache performance in iSCSI/iSER systems.

#### 2.4.1 iSCSI and iSER

The Internet Small Computer System Interface (iSCSI) is an IP-based approach to build storage area networks. It supports storage virtualization over local area networks (LANs) and even wide area networks (WANs) by encapsulating SCSI commands and payload within IP packets, which are exchanged between clients (*initiators*) and SCSI storage devices (*targets*). Ko *et al.* proposed a standard extension of iSCSI for RDMA networks, named iSER [37]. The Linux SCSI target framework [38, 39] is the de facto iSCSI target software supporting various target drivers, such as the iSCSI driver for TCP/IP, the iSER driver for RDMA [40], and several vendor specific drivers (e.g. IBM, QLogic, LSI). We design and implement a cache module in user space for this framework, and provide the same interface for all transport drivers to interoperate with the cache module.

#### 2.4.2 Caching Layer in iSCSI/iSER

Several caching mechanisms have been investigated and developed to improve the overall performance of the iSCSI system. He *et al.* proposed a strategy of combining non-volatile RAM and log disk to cache iSCSI traffic in initiators [41]. For a shared target server, however, synchronizing cache status among multiple initiators incurs a significant cost. Wang *et al.* proposed an on-board cache in a network interface card. Given a NIC cache hit, cached data does not need to traverse the host's PCI bus and memory controllers. A "Helper" cache in an iSCSI target server has advantages over the on-board one as it eliminates the limitation to cache size [42].

From a system perspective, storage area networks consists of a three-tier memory cache hierarchy, including application client cache, file or database server cache, and storage server cache, and cache layer often duplicates a fraction of the content already cached by another. To convert the inclusive cache hierarchy with duplications to the exclusive one, researchers have proposed hierarchy-aware caching, which maintains the existing I/O interface and is transparent to the application client, and aggressively-collaborative caching, which requires centralized cache management by the application client. For hierarchyaware caching, an eviction-based placement policy [43] and Multi-Queue (MQ) algorithm [44] reduce network traffic and improve the cache hit rate at storage servers. For aggressively-collaborative caching, Wong and Wilkes proposed a "DEMOTE" operation to evict the content from the frontend and re-cache it into the backend storage server to ensure exclusive caching [45]. Chen et al. found that the aggressively-collaborative caching provides a mere 1.0% improvement over hierarchy-aware caching for most workloads and cache configurations in their real system experiments [46].

# 2.5 Summary

In this section, we introduce RDMA networks and the NUMA architecture. We also provide necessary background knowledge on the state-of-the-art research works on the RDMA programming model, storage area networks, and the caching layer in the iSCSI and iSER systems.

# **Chapter 3**

# **ACES Software Architecture**

Asynchronous storage I/O and communication exhibit advantages over their synchronous counterparts and can achieve bare-metal performance. Various types of asynchronous processing (computing, storage, and networking), however, have never been considered holistically in today's high throughput computing, and therefore their advantages and flexibility have never been shown to cope with big data processing. In this chapter, we present a memory-centric software framework for high-throughput data transfer applications, called asynchronous concurrent event-driven system (ACES).

# 3.1 Introduction

Scientific and industry applications are generating increasingly large amounts of data, often referred to as "big data". Effective analysis and accurate inference from these data towards knowledge discovery require high-throughput data processing, transforming, transporting, and sharing among data management/analytics specialists and application-domain scientists. A deluge of parallel and distributed programming paradigms have been proposed to address this "big data issues": Google MapReduce [47] and its open source Hadoop [48], Grid Computing [49], and cluster computing [50]. All these paradigms parti-

| Hardware | Hardware Advances       | Software Policy          |

|----------|-------------------------|--------------------------|

| Network  | RDMA, TCP offloading    | asynchronous I/O         |

|          |                         | event-driven             |

| Disk     | SSD, TCQ, NCQ           | asynchronous I/O         |

|          |                         | event-driven             |

| Memory   | NUMA, memory wall       | zero-copy                |

| CPU      | Multicore               | thread-based concurrency |

|          | Encryption acceleration |                          |

Table 3.1: Software policies for each part of hardware advances

tion data and dispatch data processing tasks into a large number of computer servers for an aggregated high-throughput computing (HTC) performance.

The steady progress of VLSI technology continues adding more cores, higher network bandwidth, and faster storage into a single commodity server than before. These technology breakthroughs afford rethinking the existing computing models for a single Linux server to meet the performance, energy, and efficiency requirements of various HTC applications. Meanwhile, technological trends indicated that hardware throughput/bandwidth continues to be the biggest winner, and outpaces other performance components (for example, latency) with individual servers and computing facilities [51]. In the network and storage fields, disruptive innovations, such as CPU bypass Remote Direct Memory Access (RDMA) and semiconductor flash drives, have improved the throughput of I/O facilities by two to three orders of magnitude. Single host computation density and capacity are continuously improved by multi-/many-core technologies. In contrast, the speed of main memory is relatively slow and memory controller is generally the bottleneck in symmetric multiprocessing (SMP). This led to the popularity of Non-Uniform Memory Architecture (NUMA), which obtains a good aggregate memory performance, but complicates application tuning of memory accesses cross the asymmetric layout. Given the expensive memory copy operations within the NUMA servers, zero-copy primitives (such as direct I/O in storage and RDMA in network) becomes more attractive in application

design and implementation. Furthermore, high performance hardware becomes competitive in term of price and can be economically added into a commodity servers [52]. Given these trends, it is important that we understand how to leverage the advantages of these hardware advances to build high throughput applications.

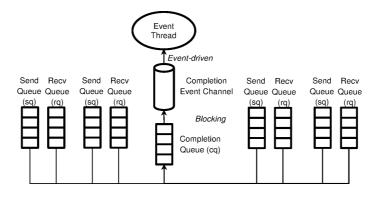

Unfortunately, existing software design in high-throughput computing cannot survive rapid changes in computer technology. In terms of data transfer which has stringent requirements on throughput, existing solutions emphasize and satisfy a fraction of user demands by a unified design philosophy. For example, OpenSSH scp/sftp [53] concentrates user requirements on security and believes in clean and simple code. It heavily relies on traditional operating system facilities such as pipe, fork(), synchronous I/O to maintain its simple design choice. GridFTP, a popular data transfer tool in grid computing, focuses on TCP throughput optimization and makes use of an event-driven software architecture to manage numerous concurrent TCP connections [28]. However, with the increase of hardware bare-metal throughput, no single design philosophy and methodology is currently able to take full advantage of the range of hardware advances. As shown in table 3.1, a hybrid software design policy is required to extract the best performance from each part of a computing system.