## **Stony Brook University**

# OFFICIAL COPY

The official electronic file of this thesis or dissertation is maintained by the University Libraries on behalf of The Graduate School at Stony Brook University.

© All Rights Reserved by Author.

#### **Automatic Synthesis of Instruction Set Semantics and its Applications**

A Dissertation presented

by

Niranjan Sudhir Hasabnis

to

The Graduate School

in Partial Fulfillment of the

Requirements

for the Degree of

**Doctor of Philosophy**

in

**Computer Science**

Stony Brook University

**August 2015**

Copyright by Niranjan Sudhir Hasabnis 2015

#### **Stony Brook University**

The Graduate School

Niranjan Sudhir Hasabnis

We, the dissertation committee for the above candidate for the Doctor of Philosophy degree, hereby recommend acceptance of this dissertation

Dr. R. Sekar - Dissertation Advisor Professor, Computer Science

Dr. Mike Ferdman - Chairperson of Defense Assistant Professor, Computer Science

**Dr. Michalis Polychronakis Assistant Professor, Computer Science**

Dr. Suresh Srinivas Principal Engineer, Intel Corporation

This dissertation is accepted by the Graduate School

Charles Taber

Dean of the Graduate School

#### Abstract of the Dissertation

#### **Automatic Synthesis of Instruction Set Semantics and its Applications**

by

#### Niranjan Sudhir Hasabnis

**Doctor of Philosophy**

in

#### **Computer Science**

Stony Brook University

#### 2015

Binary analysis, translation and instrumentation tools play an important role in software security. To support binaries for different processors, it is necessary to incorporate the semantics of every processor's instruction set into the tool. Unfortunately, the complexity of modern instruction sets makes the common approach of manual semantics modeling cumbersome and error-prone. Furthermore, it limits the number of processors as well as the fraction of the instruction set that is supported.

In this dissertation, we propose novel architecture-neutral techniques for automatically synthesizing the semantics of instruction sets. Our approach relies on the observation that modern compilers such as GCC and LLVM already contain detailed knowledge about the semantics of many instruction sets. We therefore develop two techniques for extracting this knowledge. Our first technique relies on a learning process: observing examples of translation between a compiler's architecture-neutral internal representation and machine instructions, and inferring the mapping from these examples. We then develop a second (and complementary) method that develops symbolic execution techniques to extract this mapping from the code generator source. Unlike previous symbolic execution systems that specialize in generating a single solution to a set of constraints, our problem requires a compact representation of all possible solutions. We describe the development of such a system, based on source-to-source transformation of C-code and a runtime system that is implemented in C and Prolog with a finite-domain constraint solver (CLP-FD).

To demonstrate the applicability of synthesized instruction-set semantics, we develop two applications. In the first application, we use synthesized semantics to test correctness of code generators. Specifically, we develop a new testing approach that generates and executes test cases based on the derived semantic model for each instruction. We uncovered nontrivial bugs in the GCC code generator using this technique. As a second application, we have used these models to lift binaries for x86, ARM and AVR (used in Arduino and other microcontroller) architectures to intermediate code, which can then be analyzed or instrumented in an architecture-independent manner.

#### Dedicated to,

Aai, Baba, and Nilesh (my parents and my brother) Without their support I would not have started this journey.

&

Anuja (my wife and love of my life) Without her support I would not have been able to complete it.

#### **Table of Contents**

### **Contents**

| 1      | INT            | Introduction                                                  |                                                       |    |  |

|--------|----------------|---------------------------------------------------------------|-------------------------------------------------------|----|--|

|        | 1.1            | Overv                                                         | iew of Approaches and Dissertation Organization       | 2  |  |

|        | 1.2            | High-l                                                        | Level Overview of Contributions                       | 5  |  |

| 2      | OVI            | OVERVIEW OF APPROACHES FOR AUTOMATIC SYNTHESIS OF INSTRUCTION |                                                       |    |  |

|        | SET SEMANTICS  |                                                               |                                                       |    |  |

|        | 2.1            | Level                                                         | of Abstractions Required In the Extracted Semantics   | 7  |  |

|        | 2.2            | Possib                                                        | le Approaches                                         | 9  |  |

|        |                | 2.2.1                                                         | Extraction from instruction-set manuals               | 10 |  |

|        |                | 2.2.2                                                         | Extraction from the hardware                          | 10 |  |

|        |                | 2.2.3                                                         | Extraction by exhaustive testing of CPU               | 11 |  |

|        |                | 2.2.4                                                         | Extraction by symbolic execution of CPU specification | 12 |  |

|        | 2.3            | Our A                                                         | pproach                                               | 13 |  |

|        |                | 2.3.1                                                         | Background on code generation in modern compilers     | 15 |  |

|        |                | 2.3.2                                                         | Possible challenges for our approaches                | 18 |  |

|        |                | 2.3.3                                                         | Approach details                                      | 19 |  |

| 2.4 Su |                | Summ                                                          | ary                                                   | 20 |  |

| 3      | LIS            | LISC: LEARNING INSTRUCTION SEMANTICS FROM CODE GENERATORS 21  |                                                       |    |  |

|        | 3.1            | LISC (                                                        | Overall Approach                                      | 24 |  |

|        | 3.2            |                                                               |                                                       |    |  |

|        | 3.3            | Parameterization                                              |                                                       |    |  |

|        | 3.4            |                                                               |                                                       | 31 |  |

|        |                | 3.4.1                                                         | Background                                            | 34 |  |

|        |                | 3.4.2                                                         | Maximal common prefix (mcp)                           | 36 |  |

|        |                | 3.4.3                                                         | Residue                                               | 37 |  |

|        |                | 3.4.4                                                         | Discriminating tests                                  | 40 |  |

|        |                | 3.4.5                                                         | Algorithm for constructing automaton                  | 42 |  |

|        |                | 3.4.6                                                         | Error detection                                       | 44 |  |

|        | 3.5            | Implei                                                        | mentation                                             | 44 |  |

|        | 3.6 Evaluation |                                                               | ntion                                                 | 47 |  |

|        |                | 3.6.1                                                         | Completeness of the model                             | 47 |  |

|        |                | 3.6.2                                                         | Soundness                                             | 54 |  |

|        |                | 3.6.3                                                         | Compiler independence                                 | 58 |  |

|        |                | 3.6.4                                                         | Sizes of the models and performance of LISC           | 59 |  |

|        | 3.7            | *                                                             |                                                       | 61 |  |

|        |                | 3.7.1                                                         | Relation to machine learning                          | 61 |  |

|        |                | 372                                                           |                                                       | 63 |  |

|                |      | 3.7.3    | Finite state transducers and grammatical inference                   | . 68  |

|----------------|------|----------|----------------------------------------------------------------------|-------|

|                |      | 3.7.4    | Learning using assemblers and compilers                              | 69    |

|                | 3.8  | Summa    | ury                                                                  | . 71  |

| 4              | EISS | SEC: EXT | FRACTING INSTRUCTION SEMANTICS BY SYMBOLIC EXECUTIO                  | N     |

|                | OF ( | CODE GI  | ENERATORS                                                            | 72    |

|                | 4.1  | Backgr   | ound: Symbolic Execution                                             | . 74  |

|                |      | 4.1.1    | A simple code generator and its symbolic execution                   | . 75  |

|                |      | 4.1.2    | Concolic execution of the simple code generator                      | . 79  |

|                | 4.2  | Design   |                                                                      |       |

|                |      | 4.2.1    | Input program                                                        |       |

|                |      | 4.2.2    | Overall flow                                                         | . 82  |

|                |      | 4.2.3    | Source-to-source transformation for concolic execution               | . 83  |

|                |      | 4.2.4    | C language features and challenges for EISSEC                        | . 94  |

|                | 4.3  | Implem   | nentation                                                            | . 98  |

|                |      | 4.3.1    | Source-to-source transformation                                      | . 98  |

|                |      | 4.3.2    | Dynamic single assignment                                            | . 98  |

|                |      | 4.3.3    | Undo records                                                         | . 99  |

|                |      | 4.3.4    | Constraint solver                                                    | 103   |

|                | 4.4  | Optimi   | zations                                                              | 104   |

|                |      | 4.4.1    | Using range and set constraints                                      | 106   |

|                |      | 4.4.2    | Strength reduction                                                   | 107   |

|                |      | 4.4.3    | Exploiting hardware-level parallelism                                | 107   |

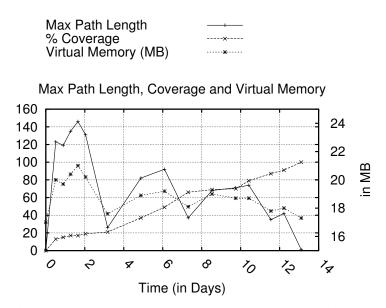

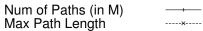

| 4.5 Evaluation |      | tion     | 108                                                                  |       |

|                |      | 4.5.1    | Model extraction performance                                         | 109   |

|                |      | 4.5.2    | Soundness, completeness, and model size                              | . 118 |

|                |      | 4.5.3    | Model extraction for AVR                                             | . 120 |

|                | 4.6  | Related  | l Work                                                               | . 122 |

|                |      | 4.6.1    | Path explosion problem                                               |       |

|                |      | 4.6.2    | Constraint solver inefficiencies                                     |       |

|                |      | 4.6.3    | Symbolic execution for function extraction                           |       |

|                | 4.7  | Summa    | ary                                                                  | 126   |

| 5              | ArCh |          | HECKING CORRECTNESS OF EXTRACTED SEMANTICS MODELS                    |       |

|                | 5.1  |          | s and Inconsistencies                                                |       |

|                |      | 5.1.1    | Types of inconsistencies in semantic models                          |       |

|                |      | 5.1.2    | How to detect inconsistencies in semantic models                     |       |

|                |      | 5.1.3    | Detecting inconsistencies in compilers' semantic models              |       |

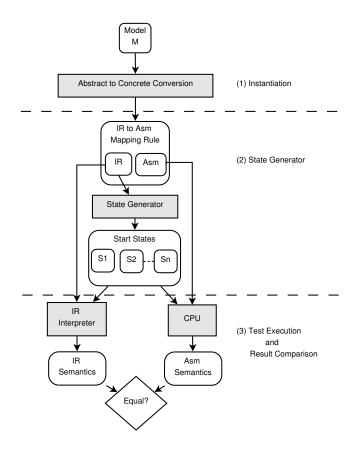

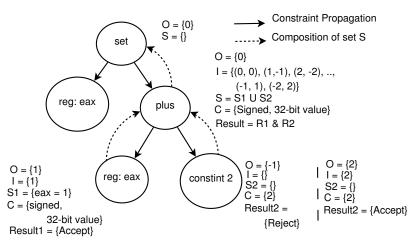

|                | 5.2  |          | pproach                                                              |       |

|                |      | 5.2.1    | Start state generation                                               | . 139 |

|                |      | 5.2.2    | Obtaining "interesting" test inputs: constraint generation, propaga- |       |

|                |      |          | tion and solving                                                     | 141   |

|   |                            | 5.2.3   | Test execution and result comparison                 |  | 144 |

|---|----------------------------|---------|------------------------------------------------------|--|-----|

|   | 5.3                        | Implen  | nentation                                            |  | 146 |

|   |                            | 5.3.1   | Obtaining concrete rules from abstract mapping rules |  | 146 |

|   |                            | 5.3.2   | Obtaining start states for a mapping rule            |  | 146 |

|   |                            | 5.3.3   | Obtaining RTL semantics                              |  | 147 |

|   |                            | 5.3.4   | Obtaining assembly semantics                         |  | 147 |

|   |                            | 5.3.5   | Handling memory                                      |  | 149 |

|   |                            | 5.3.6   | Test execution and result comparison                 |  | 150 |

|   | 5.4                        | Evalua  | tion                                                 |  | 150 |

|   |                            | 5.4.1   | Detecting known soundness issues                     |  | 155 |

|   | 5.5                        | Related | d Work                                               |  | 157 |

|   | 5.6                        | Summa   | ary                                                  |  | 159 |

|   | Рит                        | LDING   | ASSEMBLY-TO-IR TRANSLATORS AUTOMATICALLY             |  | 160 |

| 6 |                            |         |                                                      |  |     |

|   | 6.1                        | _       | opproach to Assembly to IR Translation               |  |     |

|   |                            | 6.1.1   | Challenge                                            |  |     |

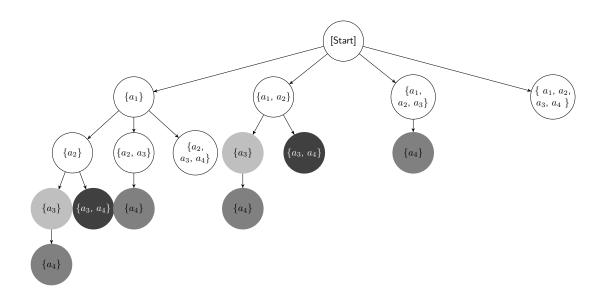

|   |                            | 6.1.2   | Algorithm                                            |  |     |

|   |                            | 6.1.3   | Other challenges for Assembly to IR translation      |  |     |

|   | 6.2                        | -       | nentation                                            |  |     |

|   | 6.3                        | Evalua  | tion                                                 |  | 171 |

|   | 6.4                        | Related | d Work                                               |  | 172 |

|   | 6.5                        | Summa   | ary                                                  |  | 173 |

| 7 | CONCLUSION AND FUTURE WORK |         |                                                      |  |     |

|   | 7.1                        | Future  | Work                                                 |  | 175 |

|   |                            |         |                                                      |  |     |

| R | EFER:                      | ENCES   |                                                      |  | 177 |

#### **List of Figures**

## **List of Figures**

| 1  | Semantics of x86 add instruction taken from Intel manual                | 9   |

|----|-------------------------------------------------------------------------|-----|

| 2  | Key steps in GCC's translation of a source program                      | 16  |

| 3  | An MD entry for x86 div instruction                                     | 17  |

| 4  | Sample compilation log produced by GCC's x86 code generator during      |     |

|    | compilation of fibonacci's C code                                       | 21  |

| 5  | Concrete pair for x86 add assembly instruction and its parameterized    |     |

|    | version                                                                 | 24  |

| 6  | LISC block diagram                                                      | 25  |

| 7  | Grammar for concrete and parameterized pairs                            | 28  |

| 8  | Examples of concrete and parameterized pairs for a subset of x86        | 29  |

| 9  | Pseudo code for identifying mapping functions between values of input   |     |

|    | and output parameters                                                   | 32  |

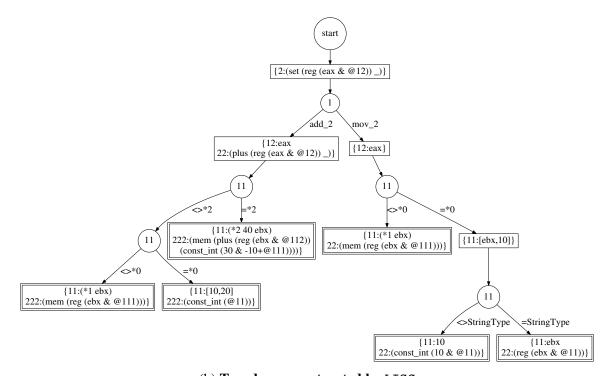

| 10 | A tree transducer for the example                                       |     |

| 11 | Lattice over a set of parameterized x86 assembly instructions           | 37  |

| 12 | An algorithm for constructing automaton                                 | 42  |

| 13 | Example of transducer construction by LISC                              | 45  |

| 14 | Breakdown of LISC implementation effort                                 | 46  |

| 15 | Detailed completeness evaluation results for x86                        | 49  |

| 16 | Detailed completeness evaluation results for ARM                        | 53  |

| 17 | Completeness results of LLVM compiled binaries for x86                  | 59  |

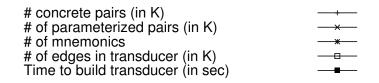

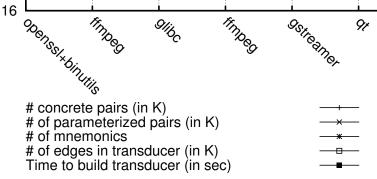

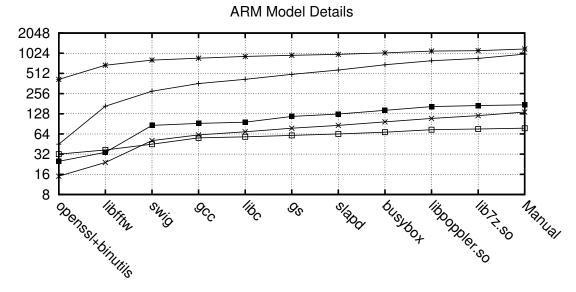

| 18 | Extracted model details                                                 | 60  |

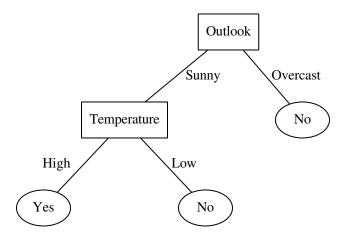

| 19 | Decision tree for decision to play tennis based on weather data         | 64  |

| 20 | Instruction set and mapping table for a simple code generator           | 76  |

| 21 | OCaml code for a simple code generator                                  | 77  |

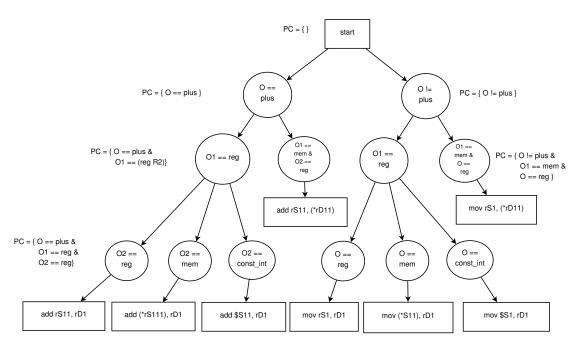

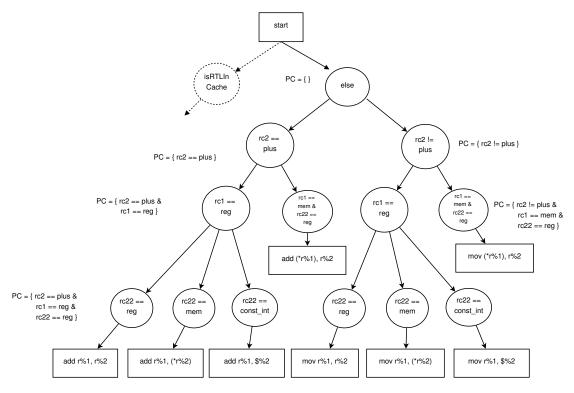

| 22 | Symbolic execution tree of the simple code generator                    | 78  |

| 23 | Modified OCaml code for the simple code generator                       | 80  |

| 24 | Concolic execution tree of the simple code generator                    | 81  |

| 25 | <b>Transformation logic for</b> $V_O = S(V_{I_1},,V_{I_n})$             | 87  |

| 26 | Transformation function for different program statements                |     |

| 27 | Source-to-source transformation of the simple code generator            | 93  |

| 28 | C Source code with use of rtx pointers and constraints generated for it | 96  |

| 29 | Sample C source code for concolic execution                             | 105 |

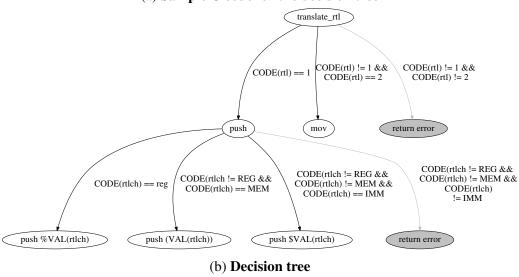

| 30 | Sample C code and its decision tree                                     | 110 |

| 112<br>115<br>nodel 116<br>AVR |

|--------------------------------|

| nodel 116                      |

|                                |

| AVR                            |

|                                |

| 121                            |

| 137                            |

| 141                            |

| ction                          |

| 143                            |

| rator                          |

| 150                            |

| code                           |

| 150                            |

| 153                            |

| 153                            |

| 154                            |

| nsla-                          |

| 160                            |

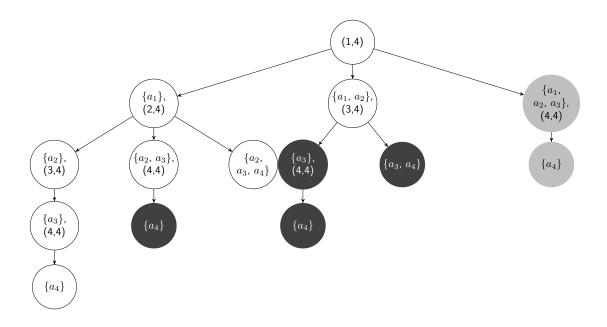

| $a_3, a_4$ } 164               |

| 167                            |

| 168                            |

| 171                            |

|                                |

#### Acknowledgements

I would like to take this opportunity to express my deepest appreciation and sincere gratitude to my advisor, Dr. R. Sekar, for his guidance, motivation, and support during my dissertation research. I would also like to sincerely thank him for providing financial support during my research and also for providing help in a number of personal issues. His suggestions, comments and insightful discussions have not only taught me how to be a good researcher, but have also enriched me for the rest of my life.

I would also like to thank my committee members, Dr. Mike Ferdman, Dr. Michalis Polychronakis, and Dr. Suresh Srinivas for dedicating their precious time to be a part of my committee. I am gracious for their constant support and constructive advice during my research.

I would also like to thank all the faculty and staff in the Department of Computer Science here at Stony Brook for their help during my research. I would especially like to thank Dr. Scott Stoller and Dr. Robert Johnson for giving me an opportunity to work with them during my Masters. Discussions with them were always very encouraging and enjoyable, and they helped me learn a lot. I would also like to thank Brian Tria for our conversations. Talking to him was always fun and much needed after intense work.

I would also like to thank all the people in Secure Systems Lab with whom I got a chance to work. Special thank goes to Alireza, Tung, Riccardo, Peter, Mingwei, Rui, Laszlo, Ashish, and Jeet. The time that we spent together solving problems, discussing research papers, or having fun will always be remembered. They all made my stay in Stony Brook very pleasurable. I would sincerely like to thank Tung and my close friend, Saurabh, who helped me a lot in a number of personal problems.

My research was financially supported in part by the National Science Foundation (NSF) grants CNS-0831298 and CNS-1319137, the Air Force Office of Scientific Research (AFOSR) grant FA9550-09-1-0539, and the Office of Naval Research (ONR) grant N000140710928. In addition, I would also like to thank the Department of Computer Science at Stony Brook for the fellowship for my research.

Last but not the least, I am so grateful to my parents, my brother Nilesh, and my wife Anuja for their love and support throughout the entire life. I am especially grateful to my father without whose encouragement I would not have started my PhD studies. I am also eternally grateful to my wife who sacrificed many things for my studies. Without her love and support, I would not have been able to complete my dissertation. Lastly, I would also like to thank my in-laws for encouraging and supporting me during my studies. Much of this work reflects the values that they all have installed in me. Without their love and support, I would not have been able to complete my dissertation. I am forever indebted to all of them. I dedicate my dissertation to all of them.

#### 1 Introduction

Binary analysis, translation, and instrumentation techniques have been phenomenal in solving a number of important problems in software engineering. Binary translation is the fundamental technique in dynamic malware analysis tools that are used by the anti-malware industry daily. Dynamic malware analysis requires malware execution in a controlled environment, so that effects of the execution are confined, and they do not spread into the underlying system. System emulators (such as QEMU [15]) and virtual machines (such as VMware [93]), which provide such controlled environment use binary translation as the underlying technology. In the past, binary translators have also been used to solve the problem of cross-platform portability and rapid deployment of software [22]. Binary instrumentation has been a popular technique with a number of important applications such as program debugging and program analysis. Dynamic binary instrumentation systems such as Pin [55], Valgrind [67], and DynamoRio [17] are popular among programmers for debugging and analyzing their programs.

A number of popular software systems that exist in the world today need to deal with the architecture-level (also called processor-level or low-level) details routinely. Technically, we can say that these systems need to model the *semantics* of target architectures that they want to support. Compilers are a good and well-known example of such systems. To be precise, many modern compilers support a number of target architectures, and their backends contain some architecture-specific components such as code generators. Binary analysis, translation, and instrumentation systems are another example of such software systems.

Modeling low-level architecture details in software is a very tedious task. Moreover, this task is made complicated by the fact that modern instruction sets are complex. For instance, Intel's instruction set manual (v52) [47] consists of around 2000 pages split across 3 volumes. To add to the complexity, new specialized instruction set extensions are proposed each year. To complicate the problem further, the systems described earlier usually rely on manual modeling of architecture semantics. Specifically, these systems often target architecture-neutrality — which is one of the desired properties of these systems — by translating low-level machine instructions from input binaries into higher-level intermediate representation (IR) instructions. Working at the IR level makes analysis and instrumentation architecture-neutral and hence applicable to all supported architectures. Unfortunately, most of these systems build the assembly-to-IR translators manually. Man-

ual development of assembly-to-IR translators translate to a number of limitations for these systems. First, considerable effort is needed to port these systems to new architectures, and as a result, most of these systems support a limited number of architectures. For instance, QEMU, a popular system emulator, supports 17 target architectures. Second, most of these systems do not support many instructions from the recently added instruction set extensions even for popular architectures such as x86. For instance, Valgrind<sup>1</sup>, one of the most popular dynamic binary instrumentation tools, still lacks support for several classes of x86 instruction sets such as AVX, FMA4, and SSE4.1, even after being in development for 10 years.

#### 1.1 Overview of Approaches and Dissertation Organization

In this dissertation, we address the problem of modeling the semantics of modern and complex architectures by developing two novel *architecture-neutral* approaches for *automatic* semantics extraction. Our approaches start with the goal of eliminating manual modeling effort completely. When this objective cannot be achieved, then they answer the question of how much manual effort can be reduced.

Automatic extraction of instruction set semantics is a very challenging problem given that the common approach for extraction is to rely on actual hardware. Tendency to rely on hardware stems from (a) the desire make the models correct and accurate, and (b) the fact that hardware is the best source of accurate and correct semantic information (Though hardware manuals may also serve as a good source of correct and accurate information, generally, it is easier to automate the extraction process with hardware than the manuals.) Unfortunately, synthesizing instruction semantics using hardware demands execution of every machine instruction under every possible machine state, which requires one to explore the huge input space of every target instruction. This challenge has prevented the development of systems for automatic semantics extraction for complex architectures such as the x86. Nonetheless, research works have attempted to address this problem by using manual effort to make traversal of the input space practically feasible. We will talk about these research efforts in Section 2.

Given that automatic extraction by using hardware is infeasible without manual effort, in this dissertation, we do not use hardware. Instead, we hypothesize that we can use modern compilers for such extraction. Modern compilers such as GCC [3] and LLVM [8]

<sup>&</sup>lt;sup>1</sup>v3.10.0, 2014

already contain detailed knowledge about the semantics of many architectures. Specifically, architecture-set specifications used by the code generators of these compilers contain a mapping between target assembly instructions and their semantics in IR. These mapping tables are used by the code generators to translate IR instructions into target assembly instructions. We hypothesize that the knowledge encoded in compilers can be extracted automatically and develop a white-box and a black-box approach for the extraction. We chose compilers for such extraction because they support a number of architectures, and their extensive testing minimizes the chances of semantic modeling errors in them. For instance, GCC and LLVM both support more than 40 target architectures — considerably more than those supported by QEMU. Moreover, being actively developed, these compilers are tested by large test suites.

One approach to extract instruction-set semantics from code generators is to use their architecture specifications directly. As we will see in Section 2, the existing approaches for writing these specifications are such that their direct use is complicated. The problem is that the compilers encode a lot of architecture-specific knowledge in their source code in addition to their specifications. Since direct use of specifications is complicated, a feasible approach would be to use the code generators in their common usage scenario of compiling source programs. Our black-box approach, called LISC (Section 3), relies on the observation that, while compiling source programs, modern compilers can output IR-to-assembly mapping rules used by their code generators. IR instructions in these rules specify the semantics of the corresponding assembly instructions. LISC *learns* the instruction-set semantic model encoded in the code generators by referring to their compilation logs.

LISC faces two interesting challenges in using compilation logs for model extraction. First, modern compilers may not support all of the target assembly instructions. For example privileged instructions are generally not supported by the compilers. Moreover, privileged instructions may not be the only instructions that are not supported. Because of this, models extracted from compilers will be incomplete. Second, even if compilers supported all of the target assembly instructions, the extraction process would need to ensure that all of the code generator mapping pairs are covered. It is likely that, for a typical compilation, a code generator may not refer to all of the target assembly instructions. For instance, GCC does not use instructions from most of the advanced x86 instruction set extensions unless a programmer directs otherwise. Both of these coverage challenges need to be addressed, because the extracted semantic models *should* contain all of the target assembly instructions. Unsupported instructions may be covered by using other compilers for extraction,

but achieving complete coverage of complex software such as code generators has been one of the challenging problems in software testing. We will address these challenges in Section 3.

As an alternative to LISC, we develop a white-box approach, called EISSEC, to extract semantic model through symbolic execution of the code generators. Symbolic execution is a technique in the software testing domain to improve program coverage. Unfortunately, it suffers from the "explosion" problem, where the exponentially increasing number of program paths make symbolic execution of complex programs infeasible. Recent research [19, 24, 21] addresses this challenge, but, unfortunately, we have not come across cases of symbolic execution being applied to complex source programs such as code generators. In EISSEC, we try to assess how we can scale symbolic execution to code generators. We believe that the solutions which we propose in EISSEC will make important contributions towards improving applicability of symbolic execution to complex programs. We will describe EISSEC in Section 4.

Correctness and completeness are the two desired properties of the models extracted using LISC and EISSEC. This is because the correct results from the applications built using these models depend upon the correctness of these models. Completeness, on the other hand, is a nice-to-have but not necessary property because its absence results in missing assembly instructions in the models. We develop two approaches to ensure correctness and completeness of the models. First, we empirically evaluate these properties in Section 3. Second, we develop an approach, called ArCheck, to check the correctness of extracted models. ArCheck formalizes the correctness checking problem as the problem of checking the semantic equivalence of every assembly and its corresponding IR instruction from the extracted models. Since the semantics of an assembly instruction can only be obtained by concretely evaluating that instruction (unless we want to manually model the semantics, which we want to avoid), approaches such as symbolic equivalence checking (a fundamental approach used in software verification) cannot be used for our purpose. Our semantic equivalence test thus involves comparison of IR and assembly semantics obtained by their concrete evaluation. But for concrete evaluation, instead of employing a random testing approach, ArCheck develops a systematic coverage testing strategy to produce test cases and to maximize confidence in the correctness of results. Solutions proposed by ArCheck make two important contributions to the compiler testing problem. First, ArCheck solves the problem of checking the correctness of code generators (for which, to the best of our knowledge, no verification work exists). Second, it provides a practical approach that can

be applied to the code generator of any compiler. We will describe ArCheck in Section 5.

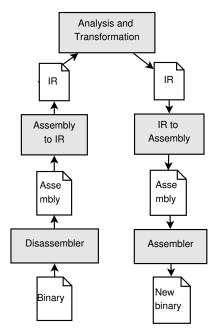

Once the extracted semantic models are checked for correctness, we demonstrate their applicability to developing assembly-to-IR translators. By building these translators automatically, we demonstrate that these systems can quickly support new architectures as well as new instructions from already supported architectures.

This dissertation is organized as follows. Section 2 discusses various approaches for automatic synthesis of instruction-set semantics and compares them with our proposed approach. Section 2.3.1 provides background on modern compilers relevant to this dissertation. Section 3 and Section 4 discuss our approaches for automatic instruction-set semantics extraction. Section 5 discusses our approach to check the correctness of extracted semantic models and code generators. Section 6 discusses an application of extracted models in building assembly-to-IR translators. Lastly, Section 7 concludes this dissertation and discusses future extensions of this work.

#### 1.2 High-Level Overview of Contributions

One of the important contributions of this dissertation is to approach the problem of *automatic* instruction-set semantic extraction by developing two novel *architecture-neutral* approaches. The solutions proposed in this dissertation have a number of important applications such as building binary analysis, instrumentation and translation systems, code generators, and CPU emulators. Furthermore, since these systems are expected to model the low-level semantics faithfully, the extracted semantic models can be used to test these systems and check if this expectation is valid.

In addition to developing approaches for automatic extraction of semantics, in this dissertation, we demonstrate two applications of the extracted models. In the first application, we use the models to *check the correctness of compiler code generators*. Although compilers are tested extensively, they are known to contain bugs. We observed that code generators of modern compilers contained semantic modeling bugs. Given the critical role played by the compilers, it is necessary that such modeling bugs are caught in the development. Our solution thus contributes to the important problem of testing compilers.

In the second application, we use the extracted models to *build assembly-to-IR translators used by the architecture-neutral binary analysis, translation and instrumentation systems automatically*. A common approach to build assembly-to-IR translators is to build architecture-neutral translators and drive them using manually-written target descriptions.

For such systems, automatically extracted semantic models can be used to replace manually-written architecture specifications. Our solution helps in improving the effectiveness of these systems by allowing them to target more architectures and also supporting existing architectures completely.

Although we described the problem of manually-developing assembly-to-IR translators by using examples of existing systems such as Valgrind and QEMU, this dissertation does not consider the problem of building a complete end-to-end binary translation, instrumentation and analysis system. It instead demonstrates the applicability of the extracted models in building the assembly-to-IR translators (which are one of the building blocks of these systems). Moreover, it is not within the scope of this dissertation to address the limitations of a specific system (e.g., Valgrind). By translating compiler's IR to the specific tool's IR, one may use the assembly-to-IR translators built using our models to support a specific system.

## 2 OVERVIEW OF APPROACHES FOR AUTOMATIC SYN-THESIS OF INSTRUCTION SET SEMANTICS

In this section, we will discuss various approaches to extract instruction set semantics models automatically. We will then discuss limitations of these approaches before moving on to our approach. But before we discuss these approaches, we need to specify precisely what is the level of detail that we want in the extracted semantics.

#### 2.1 Level of Abstractions Required In the Extracted Semantics

Semantics of an instruction can be specified and modeled at different levels of abstraction. Too much detailed semantics may not be desirable to applications which actually expect slightly abstracted semantics. Thus, it is important to establish the level of details that we want the extracted semantics to confirm. The desired level of details of the extracted semantics is actually dictated by the applications which will consume the semantic models at that level. Thus to establish the level of abstractions, we need to understand the kind of applications that will be consumers of our extracted models. In this dissertation, we target applications which work at the level of binaries but which want to target multiple architectures without much porting efforts. An example of such application could be a binary analysis framework. Typically, such a framework operates on binaries, but the kind of analyses performed are mostly architecture-neutral. So such frameworks operate on architecture-neutral representation of the input binary. Such a representation essentially makes the framework applicable to binaries from any architecture. Our extracted model will be used by such a framework to translate input binary into an architecture-neutral representation. Let us now see what level of detail these applications expect from the architecture-neutral representation.

Semantics of an assembly instruction can be represented at various levels of detail. For instance, semantics of addl %eax, %ebx could be described in the following ways:

**D1**: add the value of eax to ebx and store the result in ebx, or

**D2**: one could simply enumerate possible values of eax and ebx, and could specify the outcome of the execution of the instruction (treating instruction semantics as a function between possible input values and output values), or

**D3**: add the value in first input operand with the value in second input operand, and store the result in the output operand.

In this dissertation, we are interested in representing the semantics at the level of detail captured in the first option. In fact, that is the level of details that the applications like binary analysis are interested in. Semantics specified in the second option are too detailed, and a binary analysis system may not really process such level of details<sup>2</sup>. The third option, on the other hand, captures the semantics at a very abstract level, and thus is not desirable for binary analysis systems either. Various approaches for semantics extraction that we will describe now extract the semantics at different levels. In addition to this mismatch, they have some limitations which make them unsuitable for our purposes.

**Notations and terms.** Before we describe our approaches, we define the notations and terms which will be used in the rest of the dissertation.

We use notation A to represent an assembly instruction. An assembly instruction is abstract when the operands of the assembly instruction are abstract. For instance, "add %1, %2" is an abstract assembly instruction for the x86 add instruction. A concrete assembly instruction, on the other hand, has concrete operands. For instance, "add %eax, %ebx" is a concrete x86 add instruction. We use  $A_c$  to represent a concrete assembly instruction, and  $A_a$  to represent an abstract assembly instruction. Notation A represents both abstract and concrete assembly instruction.

We use notation  $\sigma$  to represent the semantics of an instruction. The semantics of concrete assembly instructions can be defined concretely in terms of the processor state changes caused by their execution. The semantics of abstract assembly instructions, on the other hand, cannot be defined concretely. For instance, the semantics of x86 add instruction as it is given in the Intel manual is shown in Figure 1.

We use notation R to represent a mapping between an assembly instruction A and its semantics  $\sigma$ . We represent R as  $R = \langle A, \sigma \rangle$ .

We use notation  $\mathscr{M}$  to represent semantic model. A semantic model is a collection of mapping rules between all the assembly instructions for some target architecture and their semantics. Thus, a semantic model can be formally defined as  $\mathscr{M} = \{\langle A_i, \sigma_i \rangle\} \forall i \in \mathscr{T}$ , where  $\mathscr{T}$  is a target architecture.

<sup>&</sup>lt;sup>2</sup>This is the case because systems which perform binary analysis operate on IR instructions which contain operators like plus to model semantics of addition. So they do not need to know what is the meaning of addition.

#### **Description:**

Adds the destination operand (first operand) and the source operand (second operand) and then stores the result in the destination operand. The destination operand can be a register or a memory location; the source operand can be an immediate, a register, or a memory location. (However, two memory operands cannot be used in one instruction.) When an immediate value is used as an operand, it is sign-extended to the length of the destination operand format.

The ADD instruction performs integer addition. It evaluates the result for both signed and unsigned integer operands and sets the OF and CF flags to indicate a carry (overflow) in the signed or unsigned result, respectively. The SF flag indicates the sign of the signed result.

This instruction can be used with a LOCK prefix to allow the instruction to be executed atomically. In 64-bit mode, the instruction's default operation size is 32 bits. Using a REX prefix in the form of REX.R permits access to additional registers (R8-R15). Using a REX a REX prefix in the form of REX.W promotes operation to 64 bits. See the summary chart at the beginning of this section for encoding data and limits.

#### **Operation:**

$DEST \leftarrow DEST + SRC;$

#### Flags Affected:

The OF, SF, ZF, AF, CF, and PF flags are set according to the result.

Figure 1: Semantics of x86 add instruction taken from Intel manual

#### 2.2 Possible Approaches

The high-level idea behind these approaches is to rely on authentic sources of instruction semantics. There exist two sources of such information: manuals supplied by the processor vendors (e.g., Intel's instruction set manual [5]), and the CPU itself. So these approaches rely on either of them, with tendency to prefer CPU over the manuals. Recently, there have been approaches which rely on "software" form of a CPU. By "software" form of a CPU, we mean some software which mimics the functionality of an actual CPU (e.g., CPU emulators). "Software" CPU is used because actual CPU imposes some restriction on its usage. We will see what these restrictions are, and also other approaches now.

#### 2.2.1 Extraction from instruction-set manuals

Vendor-supplied instruction-set manuals are one of the authentic sources of information about instruction semantics. In fact, supplying such information is one of the main purposes of such manuals. So it is perfectly logical to think of such manuals as a first stop for the instruction semantics. We saw an example of how these manuals contain instruction semantics by describing the entry found for add1 x86 instruction in Intel manual. Most manuals contain pseudo code for instruction semantics in addition to English description. Unfortunately, we believe that extracting semantics from such pseudo code is not a trivial task. More important issue is that such an approach will not be architecture-neutral as we need to tailor-made such approach for each and every architecture. Given these limitations, we decided not to pursue such approach at all.

#### 2.2.2 Extraction from the hardware

Given that semantics extraction approach based on CPU can be systematically applied to any other CPU, this is generally a preferred approach over use of instruction-set manuals. Such approaches rely on the observation that the hardware CPU can be treated as a hardware oracle to obtain instruction semantics. Intuitively, to obtain instruction semantics from the CPU, one can simply execute that instruction on the CPU, and compare the preand post-state of the CPU to learn the semantics. Although, this approach is simple and intuitive, unfortunately, it is infeasible. Specifically, in order to learn the semantics of some instruction completely, one needs to execute that instruction with all possible input values (if not under various possible operand combinations additionally) and under various possible pre-states of the CPU. Moreover, this option captures the semantics at the level **D2**, which makes it unsuitable for the applications that we are interested in.

To give an idea of the infeasibility, let us consider an example of x86 add instruction. x86 add instruction takes two operands, one of which being a register or memory location, and the other being either a register, a memory location, or an immediate. The total number of possible operand combinations and their values for add are  $(8+2^{32})*(6+2^{32}+2^{32})$  — 8 for the number general-purpose registers on x86,  $2^{32}$  for the number of memory locations that can appear in the instruction (considering 4GB virtual address space), and  $2^{32}$  for the total number of 32-bit immediates that can appear. The idea here is that if we execute add instruction on x86 processor with these many operand combinations in all possible states of the processor, then we can essentially learn the complete semantics of add instruction.

It is easy to see that the number of operand combinations needed for exhaustive enumeration approach are far too many to be feasible in practice.

#### 2.2.3 Extraction by exhaustive testing of CPU

The drawback of exhaustive enumeration is that it needs to cover the huge space of possible inputs of an architecture instruction in order to obtain its semantics. A natural question to ask then is: can we reduce this space somehow? Some research efforts such as [41] try to answer this question by relying on manual efforts. Specifically, they manually define instruction semantics templates in such a way that they are (1) generic enough that few such templates suffice for the whole instruction set, (2) but at the same time specific enough that they reduce the input space considerably. Work described in [41] uses 6 such templates to model semantics of 580 x86 instructions (8-bit, 16-bit and 32-bit). For this work, semantics of an instruction can be thought of as a function which maps the inputs of the instruction to its outputs. Instead of searching the function implemented by an architecture instruction in the huge space of possible functions, they restrict their search to the manually-defined function templates. The contribution of this work is an efficient approach which makes the function synthesis from I/O samples of 32-bit instructions possible. In order to discriminate multiple functions which may satisfy a subset of all possible I/O samples of an instruction, they develop a notion of discriminating inputs (called as smart inputs).

Although their approach is effective in synthesizing functions of 580 x86 instructions, it suffers from following limitations. First of all, the level of details captured in the extracted semantics is still at level **D2** which makes this approach unsuitable for our purpose. While their goal is to encode the extracted semantics in symbolic formulas which can be used by symbolic execution systems, the applications that we are interested in do not look for such level of details. Second, we believe that designing the templates and the smart inputs demands considerable understanding of the target assembly instructions. In their work, they had to study instruction-set manuals and had to manually develop the templates and the inputs. It is unclear how easy/difficult it is to come up with these templates and inputs for complex instruction set extensions such as SSE and AVX for x86. Moreover, it is unclear how much time does it take for them to support a new architecture. As we will see later in this dissertation, as compared to this approach, our approaches require very minimal (if not none) architecture knowledge to extract their semantics model. Third, designing templates to model semantics of 64-bit instructions, floating points and advanced floating point instructions is very complex and challenging (They also admit about this

complexity.) The approaches that we propose in this dissertation are not limited by the size of instruction's input space. Thus, our approaches can easily scale to complex instruction sets.

#### 2.2.4 Extraction by symbolic execution of CPU specification

Symbolic execution [49] is a very powerful technique proposed in the literature to exactly solve the kind of problems for which exhaustive enumeration is practically infeasible. It exploits the fact that most of the program inputs follow same program path. Thus, instead of considering each of such inputs separately, one can simply put them in one partition of the input space, and consider only one representative input for the whole partition. By defining few partitions to cover complete input space and by considering only one input per partition, symbolic execution can drastically reduce the number of inputs that we need to consider to obtain complete semantics. Using symbolic execution, it is thus possible to avoid exhaustive enumeration and extract instruction semantics. We will see what are its limitations when applied to the semantics extraction problem.

To extract a complete and accurate instruction set semantics model, one can simply perform symbolic execution of CPU hardware. Theoretically, this idea works fine, but, practically, it is infeasible for the following reasons. First, to perform symbolic execution of a program, one needs access to its source code or binary. In other words, the program must be available in a software form; unfortunately, CPU is hardware. Second, symbolic execution involves setting the program inputs symbolically rather than concretely. Unfortunately, CPU requires concrete inputs instead of symbolic<sup>3</sup>. Symbolic execution of CPU hardware is thus practically infeasible.

Symbolic execution of a publicly-available high-fidelity CPU emulator. A practically feasible idea, which can achieve the same effect as that of symbolic execution of CPU hardware, is to perform symbolic execution of a publicly-available high-fidelity CPU emulator. After all, CPU emulators are expected to faithfully and accurately emulate instruction semantics of the underlying CPU. PokeEmu [57] proposes such idea, and demonstrates how can one use popular emulators such as Bochs [85] for such purpose. Although, such ap-

<sup>&</sup>lt;sup>3</sup>It is most likely true that CPU manufacturers have software forms of the CPU which are used to validate functionality of the CPU before it is manufactured. As a result, it is conceivable that one could perform symbolic execution of such software forms to perform symbolic execution of the CPU. But, unfortunately, such software forms are always intellectual properties of the respective manufacturers and are not available to general public.

proach can be used to extract level of semantics suitable for our purpose, unfortunately, such an approach suffers from the limitations of the emulators. First and foremost, most of the emulators support a very limited number of architectures. An approach based on such emulators would naturally be applicable to only few architectures. Second, even though high-fidelity emulators exist, they are also shown to contain a number of bugs [57]. So the accuracy of the semantics models extracted from such emulators is an questionable.

#### 2.3 Our Approach

In the last section, we saw how can one use instruction semantics manuals, hardware CPU and software CPU for semantics extraction. We also discussed the limitations of each of them in the semantics extraction process. Given that discussion, we will first specify a number of requirements from the semantics information source that we want to use for extraction. Such requirements can make the comparative study of our approach easy. Then, we will see what our approach is. The requirements from the semantics information source are as below.

- **R1**: Accurate and faithful representation of CPU semantics. This is the most basic and important requirement of the system which we want to use to extract instruction set semantics.

- **R2**: Completeness: representation of semantics for all CPU instructions. It is desirable that the system that we want to use for extraction supports all the instructions from the target architecture. A frequent addition of a number of instruction set extensions to modern architectures underlines the importance of this requirement.

- **R3**: Support for diverse architectures. Since our objective is to extract instruction set semantics automatically, we would like to apply the solution to as many architectures as we can. This requirement also ensures that the applications built using the extracted semantics will be applicable to many architectures. For instance, system emulators will be able to support architectures that are not supported generally. This requirement thus translates into portability of the applications built using extracted instruction set semantics.

Given those requirements above, we found that the high-fidelity CPU emulators satisfy most of the requirements except **R3**. Lack of support for diverse architectures limits the

applicability of semantics extraction to very few architectures, thus limiting the overall effectiveness of applications built using extracted semantics models. Modern compilers, such as GCC [3] and LLVM [8], on the other hand, satisfy all the requirements in a better manner than the emulators. Specifically, modern compilers offer following advantages:

- Modern compilers support a number of architectures (requirement **R3**) many more than those supported by most of the commonly used emulators.

- They are tested extensively through rigorous test suites, thus minimizing the chances of bugs in them (requirement **R1**).

- These compilers are usually very quick to provide support to newly added instruction set extensions (requirement **R2**).

- Infrastructure developed by these compilers such as optimization passes can potentially be reused in other architecture-independent systems. For instance, a quick way to build a retargetable binary translator using extracted instruction set semantics could be to reuse existing compiler infrastructure such as optimizer, register allocator, instruction scheduler, directly. As a result, we will not need to build the components of the binary translator from scratch. Such an approach to build a binary translator has a number of advantages.

- The process of developing a translator from assembly-to-IR would be greatly simplified because the mapping from assembly-to-IR can be viewed as an inverse of the mapping from IR-to-assembly.

- The binary translator is inherently retargetable as it inherits retargetability from the compiler. When the compiler is retargeted to a new platform, new backend can be used to facilitate retargeting of the translator.

- As the binary translator and the compiler share same IR, we can simply reuse compiler optimizations and other passes (such as register allocation, instruction selection). Binary instrumentation frameworks, such as Valgrind, builds such components manually from scratch.

- Compiler IRs are well designed. Ability of these compilers to compile source programs written in a number of high-level programming languages and generate binaries for a number of platforms proves that their IRs are comprehensive

enough to represent features from all languages and architectures. So, instead of designing a new IR, the binary translator can simply rely on compiler IR for its purpose.

Given the advantages offered by modern compilers, we decided to use GCC compiler for extracting instruction set semantics. Even though we have used GCC for our research purpose, the ideas and techniques discussed later are equally applicable to LLVM. To understand how these compilers offer a better solution, we need to discuss some of their internal details. A reader familiar with such details can skip this section.

#### 2.3.1 Background on code generation in modern compilers

Structure of a Modern Compiler. Compiler researchers have long worked to develop architecture-independent code generators [33, 32]. These code generators start with an intermediate representation (IR), and emit assembly code. Ideally, the code generator is driven by an instruction set specification called a *machine description* (MD). This MD may take the form of a set of rules, each mapping a snippet of IR into an assembly instruction. Such a rule-based approach can generate inefficient code since it fails to take into account the context in which translation takes place, e.g., it may generate many redundant loads and stores. These inefficiencies can be mitigated by performing several optimizing transformations on the IR, and by driving instruction selection using some cost metrics. Such an approach moves the complexity to IR optimization passes that are shared across different architectures, while simplifying architecture-specific MDs.

Code generators in contemporary compilers such as GCC and LLVM follow this general outline. Due to GCC's maturity and support for many instruction sets, we chose GCC in our implementation. But an important feature of our approach is that it does not depend on GCC specifics, and hence can be applied to other retargetable compiler backends.

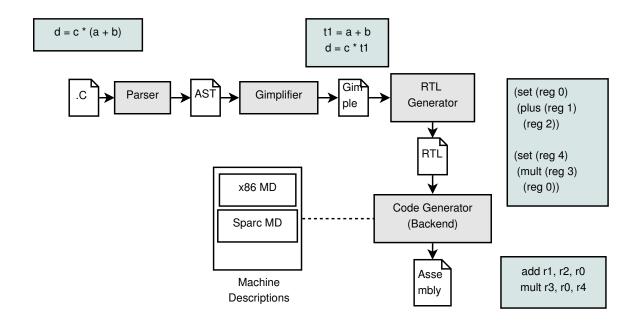

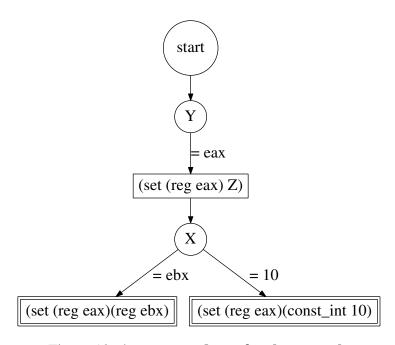

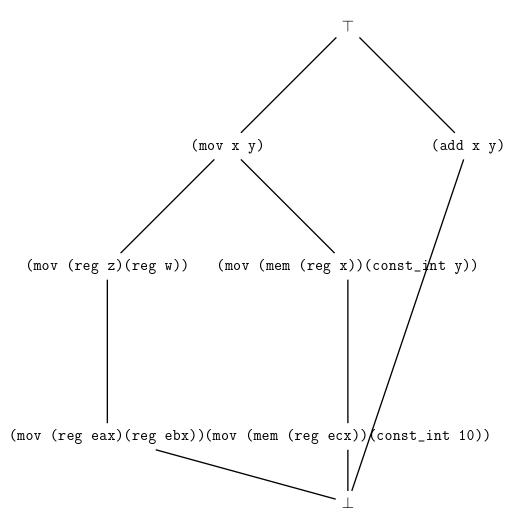

Figure 2 shows the key steps in the compilation of a high-level language (a C-program, in this case) by GCC into machine code. These steps are illustrated using a simple example: an assignment statement in C that eventually gets translated into two assembly instructions. The front-end of the compiler translates from different source languages to a high-level intermediate form called GIMPLE. Several optimizations are performed on GIMPLE and then it is translated into GCC's IR, which is called RTL (register transfer language). (These details of the front-end are not relevant for the purposes of this report, but are shown here simply to provide more context.) Then the back-end uses MDs to translate RTL snippets

Figure 2: Key steps in GCC's translation of a source program

into assembly. As noted earlier, the back-end in GCC incorporates over 40 optimization passes over RTL, and also performs related tasks such as register allocation.

**Machine Descriptions.** A machine description (MD) specifies all aspects of a target machine architecture, including the number of registers, endianness, parameter passing conventions, and a mapping from RTL snippets to equivalent assembly instruction(s). This mapping is the most important part of an MD, and poses most of the interesting research challenges, so we focus on it below.

As mentioned earlier, code generation is a pattern-driven process: it is specified using rules of the form  $RPat \longrightarrow Asm$  where RPat represents an RTL pattern, and Asm represents equivalent assembly code. Typically, Asm is a single instruction, but there are occasional cases where it may contain several instructions. An RTL pattern includes an RTL snippet, together with conditions on when the rule can be applied. The code generator starts with RTL code generated by the compiler front-end. MD rules are matched with snippets of this RTL, and any matching snippet is replaced by the corresponding assembly code. This rewriting process is continued until no more RTL is left. The order in which MD rules are tried may be governed by a cost metric associated with a rule. In addition, the code

```

(set (match_operand: 0 "reg_opnd" "a")

(div (match_operand: 1 "reg_opnd" "0")

(match_operand: 2 "nonimm_opnd" "qm")))

(clobber (reg:FLAGS_REG))

→ "div %2"

```

Figure 3: An MD entry for x86 div instruction

generator may modify RTL under translation in order to find a match, e.g., moving a value from one register (or memory) to another register in order to satisfy conditions specified in RTL patterns.

An example MD rule for the x86 instruction set is shown in Figure 3. To reduce clutter, we have abstracted away some details that are not critical for the purpose of explaining our approach.

This instruction corresponds to x86 divide instruction. The RTL pattern specifies the semantics of this instruction in RTL, namely, that it sets operand 0 to be the result of dividing operand 1 by operand 2. It also states that the flag registers are modified. Since the compiler does not require the flag values after a divide operation, it is simpler to state that flags are modified, instead of detailing the exact change. Nonetheless, when an RTL instruction checks a particular bit of flag values, its preceding instruction sets that particular bit precisely. This pattern is applicable when input RTL matches the match\_operand conditions, which are broken into a *predicate* and a *constraint*. It is not necessary for our discussion to understand the full semantics of predicates and constraints, but we will explain one of them for illustration. The predicate on operand 1 states that the operand should correspond to a register, while the constraint indicates that operand 1 should be the same as operand 0. Moreover, the constraint on operand 0 states that it should be the EAX register. Thus it is quite easy to see that the above example captures the semantics of x86 div instruction correctly.

Given the above structure of MD rules, one might simply think that the MD files already represent extracted instruction set semantics. Consequently, one can simply refer to MD files for the extracted semantics and can avoid synthesizing the instruction set semantics altogether. For instance, semantics of div instruction can be learned from the RTL contained in the rule. Unfortunately, this simplistic approach runs into many difficulties:

• Some aspects of RTL corresponding to an assembly instruction are defined by the

virtue of predicates and constraints, e.g., the condition that the destination operand is the EAX register, or that the two operands of RTL instruction should be identical. While this could potentially be handled by incorporating the semantics of constraints and predicates into a reversing algorithm, such an approach suffers from the drawback that the semantics of many of the predicates and constraints differ across architectures.

• For many rules, the *Asm* part does not directly specify assembly code, but is instead a snippet of C-code that, when executed, will generate a string representation of assembly code. Clearly, it is difficult to statically determine the string(s) that may be generated by a snippet of C-code.

To overcome above problems, we develop approaches that avoid referring the specifics of MD rules. Such approaches eliminate dependencies on architecture specifics in implementation. More importantly, such approaches can be general, and applicable to compilers other than GCC that may use more programmatic MD rules.

Even though direct use of MD files is complex task, it is a very important observation to note that the MD files already contain extracted instruction set semantics. We put this observation along with few other important observations about modern compilers to tackle the problem of automatically extracting instruction set semantics.

#### 2.3.2 Possible challenges for our approaches

Use of compilers for model extraction can lead to some interesting challenges because of the way compilers operate. Specifically, semantics models extracted using code generators may be incomplete and/or incorrect also. Incompleteness of the models comes from two different sources.

First source of incompleteness relates to a possibility that the compilers may not support all of the target architecture instructions. Consequently, such unsupported instructions would also be missing from the extracted models. We expect this to be a case for newly added architecture instructions. Nonetheless, we expect such number of unsupported instructions to be small — actively-developed modern compilers such as GCC and LLVM are generally quick to support newly added instructions (including those from advanced instruction sets).

Second source of incompleteness relates to a common observation that the compilers may not model semantics of every instruction in all the details. Unfortunately, miss-

ing details would also be lacking in the models extracted by our approaches. For instance, GCC's machine description may not model *how* CPU flags are modified as a result of some operation, but it may just model the fact that the flags are modified. For instance, GCC's MD entry for x86's div instruction discussed in the Section 2.3.1 contains (clobber: (reg: FLAGS\_REG)) instead of detailing out *which* bits of EFLAGS are modified and *how* they are modified. Such loose semantics modeling is sound for compilers because most of the compiler static analyses may only be interested to know if a particular instruction modifies flags. That is why compilers may capture over-approximation of the instruction semantics. Compilers may not always capture over-approximate semantics all the times — whenever required they may as well capture precise semantics. For instance, in x86, when the div instruction is followed by a conditional jump instruction, IR for the div instruction will precisely update the bits of EFLAGS that are needed by the jump instruction.

Incompleteness of the extracted models can be addressed in multiple ways. First, we can choose a compiler that uses most (if not all) of the target machine instructions. Moreover, the models extracted by our approaches can be augmented with manual specifications — by cutting down manual specifications to a small minority of instructions, we can achieve significant savings over existing approaches. On the other hand, manual specification of the details may not be needed as most of the applications of the extracted models, such as binary analysis and instrumentation systems, do not need much level of details. Nonetheless, in those rare cases where additional precision is desired, the models extracted by our approach can be manually augmented with the missing details.

Incorrectness of the models stems from the fact that even though modern compilers are tested rigorously, given the limitations of software testing, they are not completely bug-free. Consequently, the semantics obtained from GCC's code generator may have some correctness issues. We will talk about different types of possible correctness issues in the appropriate section of this dissertation. We will also talk about how to rectify these issues as and when relevant. But before getting into challenges, we will talk about our overall approach now.

#### 2.3.3 Approach details

Our overall approach to synthesize instruction set semantics automatically using GCC consists of two phases.

• Phase 1: extract the instruction set semantics using GCC's code generator.

For this phase, we have developed two approaches, namely LISC and EISSEC, to extract instruction set semantics from GCC's code generator. Both these approaches are discussed in depth in the Section 3 and Section 4. EISSEC uses symbolic execution of code generator to extract the semantics model. So at a high-level, this approach is similar to symbolic execution of CPU emulator performed by PokeEmu. LISC, on the other hand, employs a completely different technique than EISSEC. Specifically, it treats code generator as a black-box and *learns* the semantic model from it. Since code generators generate semantically-equivalent assembly instruction(s) for the input IR instruction(s), the outcome of this phase is a mapping between semantically equivalent IR-to-assembly pairs for all compiler-supported target assembly instructions. Such a mapping precisely defines the instruction set semantics model followed by the code generator.

#### • Phase 2: Checking correctness of extracted instruction set semantics.

Even though we are able to extract instruction set semantics from code generators automatically, there is one important challenge that we need to tackle before such semantics can be used in some applications. Specifically, to address the correctness issues, we have developed an approach named ArCheck (Section 5). Since we assume that the IR to assembly instruction pairs present in the model should be semantically equivalent (because compilers are expected to preserve semantic equivalence during compilation), we enforce semantic equivalence test as the correctness check. The outcome of this phase is a new model such that most of the correctness issues from the input model are resolved.

#### 2.4 Summary

In this section, we described various approaches for automatic extraction of instructionset semantics. We also described various levels of semantic details that one can extract, and how and why they may not be relevant for our purpose in this dissertation. We then described the advantages offered by modern compilers, and why we believe that they are appropriate for extracting instruction-set semantics. Finally, we described our overall approach of semantic extraction using code generators of modern compilers. In the next couple of sections, we will see our semantic extraction approaches in detail.

## 3 LISC: LEARNING INSTRUCTION SEMANTICS FROM CODE GENERATORS

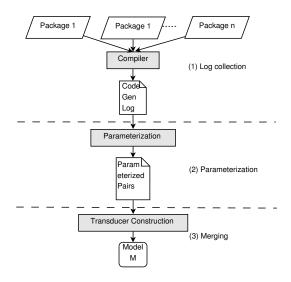

As we saw in the last section, the direct use of architecture specifications for extracting instruction set semantics model is hard. Moreover, it is undesirable since it would tie the approach of model extraction to a specific compiler. A much better approach for model extraction is to treat compilers (and code generators) as a black-box and to decouple from the specifics of their architecture specifications. Fortunately, the common practice of dumping the inputs and outputs of intermediate stages of modern compilers makes such an approach feasible. To be precise, code generators of modern compilers provide options to log IR instructions and their corresponding assembly instructions generated by the code generators during compilation of source programs. As a result, it seems possible to extract semantics models used by the code generators by referring to their logs. Our approach for semantics model extraction, called LISC (stands for Learning Instruction Semantics from Code generators), is exactly based on these observations.

A sample log obtained from GCC's x86 code generator during the compilation of a typical C code (for fibonacci series) is shown in Figure 4. The log contains x86 assembly instructions and their corresponding RTLs (GCC's IR) instruction. (It is not necessary at this stage to understand details of RTL instructions. So we will not discuss them here.)

```

\label{eq:continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous

```

| No | Assembly        | RTL instruction                                               |

|----|-----------------|---------------------------------------------------------------|

|    |                 | (set (mem:SI                                                  |

| 1  | pushl %ebp      | $(pre\_dec:SI (reg:SI esp)))$                                 |

|    |                 | $(\mathtt{reg}:\mathtt{SI}\;\mathtt{ebp})))$                  |

| 2  | movl %esp, %ebp | <pre>(set (reg:SI ebp) (reg:SI esp))</pre>                    |

|    |                 | (set (mem:SI                                                  |

| 3  | pushl %ebx      | $(pre\_dec:SI (reg:SI esp)))$                                 |

|    |                 | $(\mathtt{reg}:\mathtt{SI}\;\mathtt{ebx})))$                  |

|    |                 | (parallel [(set (reg:SI esp)                                  |

| 4  | subl \$20,%esp  | (plus (reg:SI esp)                                            |

|    |                 | $(\mathtt{const\_int}\ -20)))$                                |

|    |                 | $({\tt clobber}\;({\tt reg}{\tt :}{\tt CC}\;{\tt eflags}))])$ |

|    |                 | (set (pc)(if_then_else                                        |